一、并行ADC

1.ADC簡介

背景知識:模數轉換器(Analog to digital Converter,簡稱ADC)是模擬與數字世界的接口,為了適應計算機、通訊、多媒體技術的飛速發展以及高新技術領域的數字化進程的不斷加快,ADC正朝著低功耗、高速、高分辨率方向發展。目前市場化的ADC有很多種類型。

近年來,我國在有限的工藝水平條件下積極開展了對ADC的研究,并取得了令人鼓舞的成果,但是與國際水平相比尚有差距,電路結構設計也略顯單調,折疊式、流水線型、E一△型結構鮮見報道。統計資料表明,8-12位精度范圍的高速A/D轉換器是應用最廣泛、需求最迫切的品種,因此研制出我國具有自主知識產權的高速高精度、高速、低功耗的ADC具有十分重要的意義。目前市場化的ADC有多種結構,如并行(Flash,或稱Parallel)A DC,逐次逼近型ADC、積分型ADC,壓頻變換型ADC以及流水線型ADC和Delta-Sigma型ADC等,其中后兩種ADC是新發展起來的,這些ADC各有各的特點,根據不同的應用場合,選用的ADC的結構也是不同的。

2.基本原理

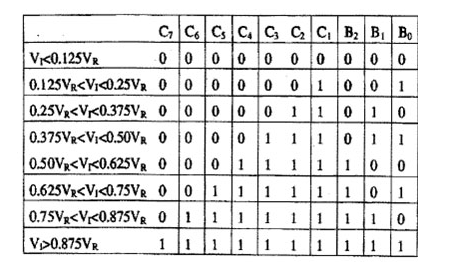

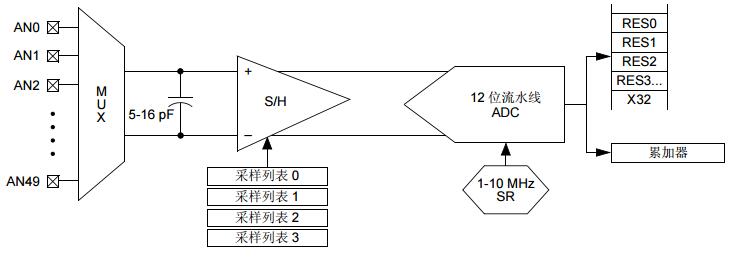

并行ADC轉換器是目前速度很快的一種結構。該結構在設計思想很容易理解。一個n位的并行ADC包含2n-1個比較器和2n-1個參考電壓值(對于一般的電壓模電路,對于電流模電路,是參考電流值)。每一個比較器對輸入信號采樣并把輸入信號與參考電壓相比較,然后每一個比較器產生一位輸出,表明輸入信號比參考電壓大還是小。2n-1個比較器輸出通常稱為溫度計代碼。該名稱的來源是,如果把比較器的輸出根據參考電壓值的大小順序排成一列,所有的1都在下面,所有的0都在上面,0和1的分界線表示信號值所在的范圍,由于和水銀溫度計表示溫度的方法相類似,因此稱為溫度計代碼。如圖為一個簡單的3位并行ADC的結構圖。譯碼器把比較器產生的溫度計代碼轉換成如表所示的二進制代碼。如圖所示,所有的比較器并行工作。因此,轉換速度僅僅受比較器的速度或采樣速度的限制,所以并行ADC具有很高轉換速度。

并行ADC的不足之處是硬件需求量大和對比較器偏移比較敏感。上面己經提到,一個n位的ADC需要2n-1個比較器。因此,高分辨率的并行ADC需要較大的芯片面積,這樣電路的功耗也增加很多。此外,大量的比較器使采樣電路要驅動很大的電容。n位分辨率的并行ADC要求比較器的偏移小于VR/2n。在較高的分辨率下,這要求比較器的偏移非常小。由于小偏移的比較器設計難度大、價格高,而且所用的比較器數量很大,因此超過8位的ADC很少用全并行結構。

二、流水線ADC和其它ADC的比較

1. 與逐次逼近型比較

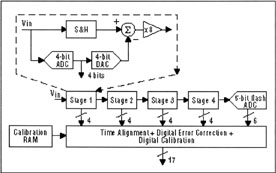

在逐次逼近(SAR)ADC中,用一個高速高精度比較器將模擬輸入和前一次得到的模數轉換結果通過DAC后的輸出相比較,依次得到MSB到LSB的每一位,逐漸逼近輸入模擬信號。SAR的這一串行工作方式從本質上限制了它的工作速度,最高約為幾Msps左右,對更高的分辨率(14到16位)速度就更低。流水線ADC則不同,它是并行結構,各級同時以逐次方式得到1位或幾位。雖然SAR中只需一個比較器,但是這個比較器必須高速工作(速率約為總位數×采樣速率),其精度必須與ADC本身一樣高,相反,流水線ADC內的比較器則不需要這一速度和精度。

當然,流水線ADC通常比相同位數的SAR占據更多的硅片面積。SAR只需一周期的延遲時間(=1/Fsample)就得到結果,而流水線ADC需要3或更多周期的延遲。與流水線ADC一樣,12位精度以上的SAR也需要某些形式的校正和標定。

2. 與閃速型比較

盡管流水線ADC是并行機制,但它還需要DAC的精密轉換和級間增益放大,因此存在建立時間問題。純閃速型ADC不同,它有大量的比較器,每個比較器由寬帶,低增益前置放大和鎖存器構成。該前置放大器不像流水線ADC中的放大器,它只需提供增益,不需要線性和精度,只是比較器的觸發點要很精確。因此流水線ADC速度根本比不上設計得很好的閃速型ADC.

雖然超高速8位閃速ADC(及各種合并/插值變體)的采樣速率高達1.5Gsps(比如MAX104/MAX106/MAX108),但是很難找到10位的閃速ADC,特別是12位及高于12位的ADC還沒有商用化。這是因為閃速ADC分辨率每增加1位,比較器數量就增加1倍,同時每個比較器的精度必須增加1倍。流水線ADC則不同,它的復雜性隨分辨率線性增加,不是指數增加。

在相同的采樣速率下,流水線ADC比閃速ADC消耗功率少得多。流水線ADC不易受比較器亞穩態的影響。閃速ADC中的比較器亞穩態會導致火花碼錯誤(即ADC輸出不可預測、不穩定結果的情況)。

3. 與Σ-Δ型比較

過采樣/Σ-Δ型ADC多用于帶寬限于22KHz以內的數字音響中。但是最近一些Σ-Δ型轉換器已經在12到16位的分辨率下達到了1至2MHz的帶寬。它們通常是高階的Σ-Δ調制器(比如4階或更高),同一個多位的ADC和多位的DAC一起工作,主要應用于ADSL。Σ-Δ型轉換器無需校正/標定,即使是16到18位分辨率,也不需要模擬輸入前的陡峭滾降的抗混疊濾波器,因為它的采樣頻率遠遠高于有效帶寬,它由后端的數字濾波器來處理混疊問題。Σ-Δ型轉換器的過采樣本質還把模擬輸入中的任何系統噪聲“平均濾除”。

但是Σ-Δ型轉換器是以犧牲速度換取分辨率的。每輸出一次采樣結果都需要對輸入采樣很多次(比如至少16次,甚至更多),這就需要Σ-Δ調制器中模擬元件的工作速率要比最終數據輸出速率快很多。數字濾波器的設計比較繁瑣,另外,它也占據了一些硅片面積。目前,最快的高分辨率Σ-Δ型轉換器還達不到幾MHz的帶寬。像流水線ADC一樣,Σ-Δ型轉換器也有延遲。

責任編輯人:CC

-

adc

+關注

關注

99文章

6720瀏覽量

549507 -

流水線ADC

+關注

關注

0文章

3瀏覽量

1897

發布評論請先 登錄

流水線ADC結構解析 流水線ADC和其它ADC的比較

一種流水線結構AD轉換器的速度分析方法

流水線ADC

流水線ADC的行為級仿真

新型流水線實現高速低功耗ADC的原理及方法

移植到全新的PIC24F流水線ADC和Σ-ΔADC

了解流水線型ADC

評論