緊迫的時間表有時會讓工程師忽略除了 VIN、 VOUT和負載要求等以外的其他關鍵細節,將PCB應用的電源設計放在事后再添加。遺憾的是,后續生產PCB時,之前忽略的這些細節會成為難以診斷的問題。例如,在經過漫長的調試過程后,設計人員發現電路會隨機出現故障,比如,因為開關噪聲,導致隨機故障的來源則很難追查。

選擇繁多 對于特定的電源設計,可能有多種可行的解決方案。在下面的示例中,我們將介紹多種選擇,例如單芯片電源與多電壓軌集成電路(IC)。我們將評估成本和性能取舍。探討低壓差(LDO)穩壓器與開關穩壓器(一般稱為降壓或升壓穩壓器)之間的權衡考量。還將介紹混合方法(即LDO穩壓器和降壓穩壓器的混合與匹配),包括電壓輸入至輸出控制(VIOC)穩壓器解決方案。 在本文中,我們將分析開關噪聲,以及在開關電源設計無法充分濾波時,PCB電路會受哪些影響。從總體設計角度來看,還需考慮成本、性能、實施和效率等因素。 例如,如何根據給定的一個或多個電源實現多電源拓撲優化設計?我們將藉此深入探討設計、IC接口技術、電壓閾值電平,以及哪類穩壓器噪聲會影響電路。我們將分析一些基本邏輯電平,例如5 V、3.3 V、2.5 V和1.8 V晶體管-晶體管邏輯(TTL)、互補金屬氧化物半導體(CMOS),及其各自的閾值要求。 本文還會提及正發射極耦合邏輯(PECL)、低壓PECL(LVPECL)和電流模式邏輯(CML)等先進邏輯,但不會詳細介紹。這些都是超高速接口,對于它們來說,低噪聲電平非常重要。設計人員需要知道如何避免信號擺幅引起的這些問題。 在電源設計中,成本和性能要求并存,所以設計人員必須仔細考慮邏輯電平和對干凈電源的要求。在公差和噪聲方面,通過設計實現可靠性并提供適當裕量,也可以避免生產問題。 設計人員需要了解與電源設計相關的權衡考量:哪些可實現?哪些可接受?如果設計達不到要求的性能,那么設計人員必須重新審視選項和成本,以滿足規格要求。例如,多軌器件(例如 ADP5054)可以在保持成本高效的同時提供所需的性能優勢。

典型設計示例

我們先來舉個設計示例。圖1顯示將12 V和3.3 V輸入電源作為主電源的電路板框圖。主電源必須降壓,以便針對PCB應用產生5 V、2.5 V、1.8 V,甚至3.3 V電壓。如果外部3.3 V電源能夠提供足夠的電源和低噪聲,那么可以直接使用3.3 V輸入電軌,無需額外調節,以免產生額外成本。如果不能,則可以使用12 V輸入電軌,通過降壓至PCB應用所需的3.3 V來滿足電源要求。

圖1.需要多軌電源解決方案的應用電路板概覽。

邏輯接口概述

PCB一般使用多個電源。IC可能僅使用5 V電源;或者,它可能要求多個電源,輸入/輸入接口使用5 V和3.3 V,內部邏輯使用2.5 V,低功耗休眠方式使用1.8 V。低功耗模式可能始終開啟,用于定時器功能、管理等邏輯,或用于中斷時啟用喚醒模式,或者用于IRQ引腳,以啟用IC功能并為其供電,也就是5 V、3.3 V和2.5 V電源。所有這些或其中部分邏輯接口通常都在IC內部。

圖2顯示了標準邏輯接口電平,包括各種TTL和CMOS閾值邏輯電平,以及它們可接受的輸入和輸出電壓邏輯定義。在本文中,我們將討論何時將輸入邏輯驅動至低電平(用輸入電壓低 (VIL)表示),何時驅動至高電平(用輸入邏輯電平高 VIH表示)。我們將重點分析VIL,即圖2中標記為“Avoid”的閾值不確定區域。

在所有情況下,必須考慮±10%的電源公差。圖3顯示了高速差分信號。本文將著重探討圖2所示的標準邏輯電平。

圖2.標準邏輯接口電平。

開關噪聲

未經過充分濾波時,開關穩壓器降壓或升壓電源設計可能產生幾十毫伏至幾百毫伏的開關噪聲,尖峰可能達到400 mV至600 mV。所以,了解開關噪聲是否會給使用的邏輯電平和接口造成問題非常重要。

安全裕度 為確保提供合適的安全裕度,實現可靠的PSU,一條設計經驗法則是采用最糟糕情況下的–10%公差。例如,對于5 V TTL,0.8 V的VIL變成0.72 V,對于1.8 V CMOS,0.63 V的VIL變成0.57 V,閾值電壓(VTH)也相應降低(5 V TTL VTH= 1.35 V,1.8 V CMOS VTH= 0.81 V)。開關噪聲(VNS)可能為幾十毫伏到幾百毫伏。此外,邏輯電路本身也會產生信號噪聲(VN),即干擾噪聲。總噪聲電壓(VTN= VN + VNS)可能在100 mV至800 mV之間。將VTN添加至標稱信號中,以生成總信號電壓(VTSIG):實際的總信號(VTSIG= VTSIG+ VTN)會影響閾值電壓(VTH),進一步擴大了avoid區域。VTH區域內的信號電平是不確定的,在該區域內,邏輯電路可以任意隨機翻轉;例如,在最糟糕的情形下,會錯誤觸發邏輯1,而不是邏輯0。

圖3.高速差分邏輯接口電平。

多軌PSU注意事項和提示

通過了解接口輸入和IC內部邏輯的閾值電平,我們現在知道哪些電平會觸發正確的邏輯電平,哪些會(意外)觸發錯誤的邏輯電平。問題在于:要滿足這些閾值,電源的噪聲性能需要達到什么水平?低壓差線性穩壓器噪聲很低,但在高壓降比下卻并不一定高效。開關穩壓器可以有效降壓,但會產生一些噪聲。高效低噪的電源系統應包含這兩種電源的組合。本文著重介紹各種組合,包括在開關穩壓器后接LDO穩壓器的混合方法。

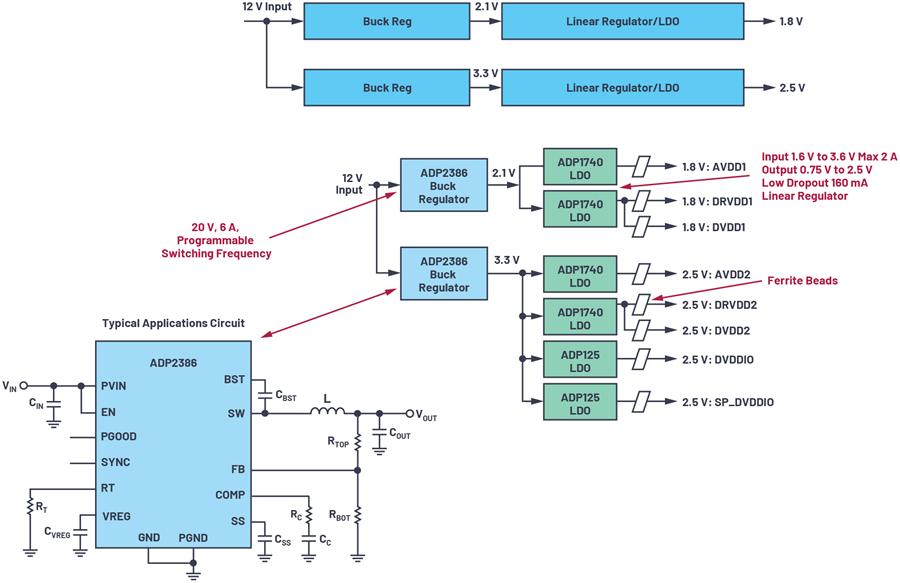

(在需要時)最大化效率和最小化噪聲的方法 從圖1所示的設計示例可以看出,為了充分提高5 V穩壓的效率并盡可能降低開關噪聲,需要分接12 V電路并使用降壓穩壓器,例如 ADP2386。從標準邏輯接口電平來看,5 V TTL VIL和 5 V CMOS VIL分別是0.8 V和1.5 V,僅使用開關穩壓器時,也具備適當的裕度。對于這些電軌,通過使用降壓拓撲可實現效率最大化,而開關噪聲則低于采用5 V(TTL和CMOS)技術時的 VIL。通過使用降壓穩壓器(例如圖4a所示的ADP2386配置),效率可以高達95%,如ADP2386的典型電路和效率曲線圖所示(見圖4b)。如果在此設計中使用噪聲較低的LDO穩壓器,從VIN到VOUT的7 V壓降會導致消耗大量內部功率,一般表現為產生熱量和損失效率。為了以少量額外成本實現可靠設計,在降壓穩壓器后接LDO穩壓器來產生5 V電壓也是一項額外優勢。

圖4.ADP2386的(a)典型電路和(b)效率曲線圖。

圖5.典型的ADP125應用。

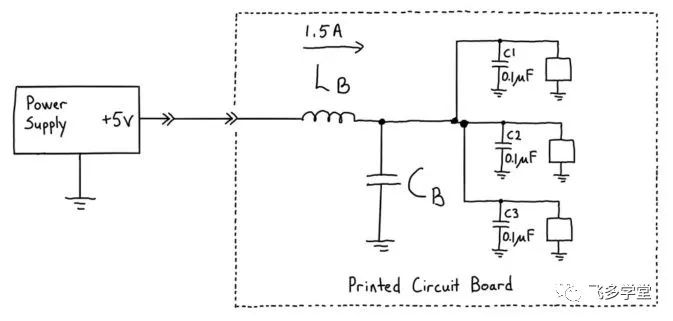

2.5 V和1.8 V CMOS的 VIL分別是0.7 V和0.63 V。遺憾的是,此邏輯電平的安全裕度尚不足以避免開關噪聲。要解決此問題,有兩種方案可選。第一種:如果圖1所示的外部3.3 V電源具備足夠功率且噪聲極低,則分接這個外部3.3 V電源,并使用線性穩壓器(LDO穩壓器),例如 ADP125 (圖5)或 ADP1740來獲得2.5 V和1.8 V電源。注意,從3.3 V到1.8 V有1.5 V壓降。如果此壓降會導致問題,則可以使用混合方法。第二種:如果外部3.3 V電源的噪聲不低,或不能提供足夠功率,則分接12 V電源,通過降壓穩壓器后接LDO穩壓器來產生3.3 V、2.5 V和1.8 V電源;混合方法如圖6所示。 加入LDO穩壓器會稍微增加成本和板面積以及少量散熱,但要實現安全裕度,有必要作出這些取舍。使用LDO穩壓器會小幅降低效率,但可以通過保持 VIN至 VOUT的少量壓降,使這種效率降幅達到最低:3.3 V至2.5 V,保持0.8 V,或3.3 V至1.8 V,保持1.5 V。可以使用帶VIOC功能的穩壓器盡可能提高效率和瞬變性能。VIOC可以調節上游開關穩壓器的輸出,從而在LDO穩壓器兩端保持合理的壓降。帶VIOC功能的穩壓器包括 LT3045、 LT3042 和 LT3070-1。 LT3070-1是一款5 A、低噪聲、可編程輸出、85 mV低壓差線性穩壓器。如果必須使用LDO穩壓器,則存在散熱問題,其中功耗= VDROP× I。例如,LT3070-1支持3 A,穩壓器兩端的功率降幅(或功耗)典型值為3 A × 85 mV = 255 mW。相比壓差為400 mV,輸出電流同樣為3 A,功耗為1.2 W的一些典型LDO穩壓器,LT3070-1的功耗僅為其五分之一。 或者,我們可以使用混合方法,以犧牲成本為代價來提高效率。圖6中效率和性能均得到優化,其中先使用降壓穩壓器(ADP2386)將電壓降至允許的最低電壓,盡量提高效率,后接一個LDO穩壓器(ADP1740)。

圖6.使用ADP2386和ADP1740組合的混合拓撲。

此練習提供一個通用設計示例,用于顯示一些拓撲和技術。但是,也不能忘記考慮其他因素,例如IMAX、成本、封裝、壓降等。 也提供低噪聲降壓和升壓穩壓器選項,例如SilentSwitcherregulators,它具備極低的噪聲和低EMI。例如,從性能、封裝、尺寸和布局區域來看, LT8650S 和 LTC3310S 具有成本高效特性。

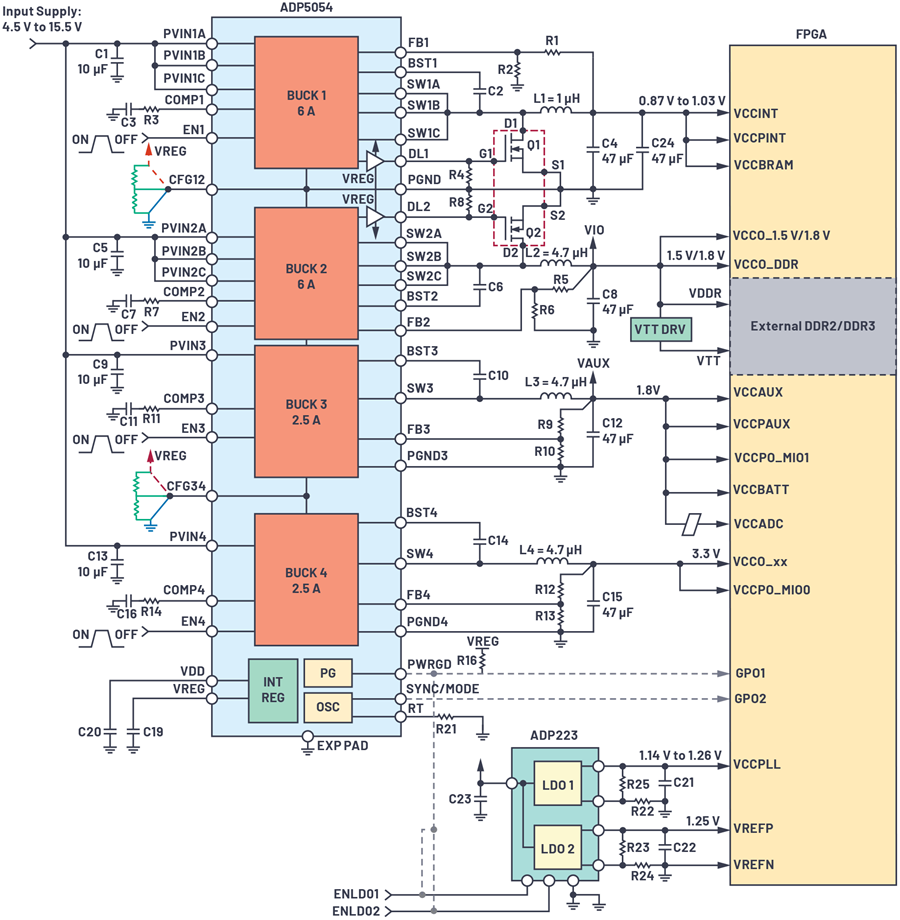

封裝、功率、成本、效率和性能取舍 量產PCB設計通常要求使用緊湊的多軌電源,以實現高功率、高效率、出色的性能和低噪聲。例如,ADP5054四通道降壓穩壓器為FPGA等應用提供高功率(17 A)單芯片多軌電源解決方案,如圖7所示。整個電源解決方案約41 mm × 20 mm大小。ADP5054本身的大小僅為7 mm × 7 mm,可以提供17 A總電流。要在緊湊空間內實現極高的功率電平,可以考慮使用ADI的μModuleregulators,例如 LTM4700,可以在15 mm × 22 mm的封裝大小內提供高達100 A電流。

圖7.適合FPGA應用的ADP5054單芯片多軌電源解決方案。

圖8.ADP5054原理圖。

ADP5054

通道 1 和通道 2

具有低端 FET 驅動器的可編程 2 A/4 A/6 A 同步降壓穩壓器

通道 3 和通道 4:2.5 A 同步降壓穩壓器

單一 12 A 輸出(通道 1 和通道 2 并聯)

單一 5 A 輸出(通道 3 和通道 4 并聯)

在 10 Hz 至 100 kHz 頻率下,0.8 VREF時為 40 μV rms

寬輸入電壓范圍:4.5 V 至 15.5 V

±整個溫度范圍下的輸出精度為 1.5%

250 kHz 至 2 MHz 可調開關頻率,并具有單獨的 ?× 頻率選項

功率調整

靈活的并行操作

低 1/f 噪聲密度

0.811 V 精確閾值的精密啟用

有源輸出放電開關

FPWM/PSM 模式選擇

頻率同步輸入或輸出

通道 1 輸出具有電源正常標記

UVLO、OCP 和 TSD 保護

48 引腳 7 mm × 7 mm LFCSP

工作結溫范圍為 ?40°C 至 +125°C

責任編輯:lq

-

開關電源

+關注

關注

6460文章

8331瀏覽量

481847 -

PCB電路

+關注

關注

1文章

37瀏覽量

11094

原文標題:【世說設計】設計多軌電源時,你可能會忽略這些問題哦~

文章出處:【微信號:Excelpoint_CN,微信公眾號:Excelpoint_CN】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開關電源在LED照明中的應用

什么叫開關電源?有什么特點

在用開關電源給低噪聲放大器供電時,電源噪聲對信號影響很大,有沒有比較理想的隔離濾波電路?

llc開關電源和普通開關電源的區別

開關電源紋波噪聲產生原因,開關電源紋波噪聲怎么解決

開關電源的噪聲是如何產生的?

開關電源濾波器設計與應用

開關噪聲,以及在開關電源設計無法充分濾波時,PCB電路會受哪些影響

開關噪聲,以及在開關電源設計無法充分濾波時,PCB電路會受哪些影響

評論