現場可編程門陣列(FPGA)的起源可以追溯到20世紀80年代,從可編程邏輯器件(PLD)演變而來。自此之后,FPGA資源、速度和效率都得到快速改善,使FPGA成為廣泛的計算和處理應用的首選解決方案,特別是當產量不足以證明專用集成電路(ASIC)的開發成本合理有效時。

FPGA取得快速發展,并廣泛用于大規模部署。例如,繼2013年試點項目中使用FPGA成功加快Bing搜索引擎的速度之后, Microsoft? 將配備FPGA的服務器使用范圍擴展到云數據中心。

FPGA電源系統要求

FPGA需要幾個不同的低壓供電軌,每個供電軌都有自己的電壓和電流規格,以便為其內核邏輯、I/O電路、輔助邏輯、收發器和存儲器供電。這些供電軌可能需要按特定的順序開啟和關閉,以避免損壞FPGA。負載點(POL)穩壓器將電路板較高的輸入電源電壓降低為FPGA所需的多個輸入電壓。當功率轉換效率至關重要時,開關穩壓器可用作POL穩壓器,而線性穩壓器(例如低壓差(LDO) 穩壓器)則用于噪聲敏感型電路,例如PLL和收發器。

典型的電路板輸入電壓為5 V、12 V、24 V和48 V,FPGA的輸入電壓范圍則為低于1 V至約3 V。對于高輸入電壓(12 V、24 V、48 V),可能需要使用額外的降壓穩壓器來生成饋送給POL穩壓器的中間總線電壓(參見圖1)。在FPGA供電軌中,核電壓需要最低的電壓(約等于或低于1 V)和最高的精度(±3%或更優),電流電平約為幾十安培,具體取決于FPGA資源的利用率。為了防止出現邏輯錯誤,不僅在直流條件下,而且在FPGA電流瞬態期間,電壓波動都需要按照FPGA供電軌公差規格要求控制在幾十毫伏之內。電源的直流精度越差,在瞬態條件下維持可用電源電壓所需的旁路電容就越多。例如,假設采用±3%內核電壓公差規格。使用精度為±1%的直流電源時,對應的瞬態公差為±2%。直流電源的精度較低(±2%)時,瞬態公差會更嚴格(±1%),相比之前的示例,需要更多的旁路電容。

圖1. 一種可行的FPGA電源樹設計:高壓輸入電源(例如12 V、24 V或48 V)降至中間總線電壓,然后饋送給為FPGA供電的POL穩壓器。

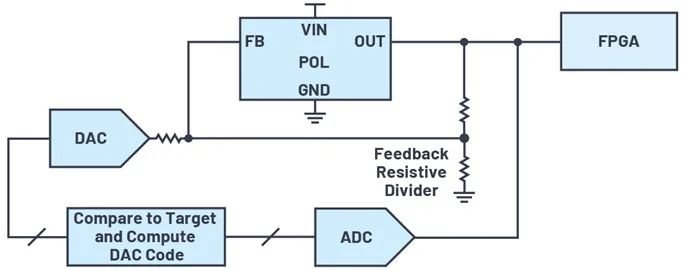

在最終進行設計變更、在另一種應用中重用設計、實施板裕量測試,以及在開發或現場運行期間動態優化系統功耗時,都需要基于默認的設定點調整或微調FPGA電源電壓電平。在這種情況下,在電源反饋網絡中采用多個不同電阻并聯不是最快或最可行的解決方案。實現電壓微調的一種方法是使用數模轉換器(DAC)來驅動穩壓器的反饋網絡(參見圖2)。需要為微調程序編寫軟件代碼,從模數轉換器(ADC)獲取電源電壓測量數據,以計算正確的DAC代碼,然后緩慢將DAC輸出調節至計算出的數字碼,逐步穩定提高電源電壓,在不會產生毛刺或過沖的情況下達到目標電壓電平。這種微調程序需要重復實施,以確保不會因為組件隨時間或溫度變化出現偏移,進而導致電源偏離目標電壓。

圖2. 使用DAC和ADC將POL電源輸出電壓微調至目標電壓。

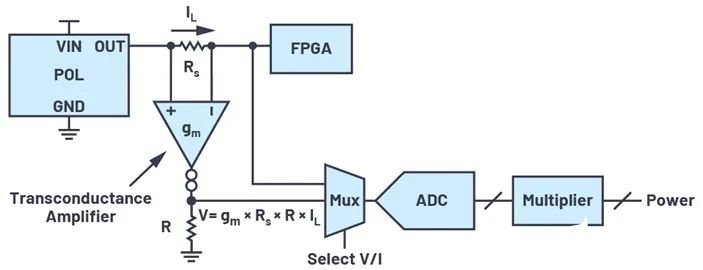

監測FPGA電源電壓、電流和故障條件,對于理解系統在不同場景下的健康狀況和功耗至關重要,這是因為,FPGA是整個電子系統的核心。將這種理解和微調功能結合起來,可以避免為最壞的情況設計電源,從而節省成本和功率。此外,潛在的系統故障可能表現為FPGA功耗異常,從而在電路板或系統發生故障之前讓主機控制器或維修人員及早發現問題。電壓監測需要使用ADC,而電流監測還需要使用電平偏移電路將高電平電流檢測電壓轉換為接地基準電壓;例如,如圖3所示,通過使用跨導放大器。

圖3. 用于監測POL電源輸出電壓、電流和功率的一種分立式電路可行方案。

雖然我們還未探討故障管理,但看了這一長串要求之后,您可能已頭暈腦脹。當POL輸出出現欠壓或過壓時,即在有效的電壓窗口范圍外時,會出現什么情況?應該只關閉故障電源?還是應該也關閉其他電源?如何消除導致系統板關斷的故障?

我們可以看到,FPGA的電源系統管理很快會變得非常復雜,從而分散對基本的FPGA應用的關注。注意,FPGA的電源樹只是數字處理電路板上整個電源系統的一部分。上述大部分要求也適用于其他數字器件,例如ASIC、DSP、GPU、SoC和微處理器。我們所需的是一個簡單、可擴展且靈活的電源系統管理解決方案。

數字電源系統管理

ADI公司提供數字電源系統管理(DPSM)器件產品,以滿足數字處理電路板中復雜的電源系統要求。DPSM器件可提供或不提供集成DC/DC轉換,以替代POL穩壓器,或者與現有的POL穩壓器配合使用。電源系統管理器不提供DC/DC轉換,對于由開關或LDO穩壓器構成的現有模擬電源系統,可增加數字監測和控制功能。使用單個器件(例如 LTC2980),可對16個POL穩壓器實施微調、裕量調節、監測、時序控制、電源監控、故障記錄和故障管理。可以混合和匹配使用不同通道數器件(2、4、8或16個通道),以管理數百個供電軌。雙通道 LTC2972是該系列的最新產品,它提供了一種簡單的入門解決方案,可監測和控制此類電源系統中兩個最重要的供電軌;例如,FPGA內核供電軌和輔助供電軌。

雙通道電源系統管理器

LTC2972是一款雙通道電源系統管理器,為FPGA、ASIC和處理器電路板增加了基于軟件的全面監測、控制和黑盒故障記錄功能,可加快產品上市,提升系統可靠性,以及優化電路板功耗(圖4)。使用出色的16位ADC對POL電源輸出電壓實施微調、裕量調節和監測,總非調整誤差(TUE)為0.25%,以提升電路板的功率和長期性能。因為能夠嚴格控制POL輸出電壓,實現±0.25%的精度,所以在負載瞬態(在±3% FPGA供電軌規格下,精度為±2.75%)期間有很大的裕量,從而大幅減少所需的旁路電容并釋放電路板空間。電源輸出電流使用檢測電阻、電感DCR,或者電源的IMON輸出進行測量。電壓和電流測量值在內部進行乘法運算,提供POL輸出功率讀數。

圖4. LTC2972是一款雙通道電源系統管理器,提供中間總線電源監測和 POL輸出功率監測。

LTC2972內置電源時序控制、監控和EEPROM故障記錄功能。通過將時間延遲寫入內部寄存器或使用級聯電源良好信號來完成時序控制。當POL輸入電壓、輸出電壓和溫度以數字方式偏離可設置閾值上下限時,專用快速比較器發出故障信號。故障觸發EEPROM黑盒記錄,簡化故障分析,并提供有關未來系統改進的相關見解。第一個故障命令提供關于系統故障原因的更多信息。故障信 息可靈活傳播到其他電源或其他DPSM器件。

LTC2972支持對POL轉換器的中間總線輸入實施電壓、電流、功率和電能監控。為了管理、優化和降低電路板功耗,進而降低服務器和數據中心的散熱和公用設施成本,必須監測電路板功率和電能使用狀況。LTC2972通過PMBus接口(與電源管理和轉換器件通信的行業標準)方便地提供輸出電能(單位:焦耳)和運行時間,以減少繁重的輪詢和計算任務。將LTC2972與POL輸出電壓、電流和功率這些數字測量值結合使用,就可以長期監測電源系統的轉換效率。

每個通道都配有可編程電源良好引腳或通用輸入/輸出(GPIO)引腳。LTC2972與其他電源系統管理器連接,可實現兩個以上供電軌的時序和故障管理。使用通過 I2C/SMBus 接口傳輸的兼容PMBus命令,可對電源系統實施靈活編程和數據回讀。配置在支持ADI所有DPSM產品的 LTpowerPlay?開發環境下完成(參見圖5)。采用所需的應用特定配置進行內部EEPROM編程后,就無需為實現自動運行而編寫軟件代碼。

圖5. 適用于DPSM產品的LTpowerPlay開發環境:無需為實現自動運行而編寫代碼。

FPGA廣泛應用于各種電子系統,甚至取代ASIC,但其周圍具有復雜的電源系統。ADI公司提供多種DPSM產品來幫助簡化電源系統管理。如果您以前從未用過DPSM,您可以試試LTC2972,這是一款入門級產品,能夠解決數字處理電路板上復雜的電源系統問題。

責任編輯:haq

-

電源

+關注

關注

184文章

17715瀏覽量

250108 -

FPGA

+關注

關注

1629文章

21736瀏覽量

603238 -

電路圖

+關注

關注

10342文章

10721瀏覽量

530497

發布評論請先 登錄

相關推薦

nPM1300—具有獨特系統管理功能的電源管理集成電路(PMIC)

NORDIC NPM1300是一款高度集成的電源管理集成電路

PD快充芯片U8724AH集成實現更高效的電源系統管理

IBMS管理平臺如何幫助企業實現數字化轉型

Linux高級文件系統管理詳解

化工人員定位系統管理的核心是什么?

TCA9546A具有復位功能的低壓通道I2C和系統管理總線(SMbus)開關數據表

TCA9544A低壓4通道I2C和系統管理總線(SMbus)復用器數據表

TCA9545A低壓4通I2C和系統管理總線(SMbus)開關數據表

TCA9534A具有中斷輸出和配置寄存器的低壓8位I2C和系統管理總線(SMBUS)低功耗輸入輸出(I/O)擴展器數據表

TCA9554低壓8位I2C和系統管理總線(SMbus)低功耗輸入輸出(I/O)擴展器數據表

SMBus協議的工作原理和應用特性

FPGA助力簡化電源設計

簡化FPGA電源系統管理的辦法

簡化FPGA電源系統管理的辦法

評論