AXI-Stream代碼詳解

AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據突發傳輸規模。AXI4-Stream的核心思想在于流式處理數據。

圖 4?58 AXI-Stream Interface

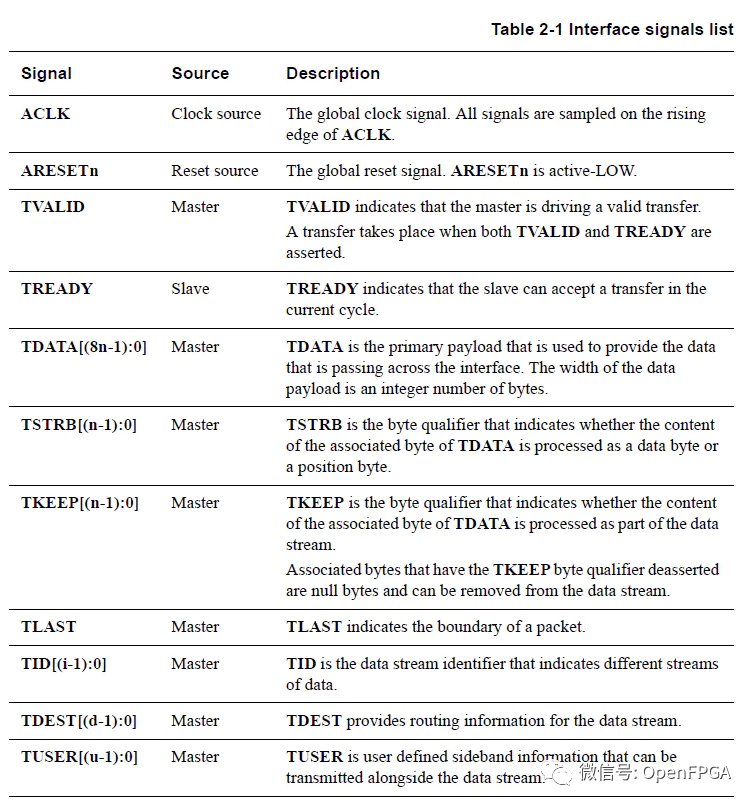

全局信號

1.ACLK 全局時鐘信號,在上升沿時對信號采樣。所有的輸入信號都通過上升沿采集,所有的輸出信號都在上升沿時變化。

2.ARESETn 全局復位信號,低電平有效。在復位期間,所有的xxVALID信號必須復位為低電平。其他的信號可以是任意值。

主機(master)控制的信號

3.TVALID 握手信號

4.TDATA 數據信號線

5.TSTRBTDATA的內容修飾符,用于指示是數據字節還是位置字節。初學者默認為1即可.

6.TKEEPTDATA的內容修飾符,用于指示是此字節是否為有效字節,和TSTRB配合使用。如下表。xilinx封裝的ip中不使用此信號,所以默認為1。

| TSTRB | TKEEP | data type |

| high | high | 數據字節 |

| high | low | 位置字節 |

| low | low | 無效字節 |

| low | low | 保留 |

7.TLAST 置高表示本次流傳輸中的最后一個數據。

8.TID 表示不同數據流的數據流標識符。xilinx封裝的ip中沒有此信號。

9.TDEST 用于提供路由信息,xilinx封裝的ip中沒有此信號。

10.TUSER AXI4協議留給用戶自定義的。xilinx封裝的ip中沒有此信號。

從機(slave)控制的信號

11.TREADY 握手信號

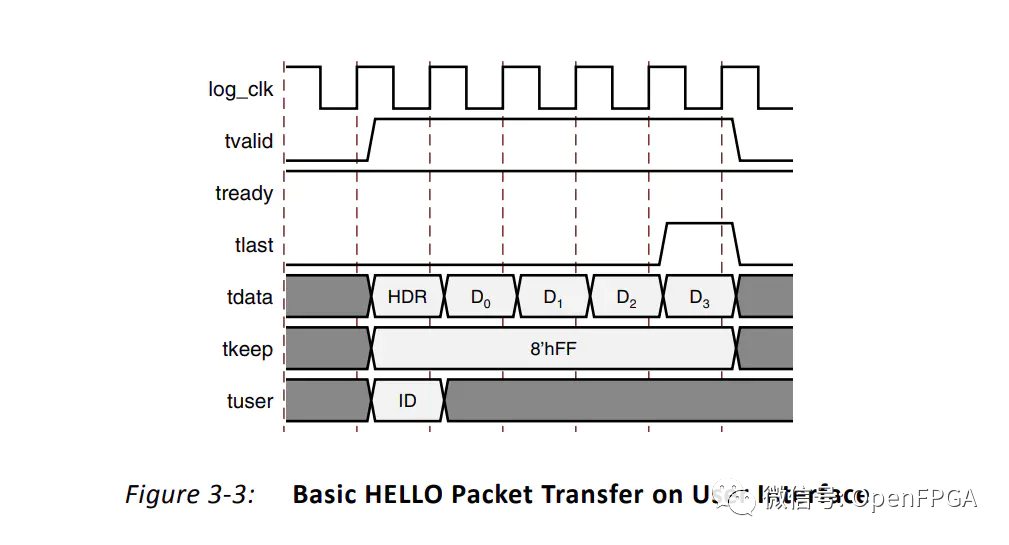

一個AXI-stream傳輸的時序圖:

圖4?59 AXI-stream example

AXI4-stream主從交互仿真

lvivado創建工程,添加代碼。

l編寫仿真tb文件。

下圖是AXI4-stream主從交互的時序圖。

圖4?60 AXI4-stream主從交互的時序圖

其中AXI-stream一般的數據傳輸過程如下:

1、首先slave將TREADY信號拉高,表示自己可以接收信號。

2、當master將TDATA,TKEEP,TUSER準備就緒之后,將TVALID拉高,傳輸開始。

3、其中TKEEP滿足TKEEP[x] is associated with TDATA[(8x+7):8x],當其被拉高時表示這段數據必須傳輸到目的地。TSTRB表示該段信息是否有效。TUSER可以在傳遞時捎帶用戶信息。具體接口參照使用的AXI-stream接口器件,并非所有支持AXI-stream接口的器件都含有以上接口,其中的一些接口是可選的而不是必需的。

4、直到master將TLAST拉高,TVALID拉低,傳輸結束。

代碼在這里:

鏈接:https://pan.baidu.com/s/1FprBYZ37FP-deT38pWzSwg

提取碼:open

責任編輯:xj

原文標題:AXI-Stream代碼詳解

文章出處:【微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

-

代碼

+關注

關注

30文章

4779瀏覽量

68525 -

Stream

+關注

關注

0文章

20瀏覽量

7968 -

AXI

+關注

關注

1文章

127瀏覽量

16622

原文標題:AXI-Stream代碼詳解

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMBA AXI4接口協議概述

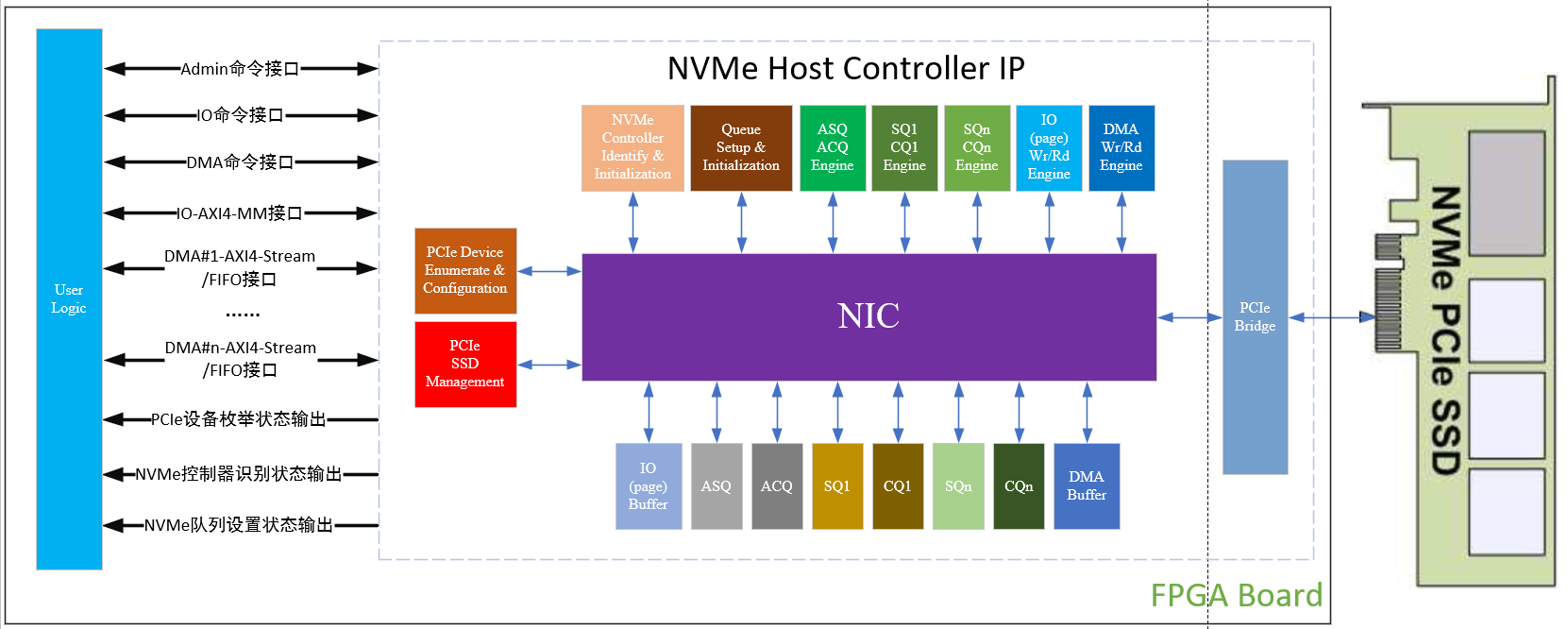

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

Fx3 an65974 stream_in示例不起作用是怎么回事?

ESP-ADF下的i2s_stream是否可以全雙工工作?

SoC設計中總線協議AXI4與AXI3的主要區別詳解

使用STM32F429的DMA多個外設都使用到同樣的DMA_STREAM的時候,就會發生沖突怎么解決?

FPGA通過AXI總線讀寫DDR3實現方式

Multi-Channel PCIe QDMA&RDMA IP應用介紹

Xilinx高性能PCIe DMA控制器IP,8個DMA通道

PCIe-AXI-Cont用戶手冊

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

如何從SD卡讀取音頻文件并將其輸出到揚聲器上?

漫談AMBA總線-AXI4協議的基本介紹

AXI-Stream代碼

AXI-Stream代碼

評論