Vivado HLS 2020.1將是Vivado HLS的最后一個版本,取而代之的是VitisHLS。那么兩者之間有什么區別呢?

Default User Control Settings

在Vitis HLS下,一個Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下圖所示。前者最終導出來的是VivadoIP,用于支持Vivado IP 設計流程。后者用于Vitis應用加速流程,此時,Vitis HLS會自動推斷接口,無需在代碼里通過Pragma或Directive的方式定義Interface,最終會輸出.xo文件。

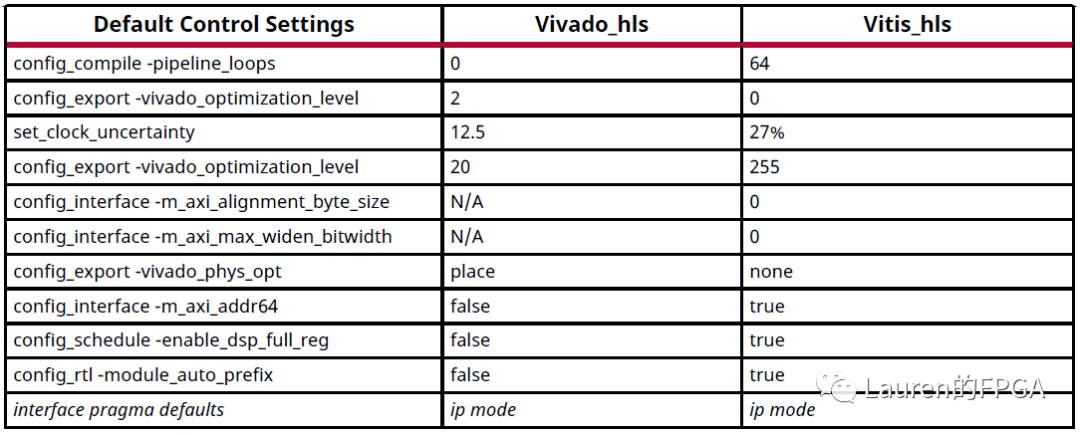

User Control Settings還有其他的一些變化,如下表所示。例如,在Vivado HLS下,默認是不會對循環設置Pipeline的,但在Vitis HLS下,只要循環邊界小于64,就會對循環設置Pipeline。在Vivado HLS下,默認Clock Uncertainty是時鐘周期的12.5%,但在Vitis HLS下更嚴格,達到了27%。

對循環而言,在Vivado HLS下,II(Initial Interval)默認的約束值為1,但在Vitis HLS下,II默認值為auto,意味著工具會盡可能達到最好的II。 目前,針對Vitis HLS,Xilinx已經提供了如下文檔和設計案例: UG1391:Vitis HLSMigration Guide UG1399:VitisHigh-Level Synthesis User Guide Vitis HLS examples: https://github.com/Xilinx/HLS-Tiny-Tutorials

責任編輯:xj

原文標題:Vivado HLS和Vitis HLS什么區別?

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

-

代碼

+關注

關注

30文章

4895瀏覽量

70523 -

Vivado

+關注

關注

19文章

834瀏覽量

68580 -

HLS

+關注

關注

1文章

133瀏覽量

24781

原文標題:Vivado HLS和Vitis HLS什么區別?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

CDS與SDS供液系統兩者之間的區別

Vivado HLS設計流程

TXB0104與TXS0102兩者之間有什么區別嗎?

ADC的接口有Serial SPI和SPI兩種,它們之間有什么區別?

請問ADC器件的interface中有分為Parallel lvds和serial lvds,請問這兩者有什么區別?

當ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

顯示器驅動板和電腦主板的區別

優化 FPGA HLS 設計

光纖通信與光通信有什么區別

一種在HLS中插入HDL代碼的方式

評論