模擬濾波器在電子信號合成系統中應用廣泛,可為ADC提供抗混疊和降噪,為DAC提供信號重建濾波1。不同的設計要求需要使用不同的濾波器架構,常用的濾波器有貝塞爾、巴特沃思以及橢圓濾波器。

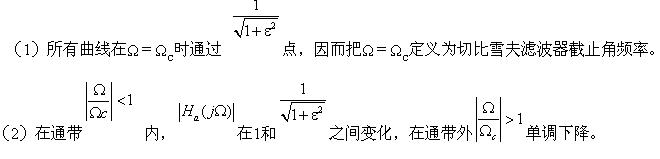

貝塞爾低通濾波器具有線性相位響應,通帶無紋波、阻帶單調衰減,適合時域應用。巴特沃思低通濾波器在通帶內具有最平坦的頻響,阻帶的單調衰減也比貝塞爾濾波器陡峭,但相位響應隨頻率非線性變化,這使得巴特沃思低通濾波器非常適合基于幅度的應用。而橢圓低通濾波器具有接近平坦的通帶響應和極為陡峭的阻帶衰減,是基于幅度的抗混疊應用的最佳選擇。

設計和實現連續時間有源濾波器非常具有挑戰性,需要使用多個高性能運放和精度很高的無源器件。設計挑戰包括如何選擇最優的濾波器架構,還需要使用專用的濾波器計算軟件2。另一個簡單的方法是使用高度集成的SCF(開關電容濾波器),SCF可以大大減少外圍元器件數目,使濾波器調諧十分簡單,并可降低系統功耗。本文通過分析如何實現一個連續時間濾波器和一個SCF來說明其在性能和復雜程度上的不同。

如上所述,貝塞爾濾波器的特性使其非常適合時域應用,因為它們在示波器/分析儀這類測試應用中幾乎沒有失真。但設計者通常需要構建更高階的貝塞爾濾波器(這意味著比巴特沃思或橢圓濾波器的極點更多)來實現足夠大的阻帶衰減。

圖1所示原理圖為5階、1.0kHz、低通貝塞爾濾波器,設計基于Sallen-Key架構,為減少元器件數目進行了優化,使用精度為1%的標準電阻和精度為5%的標準電容。為確定外圍元件值,使用了濾波器設計軟件FilterPro?,并用PSPICE仿真工具進行了驗證。

圖1.兩個運放和多個無源元件構成5階、1.0kHz、低通貝塞爾濾波器

許多情況下,輸入和輸出RC濾波器還需要一個額外的運放作緩沖,尤其是當信號源阻抗較高(大于幾百歐)或濾波器輸出的下一級輸入阻抗過低(低于幾百kΩ)時。

貝塞爾濾波器的SPICE仿真結果如圖2所示,該頻響圖是同一濾波器進行100次MonteCarlo仿真計算的結果。SPICE仿真器通過在標稱容限范圍內隨機改變外圍元件值模擬器件的差異,仿真結果揭示截止頻率會在fC=fIN-3dB±0.6dB范圍內變動,這是電容和電阻值在標稱容限內變化引起的。

圖2.5階貝塞爾濾波器SPICE仿真頻響結果

為在1kHz至15kHz的截止頻率范圍內獲得可以接受的特性(80dB或更好的動態范圍),設計人員必須使用容限更嚴格、具有更高溫度穩定性的元器件。例如:

對于截止頻率為1kHz至15kHz的濾波器來說,運放在0.5MHz至6.5MHz范圍內必須具有一致的增益,THD+N(總諧波失真+噪聲)必須小于0.005%。

電容應該采用精密的陶瓷電容或薄膜電容,而且在很寬的溫度范圍和電壓范圍內必須能夠保持穩定的標稱值。

電阻應該是容限好于±1%的金屬膜電阻,還要具有較低的溫度系數。

為了保證量產性能,元器件最好從可靠的供應商采購,如Panasonic、Rohm、Vishay、Kemet和AVX。

一個5階、截止頻率為1kHz至15kHz的貝塞爾低通濾波器的元器件BOM成本估計在$1.50至$2.00之間(1000套以上價格)。這還不包括設計、測試、PCB布板、組裝、元件采購等花費的時間成本,這些成本難以量化而且與公司有關。

Maxim提供一種更有效、更簡單的集成開關電容濾波器解決方案,利用一顆芯片即可實現大多數濾波器的效果(應用筆記733:“AFilterPrimer”介紹了更多關于SCF的技術細節)。濾波器設計人員僅需一個低成本外部電容或外部時鐘,就可以得到集成、可靠、可預測的高性價比濾波器方案,而且不易受溫度和其它環境參數影響。

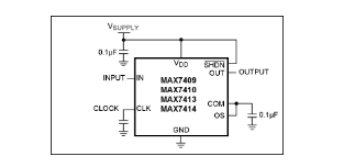

圖3和圖4是利用SCF芯片(MAX7409/MAX7413)實現5階低通貝塞爾濾波器的電路原理圖,其中的0.1μF去耦電容可以使用普通的低成本陶瓷電容(材質為X7R或Z5U),但圖4中的CCLK推薦使用COG(NPO)材質的電容。

圖3.開關電容濾波器的fC(截止頻率)可以用一個占空比為50%±10%的時鐘實現

圖4.用開關電容濾波器的內部振蕩器設置fC需要在CLK引腳和地之間接一個電容CCLK,當CCLK=300pF時,fC=1kHz。

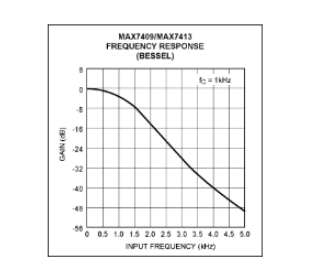

仿真和測試結果(如圖5所示)表明基于MAX7409/MAX7413的開關電容濾波器在通帶內的變化優于基于運放的連續時間濾波器。開關電容濾波器的另一個優點是易于調諧。截止頻率可以通過內部或外部時鐘調整。而對于基于運放的連續時間濾波器而言,改變截止頻率幾乎相當于重新設計濾波器。

圖5.fC=fIN處的開關電容濾波器通帶變化在整個溫度和電壓范圍內僅為-3dB±0.4dB

責任編輯人:CC

-

濾波器

+關注

關注

161文章

7795瀏覽量

177996 -

模擬濾波器

+關注

關注

0文章

33瀏覽量

13406

發布評論請先 登錄

相關推薦

模擬濾波器的設計方法

模擬濾波器的設計方法

評論