在為期三天的 2020 年虛擬閃存峰會期間,NEO 半導體首席執行官兼創始人許志安(Andy Hsu)進行了詳細的演講,介紹了該公司全新 X-NAND 閃存架構,該架構有望將 SLC 閃存的速度與 QLC 的密度和低價格相結合。

NEO Semiconductor 于 2012 年在加利福尼亞州圣何塞成立,并擁有 20 項與存儲器相關的專利。該公司于 2018 年首次公開了其 X-NAND 技術,作為面向 AI 和 5G 新興市場的存儲解決方案,他們現在已經分享關于該技術的更多細節。

▲ 圖源 Tom‘s Hardware ,下同

X-NAND 承諾將提供頂級性能:該公司聲稱其隨機讀取和寫入工作量比 QLC 閃存快 3 倍,并且在順序讀取和寫入工作量方面分別超出 27 倍 / 14 倍(請參見上圖)。

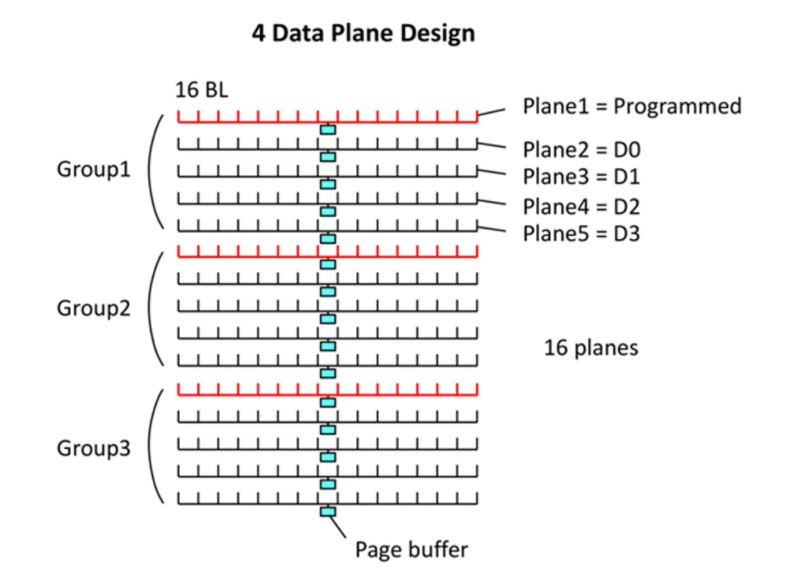

這是通過更小的裸片實現的,該裸片的尺寸約為 16 平面設計的尺寸的 37%(見下圖)。這里可以靈活制定,可以根據需要的速度減小芯片尺寸。

盡管如此,X-NAND 仍在較小的外形尺寸下提供了較高的并行度,就像在智能手機或 M.2 驅動硬盤中那樣。該公司還聲稱,可以在不影響耐用性或成本的情況下實現這一目標,而且消耗的功率非常少。

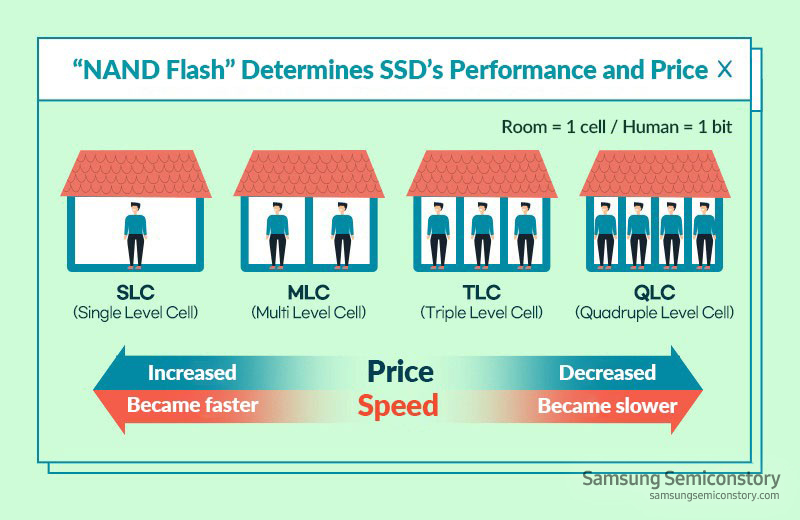

隨著 NAND 市場轉向價格更便宜但速度更慢的閃存以提高密度(例如,從 3 位 TLC 到 4 位 QLC),性能和耐用性從本質有所降低,且讀取和寫入延遲增加,這可能會降低順序寫入性能。這對于數據中心和 NAS 應用程序影響極大。

而消費級的 QLC 硬盤嚴重依賴 SLC 緩存,該緩存由部分以單位模式運行的本地閃存組成。但是,在企業工作負載中很難有足夠的時間讓你將寫入數據從 SLC 緩沖區遷移到主 QLC 存儲中。

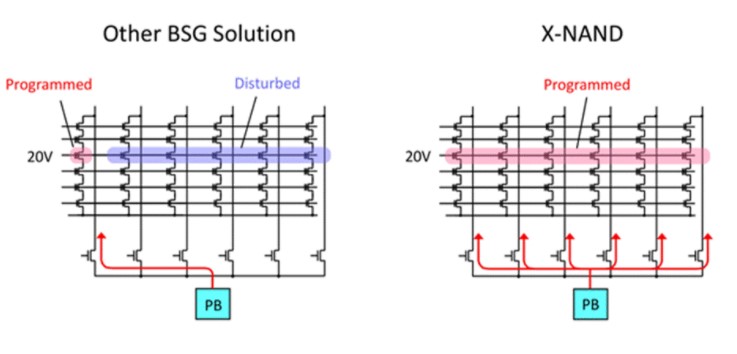

取而代之的是,X-NAND 通過同時進行 SLC 和 QLC 寫入模式(請參見下圖),為閃存提供了一種保持 SLC 性能的方法。

他指出,高密度閃存正以極快的速度增長,理由是(西數) Western Digital 到 2024 年將有 50% 的 QLC 份額。

他對 X-NAND 的目標是確保它使用傳統的 NAND 工藝,至少沒有結構上的變化,因此不會有額外的成本,以當前的 NAND 為基礎,采用快速采樣作為解決方案進行開發。

該策略旨在加速 QLC 的應用,特別是對于數據中心,因為 flash 的性能不再遠遠落后于 I/O 速度。此外,X-NAND 編程和擦除策略的設計,以大幅提高耐用性,使其壽命超過 QLC 閃存 (見下圖)。

X-NAND 通過將每個平面的 16KB 頁面緩沖區變為每個平面的 1KB 頁面緩沖區來實現這些特性,但平面的大小可以做到 16 倍。

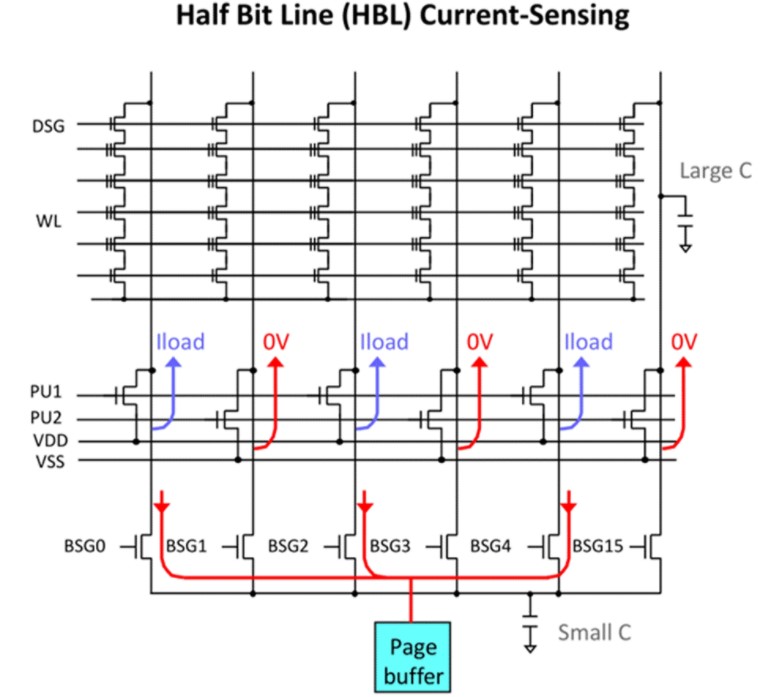

一個平面(plane)是閃存的最小單位,每個閃存 die 有一個或多個平面。頁緩沖區在總線和閃存之間保存傳輸中的數據,比如讀寫數據。閃速模被分割成包含位線或單元串的平面 (見上圖),因此平面分割可以減少位線的長度,這有助于提高性能。

而當 X-NAND 在讀取或驗證程序時,可通過屏蔽相鄰位線以減少相應的建立時間 (見下圖),這進一步增強了這種技術,使得寫入性能提高。

X-NAND 有六個主要特性 : 多位行寫、多平面 QLC 編程、程序掛起、多 bl 讀取、單鎖存 QLC 讀取,以及前面提到的 SLC/QLC 并行編程。根據實現的不同,這可以極大地提高程序吞吐量,因為可以在編程序列中使用多個平面。

使用多個存儲單位可允許同時進行 SLC 和 QLC 編程,確保 SLC 頁面永遠不會滿,同時數據可以以 SLC 速度編程到 QLC 頁面。程序可疑功能將允許使用內部共享的頁間緩沖區數據線或 I/O 總線來盡可能減少延遲。通過使用平面鎖存每個位線的讀取來改進讀取,并由于高電容而得以用非破壞性的方式像 DRAM 一樣刷新數據。

IT之家提醒,雖然愿景很美好,但該技術到實現可能仍需要不短的時間。

責任編輯:PSY

-

閃存

+關注

關注

16文章

1782瀏覽量

114895 -

NAND

+關注

關注

16文章

1681瀏覽量

136121 -

容量

+關注

關注

0文章

115瀏覽量

21216

發布評論請先 登錄

相關推薦

江波龍自研SLC NAND Flash累計出貨突破1億顆!

三星QLC第九代V-NAND量產啟動,引領AI時代數據存儲新紀元

三星電子量產1TB QLC第九代V-NAND

企業級QLC SSD普及元年,這家國產公司用前瞻性技術布局引領市場

蘋果將在iPhone中運用QLC NAND閃存技術

西部數據推出2TB QLC NAND閃存芯片,重塑數據存儲新紀元

美光232層QLC NAND現已量產

三星九代V-NAND閃存或月底量產,堆疊層數將達290層

長江存儲QLC閃存壽命實現重大突破

一文解析NAND的閃存接口ONFI

新 X-NAND 閃存架構詳解:QLC 的容量和定價 + SLC 的速度

新 X-NAND 閃存架構詳解:QLC 的容量和定價 + SLC 的速度

評論