U22是電可擦除ROM,用于存放AS下載后的數據,使得FPGA的程序段掉電也能得以保存,DATA端是數據讀取端,用于讀取ROM內數據。DCLK為時鐘端口,用于接收時鐘信號進行同步傳輸。nCS是片選端口,用于接收片選信號表示對該芯片進行通訊。ASDI為AS下載數據輸入端,用于接收AS下載數據。VCC與GND分別為電源端口與地端口,分別接3.3V與數字地。

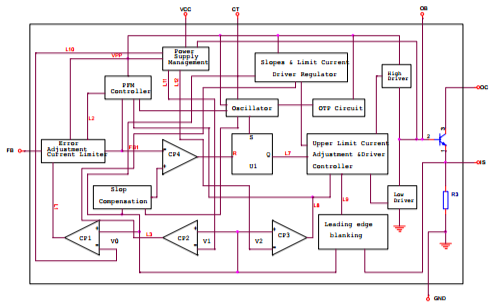

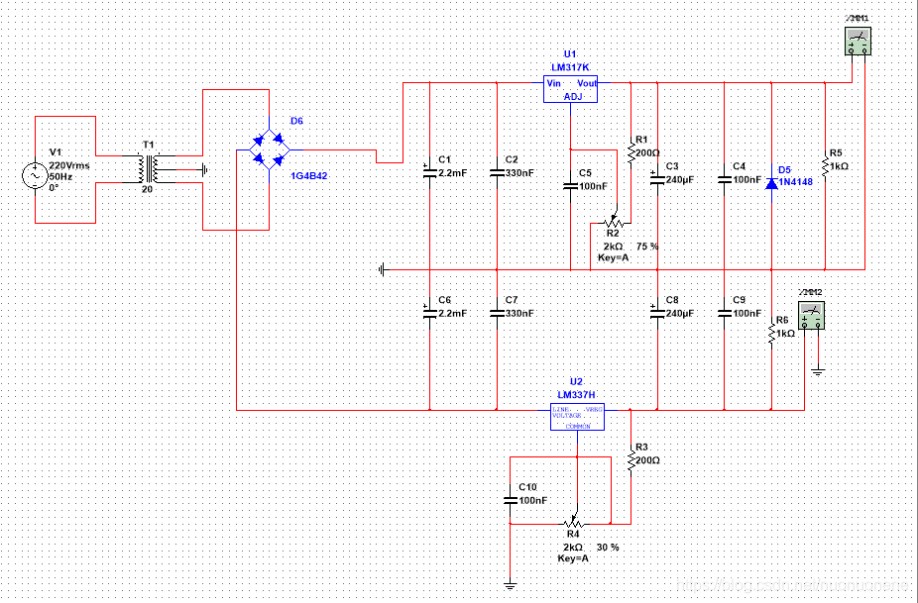

FPGA電源設計部分電路原理圖如圖5-1所示:

Header18X2為18排2列排陣,兩組排陣分別與PIN口、3.3V電源、數字地相連,提供了可動的機制,使得PIN口可根據需要用排線與目標相連,打到信號傳輸的目的。而3.3V電源以及數字地針口則可以根據需要,用排線為目標提供邏輯高電平或邏輯低電平。

U21D為FPGA芯片的時鐘信號接收部分,通過網絡標號“CLK0~3”與對應的時鐘信號端口相連。

U21C為FPGA芯片的供電及接地部分,含有“GND”字樣的是“地”端口,與數字地相連,VCCIO1~4為I/O口供電端口,采用3.3V電源供電,通過網絡標號“+3.3V”與3.3V電源端口相連。VCCA_PLL1、VCCA_PLL2、VCCINT為內部運算器和輸入緩沖區的供電端口,采用1.5V電源供電,通過網絡標號“+1.5V”與1.5V電源端口相連。

U21B為JTAG與AS下載部分,TMS、TCK、TD1、TD0分別為JATAG下載方式的模式選擇端、時鐘信號端、數據輸入端、數據輸出端。DATA0為AS下載的數據端口,MSEL0、MSEL1、nCE、nCEO、CONF_DONE、nCONFIG、nSTATUS端口按照典型接法相連。值得注意的是:無論AS還是JTAG都是通過JTAG標準通訊,AS下載一般是下載POF到PROM(flash)里,重新上電仍然可以加載,JTAG下載是通過JTAG口將sof文件直接下載到FPGA內,一般是臨時調試用的,掉電就丟失了。

責任編輯人:CC

-

FPGA

+關注

關注

1635文章

21837瀏覽量

608343 -

電源設計

+關注

關注

31文章

1545瀏覽量

66814 -

電路原理圖

+關注

關注

40文章

348瀏覽量

38572

發布評論請先 登錄

相關推薦

電源內部電子元件詳解(圖解)

USB接口電路圖解析

fpga最小系統設計和原理圖解析

電動機電氣聯控控制和單向直接啟動控制原理圖解析

鉦銘科電源芯片DK1203兼容RM6203方案原理圖解析及設計思路圖下載

FPGA電源設計部分電路原理圖解析

FPGA電源設計部分電路原理圖解析

評論