系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

系統考慮因素

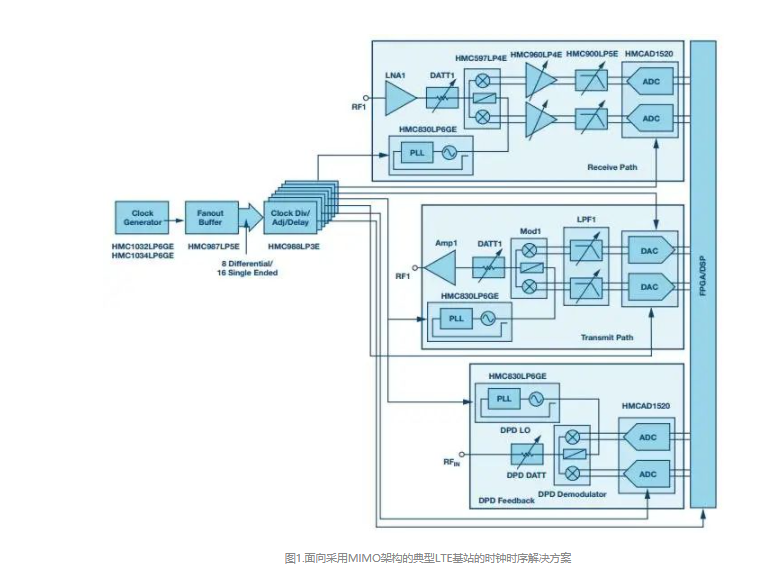

采用MIMO (多輸入多輸出)架構的典型LTE (長期演進)基站如圖1所示,該架構由多個發射器、接收器和DPD (數字預失真)反饋路徑構成。各種發射器/接收器組件(如數據轉換器(ADC/DAC))和本振(LO)要求采用低抖動參考時鐘以提高性能。其他基帶組件也要求各種頻率的時鐘源。

圖1.面向采用MIMO架構的典型LTE基站的時鐘時序解決方案

用于實現基站間同步的時鐘源一般來自GPS (全球定位系統)或CPRI (通用公共射頻接口)鏈路。這種源一般擁有優秀的長期頻率穩定性;但它要求把頻率轉換成所需的本地參考頻率,以實現良好的短期穩定性或抖動。高性能時鐘發生器可執行頻率轉換操作并提供低抖動時鐘信號,在此基礎上,這些信號可能會分配給各種基站組件。選擇最佳時鐘發生器至關重要,因為欠佳參考時鐘會增高LO相位噪聲,結果會提高發射/接收EVM(誤差矢量幅度)和系統SNR(信噪比)。高時鐘抖動和噪底也會影響數據轉換器,因為它會降低系統SNR并導致數據轉換器雜散輻射,從而進一步降低數據轉換器的SFDR(無雜散動態范圍)。結果,低性能時鐘源最終會降低系統容量和吞吐量。

時鐘發生器技術規格

盡管關于時鐘抖動的定義多種多樣,但在數據轉換器應用中,最合適的定義是相位抖動,其單位為時域ps rms或fs rms。相位抖動(PJBW)是通過時鐘信號相位噪聲在載波特定偏移范圍內的積分推導出來的抖動,計算公式如下:

fCLK為工作頻率;fMIN/fMAX表示目標帶寬,S(fCLK)表示SSB相位噪聲。積分帶寬的上限和下限(fMIN/fMAX)因具體應用而異,取決于設計敏感的相關頻譜成分。設計師的目標是選擇所需帶寬中的積分噪聲最低或者相位抖動最低的時鐘發生器。傳統上,時鐘發生器的特性是在12kHz至20MHz積分條件下測得的,這也是光學通信接口(如SONET)的指定要求。雖然這可能適用于一些數據轉換器應用,但要捕獲高速數據轉換器采樣時鐘的相關噪聲曲線,通常需要更寬的積分頻譜,具體是指20MHz以上。在測量相位噪聲時,噪聲遠遠偏離載波頻率。

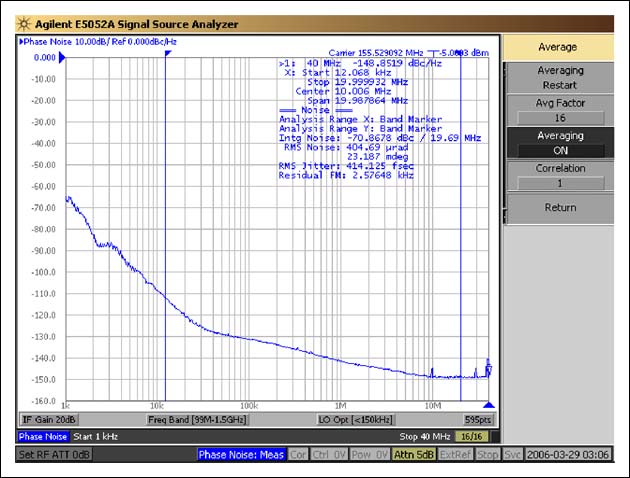

例如,數據轉換器采樣實際使用的時鐘頻率一般稱為遠遠偏離載波相位噪聲。該噪聲的限值通常稱為相位噪底,如圖2所示。該圖所示為ADI HMC1032LP6GE時鐘發生器的實際測量圖。相位噪底在數據轉換器應用中顯得格外重要,其原因在于轉換器SNR對其時鐘輸入端的寬帶噪聲極其敏感。當設計師評估時鐘發生器選項時,必須把相位噪底性能作為一項關鍵基準指標。

圖2.HMC1032LP6GE的相位噪聲和抖動性能

在圖2中,工作頻率為~160MHz時,積分相位抖動為~112fs rms,積分帶寬為12 kHz至20MHz,相位噪底為~–168dBc/Hz。這里值得注意的是,在為數據轉換器選擇最合適的時鐘發生器時,設計師不僅要參考頻域的相位噪聲測量值,同時也要參考時域的時鐘信號質量測量值,比如占空比、上升/下降時間。

數據轉換器的性能

為了描述時鐘噪聲對數據轉換器性能的影響,不妨將轉換器視為一個數字混頻器,二者僅存在一個細微差異。在混頻器中,LO的相位噪聲將添加到被混頻的信號中。在數據轉換器中,時鐘的相位噪聲將疊加到轉換輸出中,但受信號與時鐘頻率之比的抑制。時鐘抖動會導致采樣時間錯誤,表現為SNR下降。(時間抖動(T抖動)即是采樣時間中的rms誤差,單位為秒)

在有些應用中,可能會利用時鐘濾波器來減少時鐘信號的抖動,但這種方法存在顯著的缺陷:

濾波器雖然可能會消除時鐘信號的寬帶噪聲,但窄帶噪聲卻保持不變。

濾波器的輸出通常是一個類似于正弦波的慢壓擺率,會影響時鐘信號對時鐘路徑內部噪聲的敏感度。

濾波器消除了靈活性,無法更改時鐘頻率以實施多個采樣速率架構。

一種更實際的辦法是用一個擁有快壓擺率和高輸出驅動能力的低噪聲時鐘驅動器來最大化時鐘信號的斜率。這種方法可以優化性能,原因如下:

消除時鐘濾波器之后可以降低設計的復雜性,減少組件數量。

快速上升時間會抑制ADC時鐘路徑內部的噪聲。

窄帶和寬帶噪聲都可以通過選擇最佳時鐘源來優化。

可編程時鐘發生器可實現不同的采樣速率,因而可以增加解決方案對不同應用的適應能力。

超低時鐘噪底至關重要。遠遠偏離載波的時鐘抖動噪聲在ADC中采樣,并疊加進ADC數字輸出頻段中。該頻段受奈奎斯特頻率限制,后者定義為:

時鐘抖動通常由ADC時鐘信號的寬帶白噪底所主導。雖然ADC的SNR性能取決于多種因素,但時鐘信號寬帶抖動的影響由下式決定:

如上式所示,與混頻器不同,時鐘抖動的SNR貢獻與ADC模擬輸入頻率(fIN)成正比。

在驅動ADC時,時鐘噪聲受時鐘驅動器路徑中的帶寬限制,一般由ADC時鐘輸入電容主導。寬帶時鐘噪聲會調制較大的輸入信號并疊加進ADC輸出頻譜中。時鐘路徑的相位噪聲會降低輸出SNR性能,降幅與輸入信號的幅度和頻率成比例。最差情況是,在存在小信號的情況下還存在較大的高頻信號。

在現代無線電通信系統中,情況經常是,輸入端存在多個載波信號,然后在DSP中對各目標信號進行過濾,以匹配信號帶寬。在許多情況下,處于一個頻率的較大的無用信號會與時鐘噪聲混合,結果會降低ADC通帶中其他頻率下的可用SNR。在這種情況下,目標SNR為所需信號帶寬中的SNR。另外,上面的SNRJITTER值實際上是相對于最大信號(通常是一個無用信號或阻塞信號)的幅度的。

所需目標信號頻段中的輸出噪聲取決于:

在給定輸入頻率下,計算時鐘噪聲和較大無用信號條件下ADC性能的降幅;例如,計算ADC全帶寬中的SNR。

用所需信號帶寬與數據轉換器全帶寬之比計算所需信號帶寬中的SNR。

基于無用信號在滿量程以下的幅度增大該值。

步驟b的結果只是為了按以下方式修正前面所示的SNR等式:

SNRJITTER:在存在頻率為fin的大信號且采樣速率為fs的條件下,時鐘抖動在帶寬fBW中的SNR貢獻。

fIN:滿量程無用信號的輸入頻率,單位為Hz。

TJITTER:ADC時鐘的輸入抖動,單位為秒。

fBW:所需輸出信號的帶寬,單位為Hz。

fs:數據轉換器的采樣速率,單位為Hz。

SNRDC:數據轉換器在直流輸入條件下的SNR,單位為dB

最后,在存在滿量程阻塞信號的條件下,目標信號頻段中的最大可用SNR只是抖動與直流貢獻噪聲功率之和。

例如,對于ENOB為12.5位(直流)或者SNR為75dB的500MSPS數據轉換器,則在相當于采樣速率一半的帶寬中在250MHz的頻率下進行評估。如果目標信號的帶寬為5 MHz,則在接近直流時的可能SNR (帶寬為5MHz,時鐘完美)為75+10×log10 (250/5) =92 dB。

然而,ADC時鐘并不完美;根據圖3所示,在5MHz所需信號帶寬中的性能下降效應為x軸頻率下大無用信號輸入的函數。隨著抖動的增加,無用信號的影響變得更加嚴重,隨著輸入頻率的增加,情況同樣如此。如果無用信號的幅度下降,可用SNR將按比例增加。

圖3.ADC SNR與時鐘抖動和輸入頻率的關系

例如,如果在200MHz輸入下對一個滿量程5MHz無用W-CDMA信號進行采樣,采用一個高質量的500MHz時鐘(如HMC1034LP6GE),且運行于整數模式下時抖動為70 fs,則附近5MHz通道中的SNR約為91dB。相反,如果時鐘抖動降至500fs,則同一數據轉換器和信號只會表現出81dB的SNR,相當于性能下降10dB。

在400MHz下把同一信號輸入數據轉換器,70fs的時鐘會產生88dB的SNR。類似地,在500fs的時鐘下,SNR值會降至僅75dB。

-

gps

+關注

關注

22文章

2894瀏覽量

166181 -

發生器

+關注

關注

4文章

1368瀏覽量

61677 -

MIMO

+關注

關注

12文章

594瀏覽量

76824

發布評論請先 登錄

相關推薦

MAX9489/MAX9471多輸出時鐘發生器構建集成時鐘源

高精度時鐘發生器MAX945x的元件選擇和性能測試

Cypress時鐘發生器的分類,它有哪些應用

時鐘發生器性能對數據轉換器的影響

如何選擇合適的時鐘發生器

如何選擇合適的時鐘發生器

評論