1.Verilog基礎語法

1.1 可綜合模塊

以module為單元,具體實現如下

1.1.1 時序邏輯

以異步觸發的D觸發器為例,時序邏輯在always塊里實現

主要注意點:

1. 聲明模塊時,輸入變量一定是wire類型。

2. 聲明模塊時,輸出變量可以是wire,也可以是reg, reg變量只能在always塊中賦值。

3. 敏感列表既可以是邊沿觸發,也可以是電平觸發。

4. 沿觸發的邏輯里,一定采用的是非阻塞觸發<=。

1.1.2 組合邏輯

以數據選擇器為例,組合邏輯通常使用assign語句賦值

主要注意點:

1. sel = 0時,c = a;sel = 1時,c =b,即二選一數據選擇器。四選一則有兩個選擇端,四個輸入端,八選一則是三個選擇端,八個輸入端。

2. wire 變量一定要用連續賦值語句賦值,而且必須用阻塞賦值。

1.2 仿真模塊

仿真模塊和可綜合模塊的區別:

可綜合模塊最終生成的bit文件會燒錄進芯片運行,而仿真模塊編譯過后是在仿真軟件(例如modelsim)上運行的。仿真模塊是基于可綜合模塊進行例化,并通過仿真軟件的模擬,可以初步驗證我們寫的可綜合模塊的實現現象。

以計數器為例,可綜合模塊如下:

基于以上可綜合模塊的仿真模塊如下:

1. 仿真的模塊聲明不需要輸入列表。

3. 例化模塊時,如果原始模塊是輸出變量,則括號內必須【wire變量】。

HDL常見例子

2.1 譯碼器

2.1.1 可綜合模塊(case語句)

此模塊用case實現了一個數據選擇的功能,先產生了一個8位計數器,通過判斷計數器的值來輸出不同的取值,當計數器計數到1時,o_data和o_dv分別輸出5和1,當計數器為2時,輸出7和1,其余均輸出0。(Note:Case語句常常運用于狀態機中狀態的判斷)

Case語句注意點:

必須有default語句,否則會形成鎖存器

2.1.2 仿真模塊

2.2狀態機

由于FPGA內部語句塊都是并行運行的,當我們希望FPGA按照順序執行我們的語句時,就會用到狀態機。

下面例子是使用狀態機模擬的一個簡單的自動售貨機,該售貨機中的商品 2.5 元一件,每次投幣既能投入 1 元, 也能投入 0.5 元,當投入 3 元時,需要設定找零。

2.2.1 狀態圖

2.2.2 可綜合模塊(2段式狀態機)

2.2.3 仿真模塊

2.2.4 仿真腳本

仿真腳本可以省去人工操作modelsim軟件圖形頁面的步驟,運行腳本,modelsim可以根據腳本命令自動運行包括創建工作目錄,編譯文件,啟動仿真等步驟,以下是本例中的仿真腳本。

仿真腳本編寫好后,只需要進入仿真軟件(本例使用的是modelsim),改變當前路徑到腳本保存的路徑,然后在modelsim命令行輸入 do [腳本文件名]即可。

仿真結果:

2.2.5 上板測試

上板測試對原來的條件做了一定改動更方便觀測結果,輸入和輸出分別使用的按鍵和LED燈,測試版使用的是Anlogic的EF3L40CG332B_DEV,實現的功能如下:

① 在開發板上完成自動售貨機的實驗,投幣的動作通過按鍵實現, 當按一次按鍵(按下到抬起算一次),算作投幣一次;

② 按鍵有兩個,按下分別代表 5 毛和 1 元,可樂售價 2.5 元;

③ 當投入總金額為 5 毛時, led 燈亮一個,投入總金額為 1 元時, led 燈亮兩個, 投入總金額為 1.5 元時, led 燈亮三個, 投入總金額為 2 元時, led 亮四個, 用單向流水燈效果充當出可樂并且不找零的情況,用雙向流水燈效果充當既出可樂又找零的情況。流水燈持續十秒后熄滅,狀態回到初始狀態。

重新設計狀態圖如下:

代碼詳見工程fsm_key,筆記不再贅述,此次筆記主要記錄關于頂層模塊和例化的相關知識點:

工程目錄如下所示:

各模塊之間的關系是:

頂層文件是fsm.v,在fsm.v中調用了模塊led_water_single,led_Water_double和key_debounce,這三個模塊的功能分別是單向流水燈,雙向流水燈和按鍵消抖。想在頂層文件中調用對應的模塊需要在頂層文件中對相應的模塊進行例化,以單向流水燈為例。

單向流水燈的聲明如下:

(具體功能實現代碼略,如有需要,請登錄www.fortune-co.com留言)

那么在fsm.v中例化方法如下:

括號外的信號是對應的聲明信號;括號內的信號是從fsm模塊中傳入的信號,該信號名稱可以自定義。

整個工程的框架如下:(由于本實驗沒有另外寫一個總的TOP文件,而是將例化和狀態機信號處理都放在了fsm模塊中,因此top層和狀態機模塊都標注的是fsm)

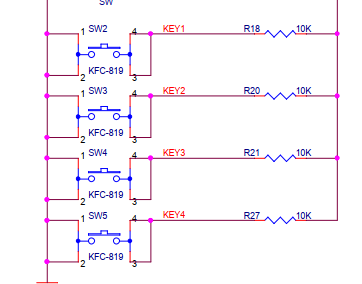

其中key05,key10,就是從外界接入的信號,led[7:0]即輸出信號。接入信號我們要引到對應的按鍵,可以參考EF3L40CG332B_DEV的原理圖

SW2和SW3對應的FPGA的管腳分別是R19和R20,同理可查,八個led的對應腳,并寫出相應的管腳約束文件。

管腳約束文件寫完后,在可綜合模塊頂層文件中的輸入輸出信號就會對應到相應的物理輸入輸出,也可以使用圖形頁面設置。

完成后編譯下載到板子上觀測現象。

在本次實驗的過程中也發生了一個編程錯誤問題,剛編寫完上板測試時發現結果和預想的有差異,具體錯處在輸入3元進入雙向流水燈的狀態時,雙向流水燈正向流水正常,當反向流水時,在倒數第二個燈會卡住,然后反復亮滅倒數一二個燈,沒法完成反向流水。

由于第一次正向流水是正常的,因此推測是在反向流水時有條件判斷錯誤使得反向流水無法正常運行,進入到led_water_double模塊關于反向流水燈的操作模塊,經查驗發現是設置翻轉標志的時候判斷條件寫錯了。

判斷條件應該是led == 8’b1111_1110,更改后,實驗現象符合預期要求。

fqj

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603795 -

輸出信號

+關注

關注

0文章

283瀏覽量

11874

發布評論請先 登錄

相關推薦

玩轉FPGA必備的基礎知識

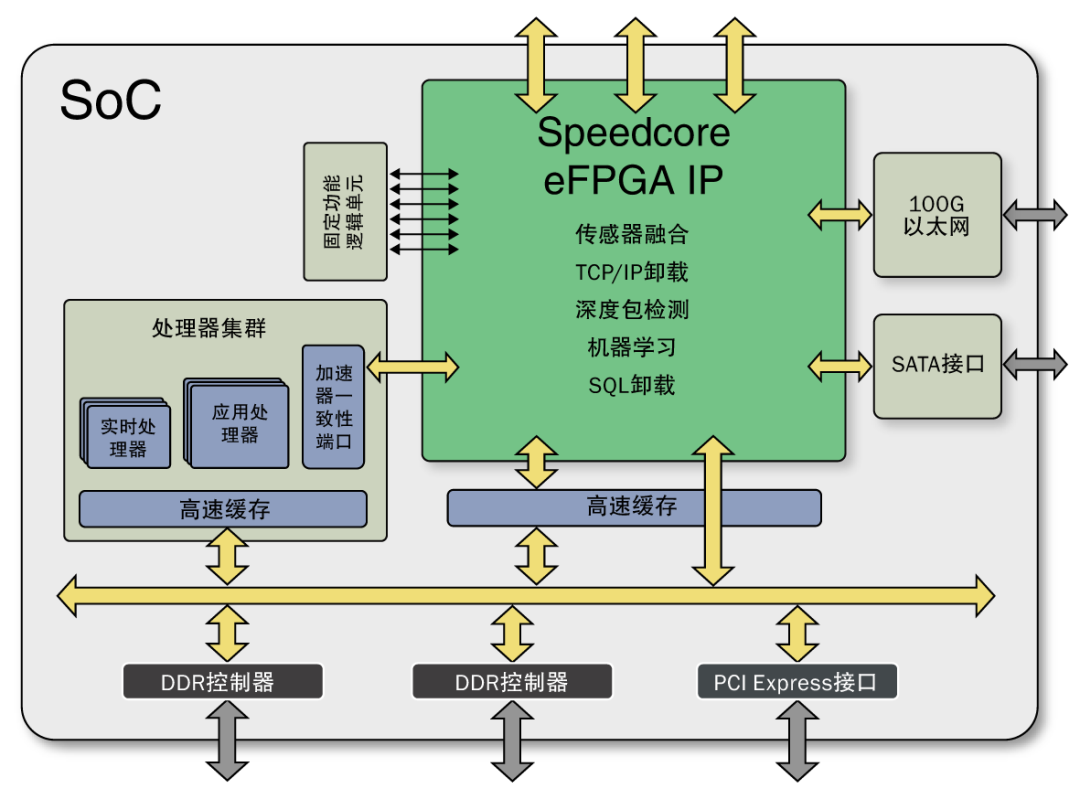

Achronix Speedcore eFPGA的特性和功能

詳解FPGA的基本結構

【《大語言模型應用指南》閱讀體驗】+ 基礎篇

淺談PUF技術如何保護知識產權

一文了解FPGA技術知識

FPGA知識詳解之基礎篇的技術分享

FPGA知識詳解之基礎篇的技術分享

評論