針對引腳的輸入輸出緩沖(I/O buffer)電路設(shè)計,也可以稱為輸入輸出接口(I/O interface)電路設(shè)計,是一顆完整芯片設(shè)計中不可或缺的組成部分,但是詳細(xì)論述其設(shè)計規(guī)則的文章或者著作在國內(nèi)卻比較鮮見,這對初學(xué)者或者沒有這方面經(jīng)驗的工程師無疑會造成困惑。本文以CMOS工藝為例,較全面的論述I/O緩沖電路設(shè)計中各種考慮,可以作為芯片引腳輸入輸出電路設(shè)計的一個參考。

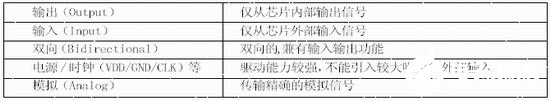

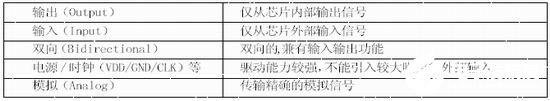

根據(jù)I/O緩沖電路應(yīng)用目標(biāo)的不同,可將其分為輸入、輸出等幾類,詳見表1。

表1 I/O緩沖電路的分類

輸出緩沖

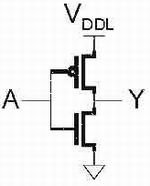

輸出緩沖電路的功能要求能夠驅(qū)動大的片外負(fù)載,通常為2~50pF,并且提供適當(dāng)?shù)纳仙?下降時間。一組連續(xù)的大尺寸的緩沖器(buffer)對驅(qū)動能力的提高是有益的。大尺寸的管子容易受閂鎖效應(yīng)(latch-up)的影響,在版圖設(shè)計時建議采用保護環(huán)(Guardrings)保護以避免閂鎖效應(yīng),如圖1-1所示。在圖中,用P+作為內(nèi)保護環(huán),而N+作為外保護環(huán)(In n-well)。

圖1-1緩沖器

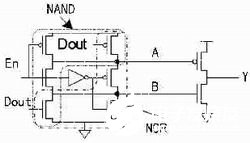

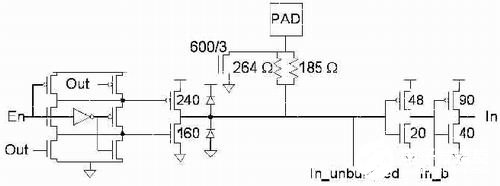

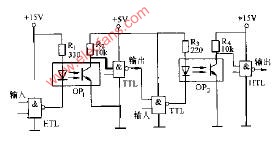

一種常見的輸出電路如圖1-2所示,En是輸出電路的使能信號,Dout是輸出數(shù)據(jù),MOS管組合的功能如圖中所示。當(dāng)En為低而Dout有效時,A、B均為高電平,輸出Y為低,且由外向里看為高阻抗?fàn)顟B(tài),如果Dout未定,則Y為高阻。需要注意的是,最后輸出級的管子尺寸要大到能夠提供足夠的電流源或電流沉并且減少延遲時間。其負(fù)面影響是電流變化率(di/dt)變大而使穿過輸出點到封裝的壓焊線上的L(di/dt)噪聲增大,從而導(dǎo)致較大的片上噪聲。

圖1-2常用的輸出緩沖電路

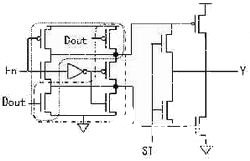

在高性能的芯片中,如32位的微處理器,如果多個I/O輸出驅(qū)動電路工作狀態(tài)相似時,L(di/dt)噪聲可能逐步增強,會影響芯片速度。圖1-3通過加入一個閘控制信號(ST),并結(jié)合時序的控制,可以減小L(di/dt)噪聲。

圖1-3降低L(di/dt)噪聲的電路

輸入緩沖

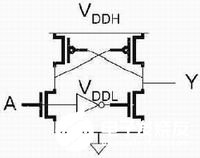

輸入數(shù)字信號電平如果和芯片內(nèi)部需要電平一致,就需要升壓或者降壓電路進行調(diào)整。注意這個升壓/降壓是芯片電壓可以提供的電平,否則可能需要DC/DC電路來完成。如芯片供電電壓為3.3V和1.8V,某外部信號供電電平為1.8V,而芯片內(nèi)部使用該信號的供電電平為3.3V,就需要降壓。電壓轉(zhuǎn)換電路如圖2-1所示,分別將高或低的片外電平進行轉(zhuǎn)換以適合片內(nèi)使用,圖2-1(a)為升壓電路,圖2-1(b)為降壓電路,VDDH接高電平,VDDL接低電平。

圖2-1(a)升壓電路 圖2-1(b)降壓電路

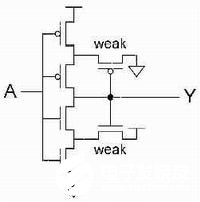

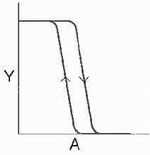

輸入緩沖電路的另外一個作用是對噪聲的濾除。對于噪聲的危害,噪聲寄生在信號電平上可能造成比較器的誤判就是一個突出的例子。施密特觸發(fā)器利用磁滯效應(yīng)的原理對消除這種噪聲干擾有很好的效果。圖2-2是施密特觸發(fā)器的結(jié)構(gòu)和磁滯現(xiàn)象中的磁滯回路。這樣,即使重疊噪聲(noise)混入電路,該噪聲如果沒有超越磁滯寬度的話,輸出就不會產(chǎn)生多次拉動(multi pull trigger)的誤動作,只會出現(xiàn)與磁滯寬度相同的響應(yīng)延遲。

圖2-2(a)施密特觸發(fā)器 圖2-2(b)磁滯現(xiàn)象中的磁滯回路

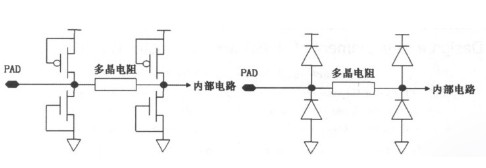

靜電放電保護也是輸入緩沖電路的一個基本功能,通常用二極管鉗位,如果電壓過高將會使其導(dǎo)通,使大電流泄走,在后文的靜電放電保護部分會有更多討論。

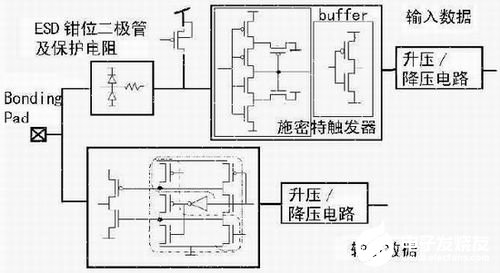

雙向緩沖

雙向緩沖,即兼有輸入輸出功能的雙向緩沖電路,輸出時有三態(tài)驅(qū)動,可以使用使能(enable)信號來區(qū)分輸入輸出狀態(tài)。并且可以優(yōu)化三態(tài)輸出以避免使用大尺寸的管子。根據(jù)前面對輸入和輸出緩沖的單獨描述,組合起來并用使能信號控制,得出雙向緩沖電路如圖3-1所示。

圖3-1雙向緩沖電路的結(jié)構(gòu)框圖

圖3-2給出了一個0.6μm工藝的雙向I/O緩沖簡化電路。圖3-3是其版圖。該電路及版圖設(shè)計包括了保護電阻、保護二極管、保護環(huán)、場氧鉗制(Field oxide clamps)等。

圖3-2一個I/O緩沖的簡化電路

圖3-3示例的版圖

模擬信號引腳接口電路

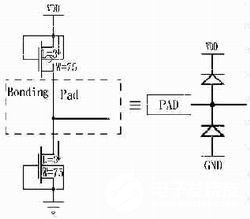

模擬信號引腳接口電路是直接將模擬信號精確的輸入或輸出,故無須額外的緩沖電路(buffer),而且保護電路也不可對電壓/電流信號有所扭曲。圖4-1給出了一種模擬信號引腳接口電路的結(jié)構(gòu)和等效電路。三極管的短接方式實際等效為二極管,如果工藝庫提供專門的二極管,則無須這樣的替代。

圖4-1模擬I/O的結(jié)構(gòu)和等效電路(以TMSC0.35μm工藝為例)

電源,時鐘等信號的引腳電路與之類似。有時還需要串接一個保護電阻,其作用是避免大電流對二極管的沖擊,而壞處是可能引入熱噪聲。對于輸入緩沖,保護電阻的值應(yīng)該設(shè)計得較大,如200到2000歐姆;電源、時鐘信號的緩沖電路則選擇小一些。

ESD保護

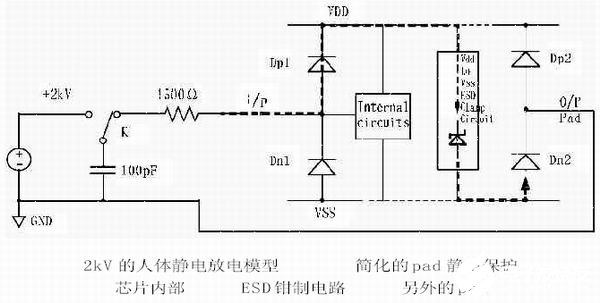

通常,穿尼龍制品的人體靜電可能達到21,000V的高壓,750V左右的放電可以產(chǎn)生可見火花,而僅10V左右的電壓就可能毀壞沒有靜電保護的芯片。在正常工作情況下,靜電放電保護電路設(shè)計,除對靜電放電保護外,還有柵氧化層(Gate Oxide)的可靠性,避免額外漏電等問題;有省電模式的芯片,靜電放電電路還須考慮在省電模式時,避免額外漏電流對內(nèi)部芯片產(chǎn)生誤操作。在靜電放電發(fā)生時,保護電路必須保護內(nèi)部電路不受放電電流傷害。此外,還需要考慮靜電放電保護電路的低持有電壓(Holding Voltage)特性可能帶來的閂鎖效應(yīng)(Latch-up)或類似閉鎖效應(yīng)(Latch-up-Like)。這也使得高性能的靜電放電電路設(shè)計變得復(fù)雜,如果要詳細(xì)討論這些問題需要單獨的論述。

靜電放電保護標(biāo)準(zhǔn)有常用的工業(yè)標(biāo)準(zhǔn)(+/-2000V),IEC61000-4-2標(biāo)準(zhǔn)(+/-15000V,+/-8000V)等,可以根據(jù)芯片工作環(huán)境做相應(yīng)的保護設(shè)計。

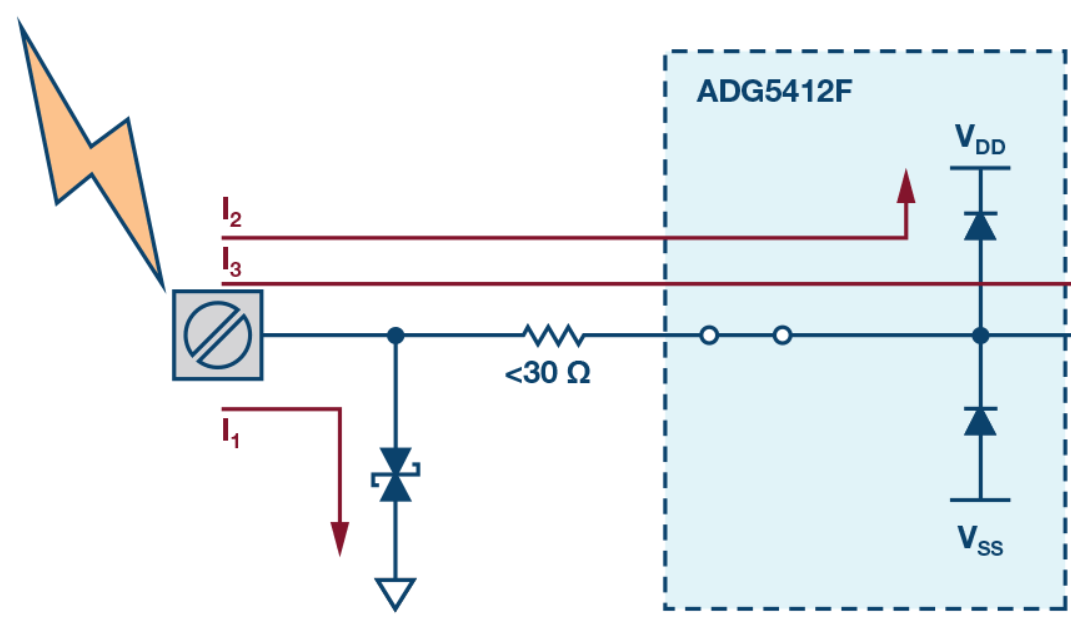

圖5-1給出了人體靜電放電模型及靜電放電保護電路工作時電流回路示意圖。高壓將鉗位二極管導(dǎo)通,電流經(jīng)VDD,靜電放電鉗制電路等泄入地端,避免內(nèi)部電路受損。

圖5-1芯片的ESD保護電路模型

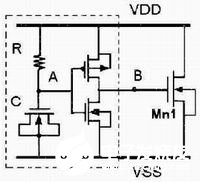

一種常見的ESD鉗制電路如圖5-2所示。芯片正常工作時,A點電位為高,B點為低,Mn1不導(dǎo)通。當(dāng)瞬間的靜電高壓沖擊到來時,圖5-1中的二極管導(dǎo)通,VDD為靜電高壓,RC電路對高壓有延遲,故A點電壓較VDD上升慢,而使反相器PMOS管導(dǎo)通,B點電壓上升,使大尺寸的Mn1管導(dǎo)通,靜電電流被泄載掉。需要注意,人體靜電放電上升時間為10ns量級,芯片啟動為ms量級,ESD鉗制電路的RC時間常數(shù)應(yīng)在兩者之間,通常可以取0.1μs到1μs量級。另外,高壓對電路沖擊的效應(yīng)是較難模擬的,ESD電路的版圖設(shè)計需要特別小心。

圖5-2RC電路結(jié)構(gòu)的ESD鉗制電路

ESD保護設(shè)計隨著CMOS工藝的演進而越來越困難,迄今已有六百多件ESD相關(guān)的美國專利。而且,ESD更應(yīng)當(dāng)從芯片全局考慮,而不只是Input PAD,Output PAD,或Power PAD的問題。各個PAD都有很好的ESD防護能力,并不說明整個芯片的ESD防護能力就一定好。采用整片(whole-chip)防護結(jié)構(gòu)是一個好的選擇,也能節(jié)省I/O PAD上ESD元件的面積。整片ESD防護結(jié)構(gòu)同樣是各大IC設(shè)計公司專利競爭的焦點,所以,IC設(shè)計公司應(yīng)該特別注意這些技術(shù)的發(fā)展。

責(zé)任編輯:gt

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423142 -

ESD

+關(guān)注

關(guān)注

48文章

2029瀏覽量

172929 -

緩沖器

+關(guān)注

關(guān)注

6文章

1921瀏覽量

45473

發(fā)布評論請先 登錄

相關(guān)推薦

CMOS電路中ESD保護結(jié)構(gòu)的設(shè)計要求

求助,關(guān)于LM386芯片內(nèi)ESD保護電路設(shè)計和引腳分配情況求解

系統(tǒng)輸入輸出保護電路怎么實現(xiàn)

如何設(shè)計ESD保護電路?

如何設(shè)計系統(tǒng)輸入輸出保護電路?解決模擬輸入IEC系統(tǒng)保護問題!

基于CMOS電路的ESD保護設(shè)計

芯片輸入輸出緩沖電路和ESD保護電路的應(yīng)用設(shè)計

芯片輸入輸出緩沖電路和ESD保護電路的應(yīng)用設(shè)計

芯片輸入輸出緩沖電路和ESD保護電路的應(yīng)用設(shè)計

評論