首發(fā):GiantPandaCV

作者:ybai62868

【GiantPandaCV導(dǎo)語】

這篇文章為大家介紹了一下面向低功耗AI芯片上的神經(jīng)網(wǎng)絡(luò)設(shè)計(jì),隨著這幾年神經(jīng)網(wǎng)絡(luò)和硬件(CPU,GPU,FPGA,ASIC)的迅猛發(fā)展,深度學(xué)習(xí)在包括互聯(lián)網(wǎng),自動(dòng)駕駛,金融,安防等很多行業(yè)都得到了廣泛的應(yīng)用。然而當(dāng)我們真正在實(shí)際部署深度學(xué)習(xí)應(yīng)用的時(shí)候,許多場景例如無人駕駛對設(shè)備在功耗,成本,散熱性等方面都有額外的限制,導(dǎo)致了無法大規(guī)模應(yīng)用深度學(xué)習(xí)解決方案。感興趣的同學(xué)可以了解一下有關(guān)如何面向AI芯片來設(shè)計(jì)神經(jīng)網(wǎng)絡(luò)。

一、目前算法和硬件co-design的一個(gè)大背景

從硬件方面來看,我們都知道,深度神經(jīng)網(wǎng)絡(luò)中的計(jì)算都是大量的稠密型運(yùn)算。那么,當(dāng)前的硬件發(fā)展其實(shí)已經(jīng)很難滿足這些稠密型的運(yùn)算需求了。那么,設(shè)計(jì)低功耗,低成本,高性能的硬件計(jì)算部署平臺就成為了當(dāng)務(wù)之急。

對于算法來說,其實(shí)在某些公開的數(shù)據(jù)集上,已經(jīng)有很多非常不錯(cuò)的算法了,但是這些算法僅僅是針對特定數(shù)據(jù)集(瘋狂刷點(diǎn)...)而在真實(shí)的業(yè)務(wù)場景下,這些算法有時(shí)候就并不一定能表現(xiàn)的非常出色。這個(gè)時(shí)候,我們就要去設(shè)計(jì)那些不僅是針對一些public數(shù)據(jù)集能夠表現(xiàn)的比較comparable的,同時(shí)在一些特定的業(yè)務(wù)場景下,也要能夠表現(xiàn)令人滿意的算法。

二、當(dāng)前AI芯片的發(fā)展?fàn)顩r

總的來說,目前的硬件家族可以被分為兩個(gè)大類。

一大類是以通用需求為主的:CPU, GPU

另一大類以特殊用途為主的:FPGA, ASIC

先有一個(gè)大體的宏觀概念。然后在看看看算法和這些硬件是怎么結(jié)合的。

早期的代碼都是跑在CPU上的,比如說,我們知道的LeNet,那會GPU并不像現(xiàn)在這么盛行。直到ImageNet的冠軍Alex把網(wǎng)絡(luò)跑到了GPU上。這個(gè)時(shí)候,大家都開始使用GPU作為自己的訓(xùn)練平臺。其實(shí),CPU并不能非常高效的去運(yùn)行我們需要的神經(jīng)網(wǎng)絡(luò)。因?yàn)镃PU的運(yùn)行方式是以串行為主,并且CPU上有很多操作都是為了優(yōu)化多級緩存,更加偏向的是對于數(shù)據(jù)IO處理的的能力。而這些方面的設(shè)計(jì)對于神經(jīng)網(wǎng)絡(luò)來說都是多余的。

那么,什么樣的硬件結(jié)構(gòu)設(shè)計(jì)才能更加滿足神經(jīng)網(wǎng)絡(luò)的特性呢?

其實(shí),這個(gè)問題上,超哥講的很好。究竟什么樣的硬件結(jié)構(gòu)更加適合神經(jīng)網(wǎng)絡(luò),還得從神經(jīng)網(wǎng)絡(luò)自身的特性來分析。

就拿我們熟悉的全連接層來講,比如說,現(xiàn)在第i層的神經(jīng)元和第i+1層的神經(jīng)元之間是以全連接的方式溝通的,那么溝通每個(gè)神經(jīng)元的運(yùn)算實(shí)際上是非常簡單的乘法和加法。那么在網(wǎng)絡(luò)進(jìn)行一次前向運(yùn)算的過程中,硬件上能夠支持乘法和加法的運(yùn)算單元越多,那么此時(shí)就能夠承載下更深的網(wǎng)絡(luò)。

對于同一層上的不同神經(jīng)元來說,我們需要他們能夠相互獨(dú)立的完成各自的運(yùn)算,從這點(diǎn)來看,神經(jīng)網(wǎng)絡(luò)具有大規(guī)模的并行性。

不論是在網(wǎng)絡(luò)進(jìn)行前向計(jì)算還是反向計(jì)算的過程中,都會產(chǎn)生很多的中間計(jì)算結(jié)果。而這些中間結(jié)果并不是每個(gè)都會被復(fù)用,要能放下在網(wǎng)絡(luò)運(yùn)算過程中產(chǎn)生的中間結(jié)果,就需要我們的硬件有足夠的帶寬。對于一個(gè)理想的設(shè)備來說,它應(yīng)該有比較大的片上存儲,并且?guī)捯惨銐颉_@個(gè)時(shí)候,對于屬于的圖片信息(以視覺任務(wù)為主)和網(wǎng)絡(luò)的權(quán)重才能有足夠的空間來做存儲。就是說要它充分的利用片上資源,減少片外的訪存。

其實(shí),在我們對一個(gè)網(wǎng)絡(luò)進(jìn)行train和inference的過程中,網(wǎng)絡(luò)本身對于計(jì)算精度并沒有我們想象的那么敏感。那么,為了能夠存下更多的權(quán)重(deep的網(wǎng)絡(luò)),我們可以使用那些比較簡單的數(shù)據(jù)類型,比如說,int8,fp16。因此,這些年來,大家對于CPU+(GPU, FPGA, TPU, ASIC)這些硬件所組成的異構(gòu)計(jì)算平臺。

第一種組合:CPU+GPU

其實(shí),在我們平時(shí)做實(shí)驗(yàn),訓(xùn)練模型的過程中,用的最多的就是CPU+GPU這樣的組合。

借助現(xiàn)有的非常成熟的深度學(xué)習(xí)框架(mxnet,pytorch,tensorflow等),我們就能非常方便和容易的完成開發(fā)。

優(yōu)點(diǎn):編程容易,運(yùn)算力和吞吐量大。

缺點(diǎn):GPU的功耗高,延遲大,部署實(shí)際的AI產(chǎn)品,沒人會用服務(wù)器級別的GPU。

第二種組合:CPU+FPGA

這種組合方式的功耗相比CPU+GPU就要低很多。但是,對于FPGA的開發(fā)難度則會大很多。

優(yōu)點(diǎn):功耗低,方便落地

缺點(diǎn):編程開發(fā)難度大,需要學(xué)習(xí)專用的硬件語言來支持相應(yīng)的設(shè)備

第三種組合:CPU+ASIC

ASIC指的的是按照產(chǎn)品需求不同而定制化的特殊規(guī)格集成電路,由特定使用者要求和特定電子系統(tǒng)的需要而設(shè)計(jì),制造。也就是說,ASIC在特定功能上進(jìn)行了專項(xiàng)強(qiáng)化,可以根據(jù)需要進(jìn)行復(fù)雜的設(shè)計(jì),從而實(shí)現(xiàn)更高的處理速度和更低的功耗。那么,ASIC的生產(chǎn)成本就會更高!

那么其實(shí),可以對上面講的這些硬件進(jìn)行一個(gè)歸類,CPU,GPU叫做通用性芯片。ASIC叫做定制化芯片,而FPGA叫做半定制化芯片。

Google的TPU就是采用了定制化芯片的設(shè)計(jì)。

其中TPUv1采用了大量的乘法單元,有256x256個(gè)8位乘法器。片上有28MB的緩存,能夠存儲網(wǎng)絡(luò)的參數(shù)和輸入。同時(shí),TPU上的數(shù)據(jù)和指令

說白了,就是將訓(xùn)練好的model拿來定點(diǎn)化做inference。

TPUv2支持了train的功能,并且也能夠使用fp進(jìn)行訓(xùn)練。

講了這三種組合,其實(shí)如果就拿inference來說,F(xiàn)PGA才是合適的硬件。

各種硬件用于前向推理的優(yōu)缺點(diǎn)

現(xiàn)在來看,要想設(shè)計(jì)一款適合深度神經(jīng)網(wǎng)絡(luò)的芯片,我們需要其具備什么特性呢?

支持主流的視覺任務(wù)(inference),不僅僅要支持int8,還要支持fp。

high performance,low engergy,low cost

方便開發(fā)和支持主流的DL框架

這里要提的就是地平線自己設(shè)計(jì)的BPU,它也屬于ASIC的范疇。并且支持主流的CV任務(wù)。

BPU最大的特點(diǎn)就是設(shè)計(jì)了彈性的Tensor Core,它能夠?qū)⒛切τ趇mage來說所需要的op硬件化,這些op包括CNN中常見的(卷積,池化等),從而非常高效的去執(zhí)行這些操作。中間通過一個(gè)叫做數(shù)據(jù)路由橋(Data Routing Bridge)的結(jié)構(gòu)從片上來讀取數(shù)據(jù),負(fù)責(zé)數(shù)據(jù)的傳輸和調(diào)度。同時(shí),整個(gè)數(shù)據(jù)存儲資源和計(jì)算資源都可以通過編輯器輸出的指令來執(zhí)行調(diào)度,從而方便實(shí)現(xiàn)各種算法,各種model的結(jié)構(gòu),和各種不同的任務(wù)。

三,如何從算法層面設(shè)計(jì)高效的神經(jīng)網(wǎng)絡(luò)

從AI的解決方案來看存在兩種方式:

云端 AI

前端 AI

云端 AI 說的就是把我們的計(jì)算放在遠(yuǎn)程服務(wù)器上去執(zhí)行,然后把最終的計(jì)算結(jié)果傳回本地,這就要求我們的設(shè)備時(shí)時(shí)刻刻聯(lián)網(wǎng),并且存在很大的安全問題和計(jì)算傳輸延遲問題,也就是我們通常所說的通信代價(jià)。

前端 AI 說的就是設(shè)備本身就能進(jìn)行運(yùn)算,不需要聯(lián)網(wǎng)。那么在安全性,實(shí)時(shí)性,適用性方面都要?jiǎng)龠^云端 AI 。但是,他們在功耗,計(jì)算,內(nèi)存存儲等方面有很多受限。

其實(shí)關(guān)于AI 產(chǎn)品落地,還是回到上面硬件部分講過的內(nèi)容,如何去尋求一套 低功耗,高性能,低成本的解決方案。

這里拿IPC和TX2進(jìn)行比較來說明這個(gè)問題。

IPC通過網(wǎng)線來供電,功耗非常低,只有12.5w,TX2的功耗是10-15w。TX2雖然在算力和計(jì)算成本方面都要?jiǎng)龠^IPC,但是TX2的價(jià)位對于嵌入式的方案是不能接受的。。。

那么,要想做好前端AI方案(針對embedd AI)設(shè)備來說,我們就要在給定功耗(12.5w)和算力(IPC最大能力)的情況下,去優(yōu)化我們的算法和神經(jīng)網(wǎng)絡(luò)模型,來達(dá)到符合場景落地的需要。

那么,說白了,我們最終加速網(wǎng)絡(luò)的目的就是,在網(wǎng)絡(luò)保持不錯(cuò)性能的的前提下,盡量去降低計(jì)算代價(jià)和帶寬的需求。

關(guān)于網(wǎng)絡(luò)加速方面看songhan的,補(bǔ)。我在cs231n上學(xué)到的東西。

網(wǎng)絡(luò)量化,網(wǎng)絡(luò)剪枝,參數(shù)共享,蒸餾以及模型結(jié)構(gòu)優(yōu)化。

在工業(yè)界,用的最多的就是網(wǎng)絡(luò)量化和模型結(jié)構(gòu)化的方法。

下面重點(diǎn)來講講這些方法:

3.1 量化

量化其實(shí)說的就是離散化。將我們原先連續(xù)變化的量通過近似從而達(dá)到離散的目的。

神經(jīng)網(wǎng)絡(luò)的量化,值得就是將原先用浮點(diǎn)數(shù)表示的情況改成用更低的bit,從而繼續(xù)完成原先浮點(diǎn)數(shù)能夠完成的訓(xùn)練和測試。

前面再將神經(jīng)網(wǎng)絡(luò)特性的時(shí)候,我們也提到了網(wǎng)絡(luò)本身對于計(jì)算精度并沒有我們想象的那么敏感。所以,比較常用的方法,就是用fp16代替fp32來做train和inference。

其實(shí),使用fp16去訓(xùn)練,有時(shí)候還能得到比fp32更好的精度。從ML的角度來看,量化網(wǎng)絡(luò)本身就是對數(shù)據(jù)集正則化的一種方式,可以增強(qiáng)模型的泛化能力,從而提高精度。

其實(shí)還可以進(jìn)一步的用int8來取代fp16,這樣操作后,帶寬只有fp32的四分之一。

當(dāng)然,如果你不擔(dān)心精度的損失,那么也可以使用4bit, 2bit, 1bit去代替int8。

神經(jīng)網(wǎng)絡(luò)的量化其實(shí)可以分為:網(wǎng)絡(luò)權(quán)重的量化和網(wǎng)絡(luò)特征的量化。

網(wǎng)絡(luò)權(quán)重的量化對于最終的結(jié)果輸出損失比較小,而特征量化對最終的結(jié)果輸出損失就比較大。大模型和小模型對量化的敏感程度也不一樣,一般小模型會更加敏感。

關(guān)于量化想更深入的了解可以看一下下面的這些講解:

深度學(xué)習(xí)量化技術(shù)科普

Pytorch實(shí)現(xiàn)卷積神經(jīng)網(wǎng)絡(luò)訓(xùn)練量化(QAT)

MXNet實(shí)現(xiàn)卷積神經(jīng)網(wǎng)絡(luò)訓(xùn)練量化

深入了解NNIE量化技術(shù)

ICCV2019 高通Data-Free Quantization論文解讀

EasyQuant 后量化算法論文解讀

3.2 模型剪枝和參數(shù)共享

可以參考下面的講解:

如何讓你的YOLOV3模型更小更快?

YOLOV3剪枝方法匯總

深度學(xué)習(xí)算法優(yōu)化系列八 | VGG,ResNet,DenseNe模型剪枝代碼實(shí)戰(zhàn)

3.3 知識蒸餾

蒸餾的思想非常簡單,其實(shí)就是用一個(gè)小模型來取代一個(gè)大模型,從而使得小模型能夠?qū)崿F(xiàn)大模型的效果。大模型在這里一般叫做Teacher Net, 小模型叫做Student Net。從小模型到大模型的學(xué)習(xí)目標(biāo),包括最終的輸出層,網(wǎng)絡(luò)中間的特征結(jié)果,以及網(wǎng)絡(luò)的連接方案。

其實(shí),知識蒸餾本質(zhì)是一種transfer learning,比直接用小數(shù)據(jù)從頭開始訓(xùn)練一個(gè)model要得到更好的效果。

3.4 低秩近似

可以參考:https://blog.csdn.net/kathrynlala/article/details/82943291

3.5 二值化/三值化網(wǎng)絡(luò)

可以參考下面的講解:

基于Pytorch構(gòu)建一個(gè)可訓(xùn)練的BNN

基于Pytorch構(gòu)建三值化網(wǎng)絡(luò)TWN

低比特量化之XNOR-Net

低比特量化之DoreFa-Net理論與實(shí)踐

3.6 Winograd 變化

可以參考下面的講解:

詳解Winograd變換矩陣生成原理

詳解卷積中的Winograd加速算法

3.7 模型結(jié)構(gòu)化

模型結(jié)構(gòu)化其實(shí)是對模型加速最有效的一種方式。

那么關(guān)于模型結(jié)構(gòu)優(yōu)化,又會涉及到很多的知識。

接下來,就要講講怎么去設(shè)計(jì)一個(gè)高效的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu),它需要遵循一些基本原則。

從最初的AlexNet到現(xiàn)在的MobileNetv2,網(wǎng)絡(luò)的參數(shù)從最初的240MB降低到了35MB,

準(zhǔn)確率從57%也提高了75%。那么,我們肯定是去設(shè)計(jì)小的模型結(jié)構(gòu)從而完成相對于大模型難以完成的任務(wù)。那么在這個(gè)設(shè)計(jì)的過程中,會涉及哪些基本原則呢?

關(guān)于這些,超哥也講的非常到位,我也總結(jié)下:

小模型其實(shí)并不一定比大模型運(yùn)行(inference)的快。

一個(gè)網(wǎng)絡(luò)計(jì)算量小,并不代表他就一定運(yùn)行的快,因?yàn)檫\(yùn)行速度還和帶寬有關(guān),計(jì)算量僅僅是其中的一個(gè)因素。

那么,結(jié)合上面兩點(diǎn),我們就能明白。一個(gè)好的,跑起來比較快的網(wǎng)絡(luò)結(jié)構(gòu)。必須要衡量計(jì)算量和帶寬的需求。

4. 總結(jié)

總結(jié)下,如果要設(shè)計(jì)高效的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)來部署到硬件平臺。那么我們應(yīng)該盡可能的讓網(wǎng)絡(luò)中的operator去做并行化計(jì)算,同時(shí)減少這些operator對于帶寬的需求。

審核編輯 黃昊宇

-

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4771瀏覽量

100714 -

人工智能

+關(guān)注

關(guān)注

1791文章

47183瀏覽量

238255 -

AI芯片

+關(guān)注

關(guān)注

17文章

1879瀏覽量

34991

發(fā)布評論請先 登錄

相關(guān)推薦

BP神經(jīng)網(wǎng)絡(luò)和人工神經(jīng)網(wǎng)絡(luò)的區(qū)別

rnn是遞歸神經(jīng)網(wǎng)絡(luò)還是循環(huán)神經(jīng)網(wǎng)絡(luò)

遞歸神經(jīng)網(wǎng)絡(luò)與循環(huán)神經(jīng)網(wǎng)絡(luò)一樣嗎

遞歸神經(jīng)網(wǎng)絡(luò)是循環(huán)神經(jīng)網(wǎng)絡(luò)嗎

循環(huán)神經(jīng)網(wǎng)絡(luò)和卷積神經(jīng)網(wǎng)絡(luò)的區(qū)別

深度神經(jīng)網(wǎng)絡(luò)與基本神經(jīng)網(wǎng)絡(luò)的區(qū)別

人工智能神經(jīng)網(wǎng)絡(luò)芯片的介紹

神經(jīng)網(wǎng)絡(luò)芯片與傳統(tǒng)芯片的區(qū)別和聯(lián)系

神經(jīng)網(wǎng)絡(luò)芯片和普通芯片區(qū)別

反向傳播神經(jīng)網(wǎng)絡(luò)和bp神經(jīng)網(wǎng)絡(luò)的區(qū)別

bp神經(jīng)網(wǎng)絡(luò)和卷積神經(jīng)網(wǎng)絡(luò)區(qū)別是什么

卷積神經(jīng)網(wǎng)絡(luò)的原理是什么

卷積神經(jīng)網(wǎng)絡(luò)和bp神經(jīng)網(wǎng)絡(luò)的區(qū)別

神經(jīng)網(wǎng)絡(luò)架構(gòu)有哪些

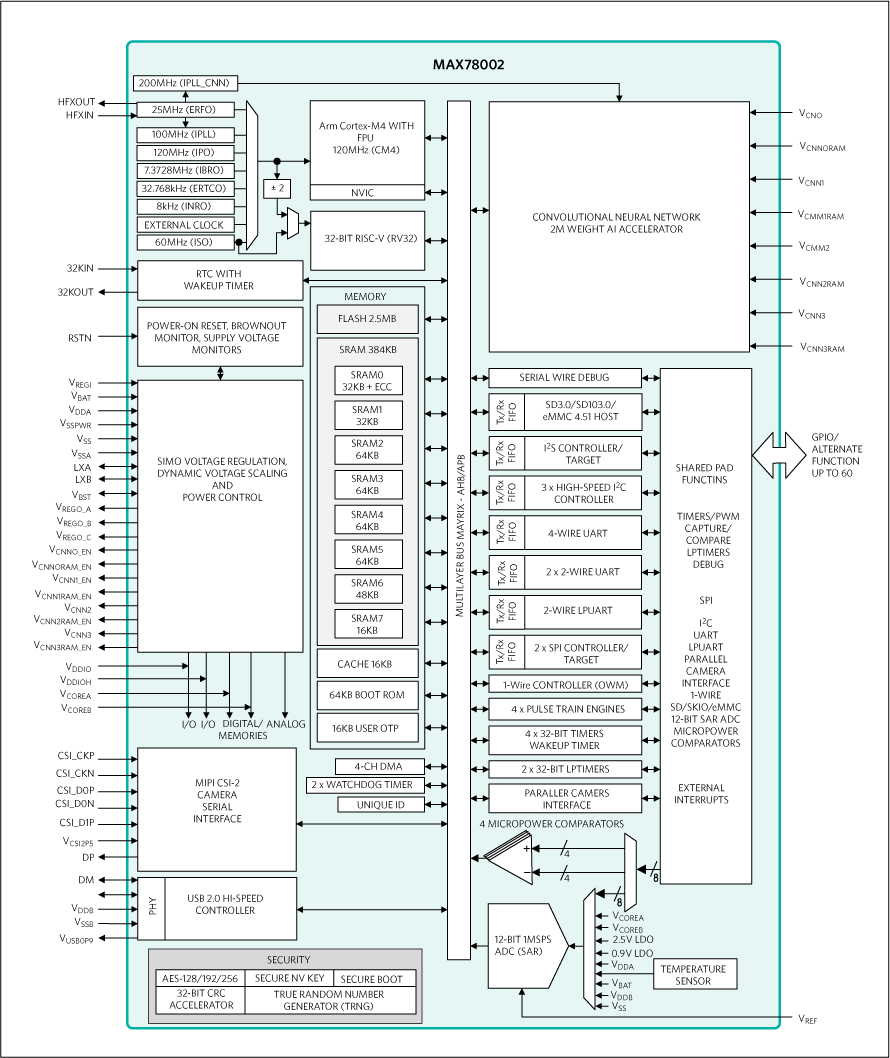

芯品#MAX78002 新型AI MCU,能夠使神經(jīng)網(wǎng)絡(luò)以超低功耗運(yùn)行

面向低功耗AI芯片上的神經(jīng)網(wǎng)絡(luò)設(shè)計(jì)介紹

面向低功耗AI芯片上的神經(jīng)網(wǎng)絡(luò)設(shè)計(jì)介紹

評論