我們生活在一個由模擬構成的世界中。不過,數字處理的出現,為我們體驗這個世界并與之互動帶來了全新的方式,包括衛星導航、自動駕駛汽車、增強現實,當然還有那永遠都離不了身的手機。

要想實時或者準實時地處理那么多信息,就必須要有強大的處理能力,這樣的處理能力顯然是受益于摩爾定律的。對于設計工程師而言,他們也可以從多種處理技術中來進行選擇,以便將最合適的技術運用到手邊的應用中。這些處理技術涵蓋了傳統處理器、圖形處理單元(GPU)和可編程邏輯(PL)。

在上述處理技術中,可編程邏輯恐怕是最鮮為人知的一種,人們也往往認為它是用起來最具挑戰性的處理技術之一。

No.1

可編程邏輯的優勢可編程邏輯能夠讓用戶在真正意義上并行實現其算法和應用,從而創造出更具有確定性、響應更加迅速的解決方案,因而適用于需要實時處理和響應的場景,例如視覺和信號處理以及雷達等。 傳統意義上,可編程邏輯器件可分為復雜可編程邏輯器件(CPLD)與現場可編程門陣列(FPGA)兩種類別, 其中CPLD基于“門海”(sea-of-gate)的方式提供由寄存器和邏輯函數構成的簡單器件結構。

至于FPGA,它提供的結構要比CPLD更加復雜,通常還會包含多種專用硬件元件,例如存儲塊、數字信號處理、時鐘管理、千兆串行收發器和IO塊。

No.2

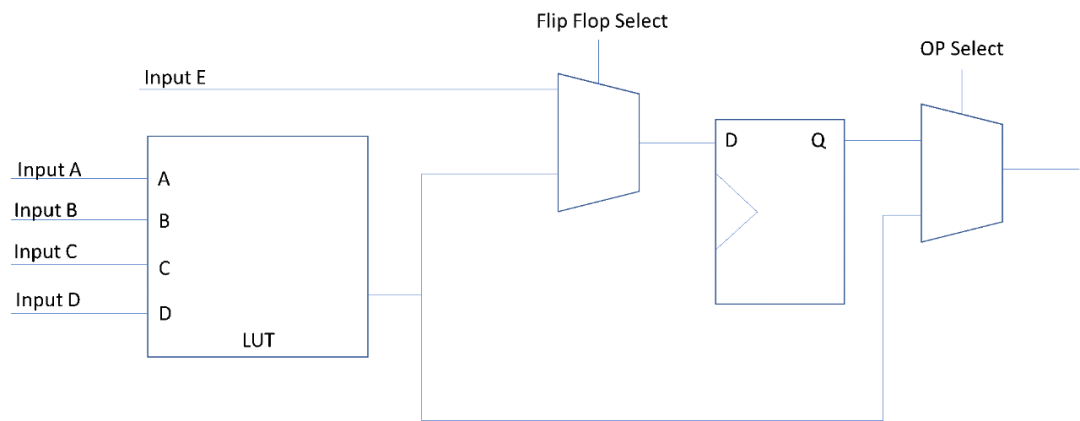

FPGA的構成要素FPGA的基本構成要素是查找表(LUT)、寄存器和靈活IO單元結構,其中LUT能夠實現邏輯方程式,而寄存器則為實現順序邏輯設計提供了必要的存儲元件。LUT和寄存器結合在一起,即可實現通常所說的“邏輯片”,其簡單示例如(圖1)所示。現代器件中的這些邏輯片包含諸多選項,以便實現組合邏輯電路或時序邏輯電路,這些選項包括本地分布式內存,以及可通過配置將LUT用作移位寄存器的功能。

圖1:簡單的LUT結構

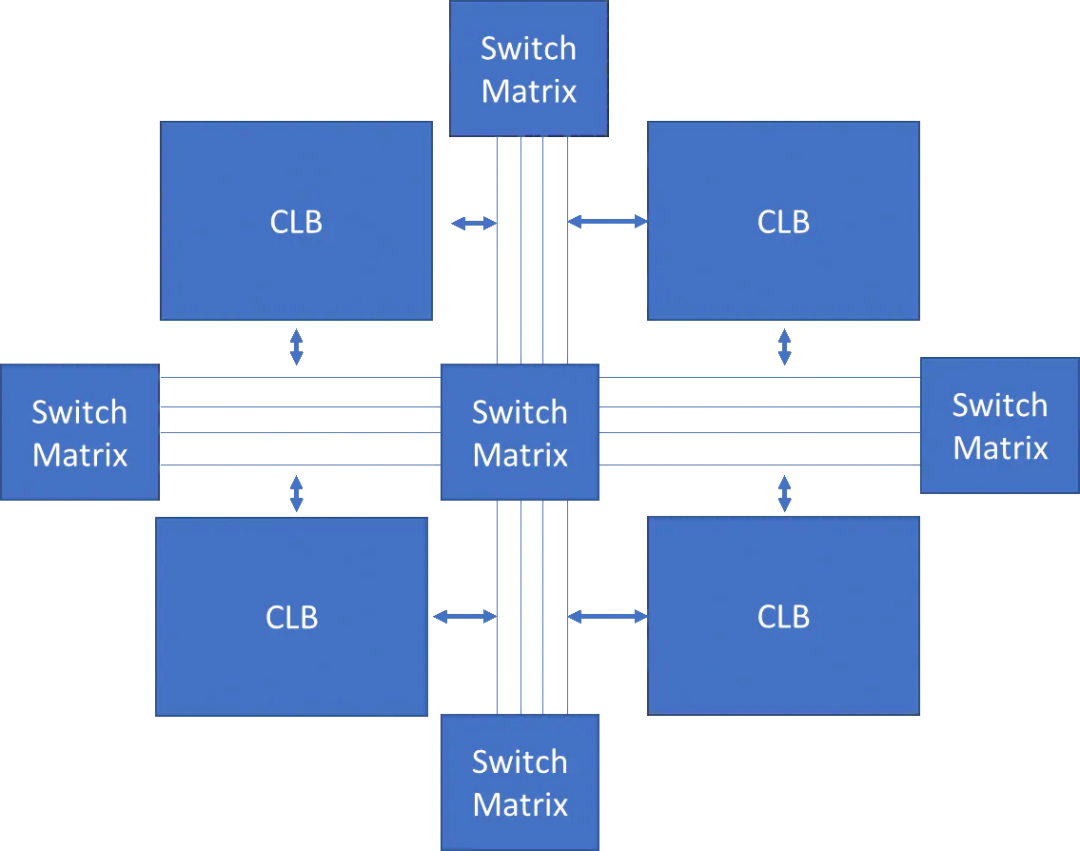

在FPGA器件中,通常將兩個邏輯片組合在一起,形成可配置邏輯塊(CLB)。這些CLB相互連接,以便通過路由和交換矩陣實現必要的功能,如圖2所示。

圖2:可通過交換矩陣配置路由塊和互連

No.3

FPGA設計FPGA通常使用硬件描述語言(HDL)設計,其中最常見的兩種是Verilog和VHDL。和傳統的軟件語言相比,這些語言需要在更加低級的層面上定義設計,它們具體描述的是寄存器級別上的傳輸,例如實現狀態機、計數器等。VHDL和Verilog都固有地支持并發的概念,這是對FPGA架構的并行架構進行建模所必需的。此外,通過高級綜合(HLS)使用C、C++或OpenCL等高級語言開發FPGA IP塊的做法也正變得越來越普遍。雖然這些語言并不支持并行,但工程師可以使用編譯器指令來指示并行結構,而使用更高級的語言有助于工程師更快地完成開發和驗證。 FPGA器件的IO結構可以直接對接各種IO標準,包括LVCMOS等單端標準以及LVDS、TMDS等差分標準。但這種IO結構的“技能”可遠不止于此——現代化的IO結構還可以實現片上端接、精細PS延遲,甚至SerDes結構。也就是說,FPGA有效地提供了各種對接接口,連接起了各種標準、定制或傳統接口。這種靈活性還使系統設計人員擺脫了引腳綁定的束縛,這與使用帶固定IO引腳分配的專用標準產品(ASSP)有著顯著區別。 因此,要設計出可編程邏輯設計解決方案,需要執行以下步驟:

合成 – 將HDL設計轉換為一系列邏輯方程,然后將其映射到目標FPGA中可用的資源上。

放置 – 把合成工具確定的邏輯資源放置到目標器件中的可用位置。

路由 – 使用路由和交換矩陣將設計中放置的邏輯資源互連,以實現最終應用。

位文件 – 生成目標FPGA的最終編程文件。

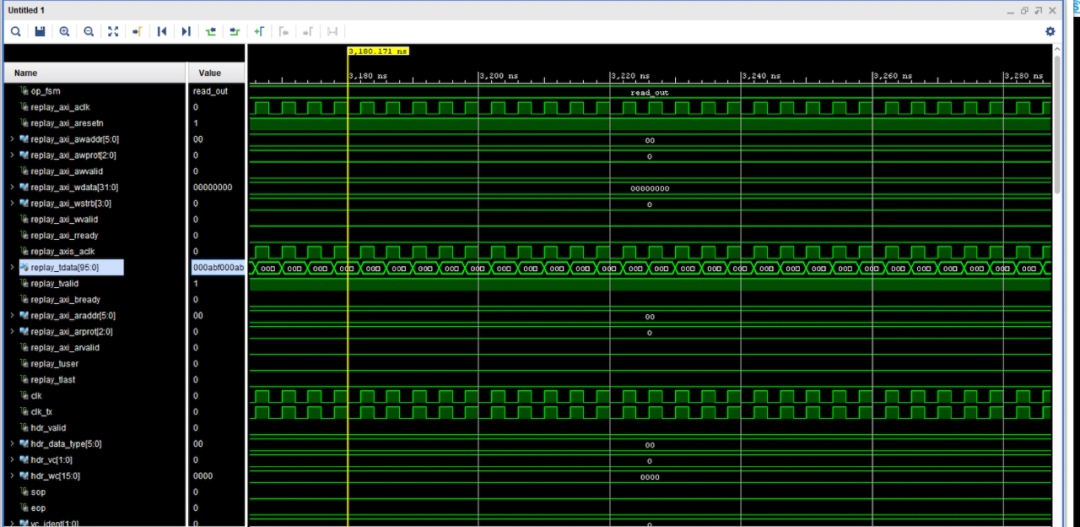

通過仿真,工程師可以確保他們實現的設計在功能上符合設計要求。他們可以創建激發RTL(寄存器傳輸級別)模塊的測試平臺,這些平臺可以提供輸入并監視結果輸出,然后通過查看仿真波形來驗證這些模塊的行為,如(圖3)所示。或者,他們也可以編寫更復雜的測試平臺,用來檢查和驗證輸出。

圖3:RTL仿真輸出

盡管FPGA在性能和接口上具有顯著優勢,但開發基于FPGA的解決方案可能會比開發傳統軟件更加復雜。不過,我們有現代化的設計工具,尤其是高級合成工具以及各種可以免費獲取的知識產權,并且現代化器件的功能也更加強大,這些都讓“FPGA更難開發”成為了歷史。

No.4

器件產品系列如果您還不熟悉FPGA的歷史,這里就先簡單地介紹一下。FPGA是Ross Freeman和Bernard Vonderschmitt于1985年隨著XC2064的發布而發明的,這款FPGA先驅產品具有64個可配置邏輯塊。今天,Xilinx的現代化器件可為用戶提供893.8萬個系統邏輯單元、3840個DSP元件、76Mb塊內存和90Mb的UltraRAM——這與最初的產品相比堪稱巨大飛躍。 當然,上面提到的器件是Xilinx現階段最大型的FPGA產品,對許多應用而言確實有點殺雞用牛刀了。為了幫助指導工程師選擇適合其應用的FPGA,Xilinx提供了一系列FPGA和片上系統器件,這些器件能夠支持多個不同系列的各種解決方案。 Xilinx圍繞28nm節點開發了一系列成本優化型產品,總共提供三個不同的器件系列,均針對不同的用戶需求進行了優化。

Spartan-7 FPGA:該系列是廣受歡迎的Spartan-6系列器件的后繼產品,可為開發人員提供比舊技術45nm節點更高的性能和更低的功耗。Spartan-7還經過了I/O優化,在成本優化的FPGA產品組合中是一個引腳數量非常高的系列。

Artix-7 FPGA:這是Xilinx 7產品線中的全新系列,針對收發器進行優化,具有6.6Gbps高速收發器。

Zynq-7000 SoC:該系列在初次亮相時頗具革新意義,它為業界帶來了將硬核Arm Cortex-A9處理器與FPGA架構相結合的新型器件。這種新型器件可以提供集成系統解決方案,并且具有功耗更低、解決方案整體體積更小、EMI顯著降低等優勢。

該產品組合中的器件可以支持從傳感器融合到精確控制、圖像處理和云計算等一系列應用。

No.5

高端解決方案對于超高性能和更專業的應用,Xilinx提供了28nm、20nm和16nm三個技術節點上的Kintex和Virtex系列。隨著UltraScale和UltraScale+系列器件的不斷發展,其性能和功能得到了顯著提高。 Kintex器件在三個技術節點上提供了不斷提升的性能、邏輯資源和收發器:從Kintex器件中的6.55萬個邏輯單元到Kintex UltraScale+器件中的11.43萬個邏輯單元。它們提供GTH和GTY千兆收發器,分別支持高達16.3Gbps和32.75Gbps的數據傳輸速率。

Virtex是Xilinx FPGA中性能最高的系列。這些器件不僅提供多達893.8萬個系統邏輯單元和58Gbps高速收發器,而且還支持高帶寬存儲器(HBM)。該系列產品具有4GB至16GB的片上DRAM和高達460Gbps的帶寬,其內存性能是DDR4 DIMM的約20倍。Virtex HBM器件適用于為網絡和存儲加速的應用。

No.6

工具鏈

Xilinx開發工具支持從最小的Spartan-7到最大的Virtex UltraScale+的所有器件,涵蓋了設計生命周期中的各個方面,從RTL捕獲直到仿真以及開發用于處理器核心的軟件。

Vivado設計套件:Vivado可以對設計、RTL仿真以及合成、放置、路由和生成位文件的實施過程進行捕獲。

Vivado HLS:高級合成工具,讓工程師能夠使用C或C++來開發IP。

Vitis一體化軟件平臺:Vitis支持嵌入式處理器的軟件開發,以及使用OpenCL進行加速。

PetaLinux工具:PetaLinux是用于嵌入式處理器的嵌入式Linux解決方案。

當然,您還可以選用其他各種商業和開源軟件工具,它們涵蓋了從合成到仿真的各個階段;此外,同時支持仿真和形式驗證的驗證工具正變得越來越多。

原文標題:何為FPGA?

文章出處:【微信公眾號:貿澤電子設計圈】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603795 -

寄存器

+關注

關注

31文章

5346瀏覽量

120485 -

RTL

+關注

關注

1文章

385瀏覽量

59827

原文標題:何為FPGA?

文章出處:【微信號:Mouser-Community,微信公眾號:貿澤電子設計圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

大多數FPGA的程序存儲器(FLASH)為什么都放在外面呢?FPGA的主要應用

什么是FPGA?

什么是FPGA?

評論