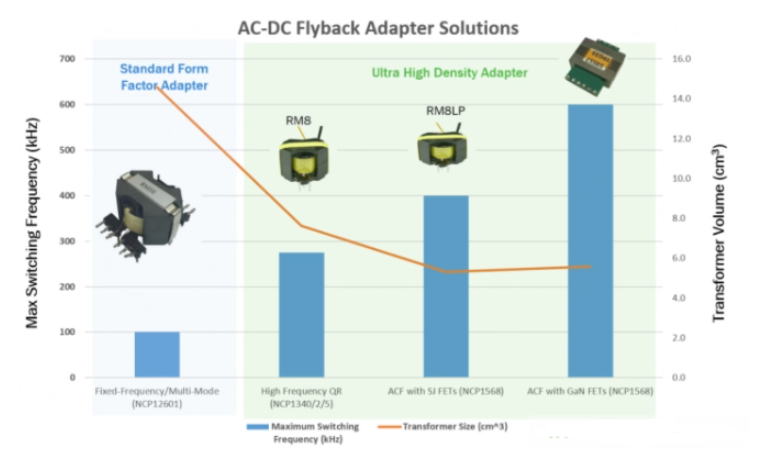

諸如USB-C PD 3.0 100 W可編程電源(PPS)等新興應(yīng)用推動(dòng)了對(duì)更小巧,更緊湊的開(kāi)關(guān)電源(SMPS)外形尺寸的需求。如圖1所示,提高開(kāi)關(guān)頻率可以減小變壓器體積,但是更高的開(kāi)關(guān)頻率則會(huì)增加功耗,從而需要不斷發(fā)展的反激式架構(gòu)。

?100 kHz的固定頻率/多模式反激式開(kāi)關(guān)驅(qū)動(dòng)標(biāo)準(zhǔn)SMPS適配器較大變壓器。移植到準(zhǔn)諧振(QR)反激會(huì)使開(kāi)關(guān)頻率增加到?280 kHz,從而將變壓器減小到較小的RM8尺寸。采用有源鉗位反激式(ACF)可使達(dá)到?450 kHz,從而實(shí)現(xiàn)外形較小的RM8LP變壓器。最后,用氮化鎵(GaN)代替硅結(jié)(SJ)FET可實(shí)現(xiàn)> 600 kHz的開(kāi)關(guān),實(shí)現(xiàn)更小的變壓器體積。

圖1增加開(kāi)關(guān)頻率可以減小變壓器的體積,但是更高的開(kāi)關(guān)頻率會(huì)增加功耗。資料來(lái)源:安森美半導(dǎo)體

反激式電源

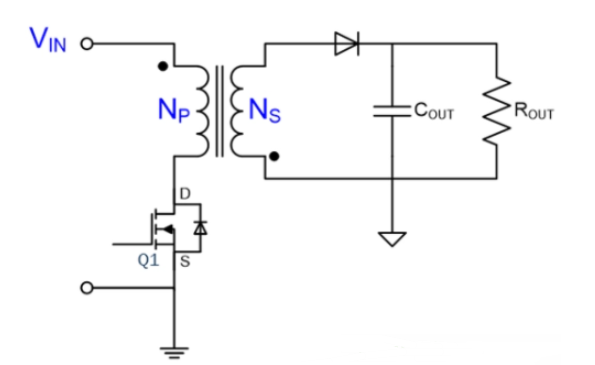

反激是中低功率AC-DC轉(zhuǎn)換器的一種流行拓?fù)洌饕且驗(yàn)樗牡统杀竞鸵子眯浴7醇な郊俣镈C輸入,并在次級(jí)側(cè)包含一個(gè)變壓器,一個(gè)電源開(kāi)關(guān)(Q1)和一個(gè)二極管(圖2)。變壓器(其中的點(diǎn)表示初級(jí)側(cè)與次級(jí)側(cè)異相180°)是一個(gè)耦合電感器,只有在關(guān)閉電源開(kāi)關(guān)時(shí),能量才從初級(jí)傳遞到次級(jí)。

圖2反激式拓?fù)湓诖渭?jí)側(cè)包括一個(gè)變壓器,一個(gè)電源開(kāi)關(guān)和一個(gè)二極管。資料來(lái)源:安森美半導(dǎo)體

反激工作方式

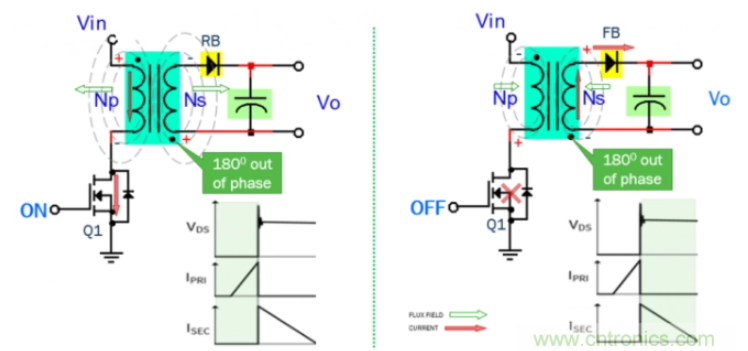

當(dāng)電源開(kāi)關(guān)(Q1)接通(圖3,左)時(shí),電流從Vin流出,能量存儲(chǔ)在初級(jí)側(cè)和次級(jí)側(cè)(磁通場(chǎng)擴(kuò)展)電感器中。電流不會(huì)在次級(jí)側(cè)線圈中流動(dòng),因?yàn)槎O管會(huì)由于180o的反相而反向偏置。

當(dāng)電源開(kāi)關(guān)關(guān)閉時(shí)(圖3,右),初級(jí)和次級(jí)磁通場(chǎng)都開(kāi)始消除,初級(jí)側(cè)的極性發(fā)生變化(反激作用),二極管正向偏置,電流在次級(jí)側(cè)流動(dòng),。

圖3該圖顯示了電源開(kāi)關(guān)處于打開(kāi)狀態(tài)(左)和關(guān)閉(右)時(shí)的反激式操作。資料來(lái)源:安森美半導(dǎo)體

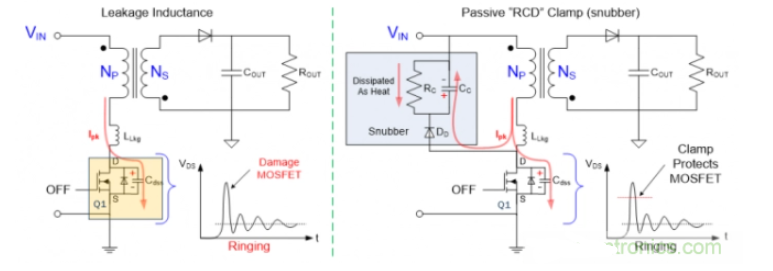

反激式漏電感

不幸的是,當(dāng)電源開(kāi)關(guān)(Q1)斷開(kāi)時(shí),初級(jí)側(cè)漏電感(LLkg)與電源開(kāi)關(guān)的漏源電容Cdss相互作用,導(dǎo)致VDS上出現(xiàn)過(guò)多振鈴,這會(huì)損壞MOSFET(左圖4)。可以添加一個(gè)稱(chēng)為緩沖器的無(wú)源電阻電容二極管RCD鉗位來(lái)保護(hù)MOSFET(圖4,右)。緩沖器將LLkg能量從MOSFET漏極移動(dòng)到緩沖器電容器(CC),并通過(guò)RC散發(fā)熱量。緩沖器不能提高整體反激效率。

圖4添加RCD緩沖器可以保護(hù)MOSFET 資料來(lái)源:安森美半導(dǎo)體

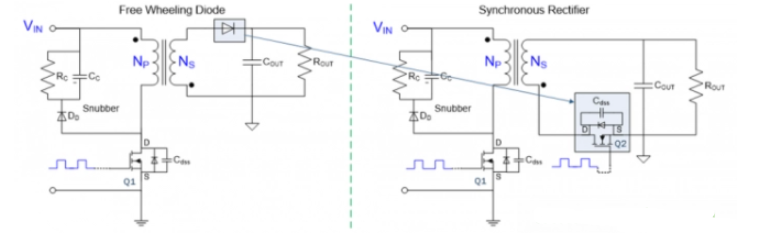

次級(jí)側(cè)的同步整流器

用MOSFET(圖5中的Q2,右)替換“續(xù)流”二極管(圖5,左)可提高次級(jí)側(cè)效率。 MOSFET的RDSON耗散的功率比硅二極管(0.6V正向偏置)甚至肖特基(0.3V)二極管要少得多。

圖5在次級(jí)側(cè)添加SR MOSFET可以提高效率。資料來(lái)源:安森美半導(dǎo)體

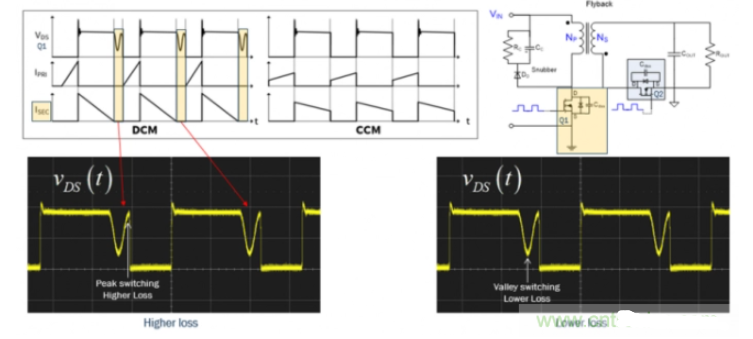

波谷切換和準(zhǔn)諧振反激

在次級(jí)側(cè)電流(ISEC)達(dá)到零或不連續(xù)模式(DCM)之后,由于勵(lì)磁電感和開(kāi)關(guān)節(jié)點(diǎn)電容之間的諧振,Q1電源開(kāi)關(guān)VDS可能會(huì)出現(xiàn)振蕩(圖6)。這些振蕩形成波谷。QR開(kāi)關(guān)將尋找下一個(gè)波谷,以便下次打開(kāi)電源開(kāi)關(guān)。簡(jiǎn)而言之,在峰值期間打開(kāi)Q1會(huì)增加功耗,而在波谷值期間打開(kāi)Q1則會(huì)降低功耗。

圖6電源開(kāi)關(guān)可能表現(xiàn)出谷底開(kāi)關(guān)振蕩。資料來(lái)源:安森美半導(dǎo)體

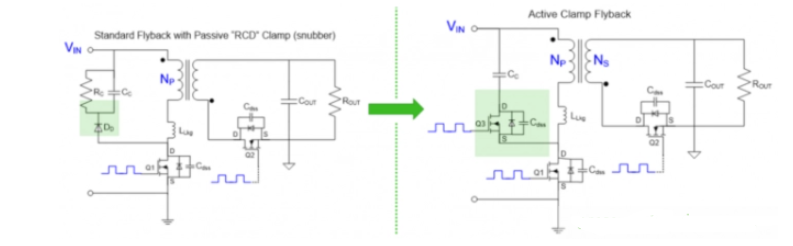

有源鉗位反激(ACF)

用MOSFET(Q3)替換鉗位二極管(圖7,左)可以提高效率(圖7,右),并保護(hù)電源開(kāi)關(guān)(Q1)。

圖7 ACF架構(gòu)提高了電源效率。資料來(lái)源:安森美半導(dǎo)體

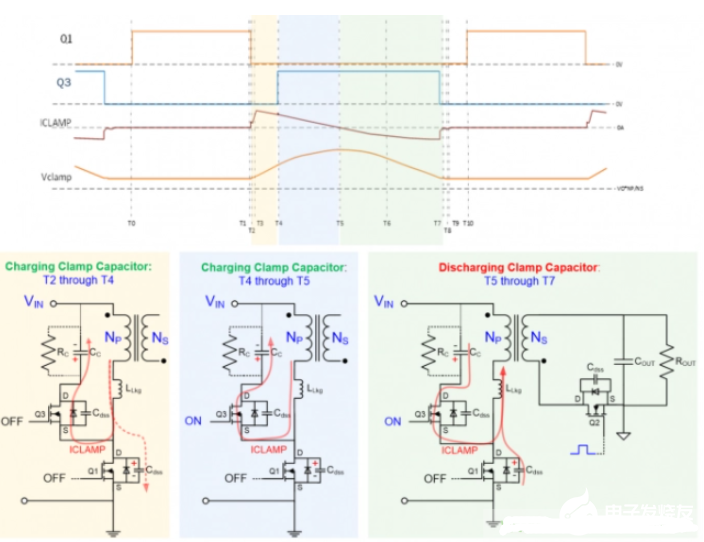

ACF體系結(jié)構(gòu)可以將泄漏電感循環(huán)回負(fù)載。參考圖8的相對(duì)時(shí)序圖,電源開(kāi)關(guān)(Q1)在T0接通,在T2斷開(kāi)。在T2處,漏感(ICLAMP)開(kāi)始流過(guò)有源鉗位(Q3)體二極管,為鉗位電容器(VCLAMP)充電。在T4,Q3打開(kāi),繼續(xù)VCLAMP充電。在T5處,ICLAMP變?yōu)樨?fù)值,現(xiàn)在VCLAMP通過(guò)Q3將漏電感放電回到負(fù)載,直到T7。

圖8該相對(duì)時(shí)序圖中顯示了ACF泄漏電感的再循環(huán)。資料來(lái)源:安森美半導(dǎo)體

從T9到T10,有源鉗位(Q3)在下一個(gè)Q1導(dǎo)通時(shí)間將VDS穩(wěn)定在0V,這稱(chēng)為零電壓開(kāi)關(guān)(ZVS)。如果在ZVS,則FET電容為零。因此,導(dǎo)通開(kāi)關(guān)損耗為零,效率更高。這是一種軟開(kāi)關(guān)形式,也有利于EMI。

ACF的缺點(diǎn)

ACF有兩個(gè)缺點(diǎn)。再參考圖8,從T5到T7的相對(duì)時(shí)序,當(dāng)ICLAMP變?yōu)樨?fù)值時(shí),磁通密度增加,從而導(dǎo)致有源鉗位鐵芯損耗與之相比略高。圖4的RCD緩沖器。另一個(gè)缺點(diǎn)是ICLAMP在Q1關(guān)斷時(shí)間內(nèi)流入變壓器的初級(jí)繞組。這增加了初級(jí)繞組損耗。

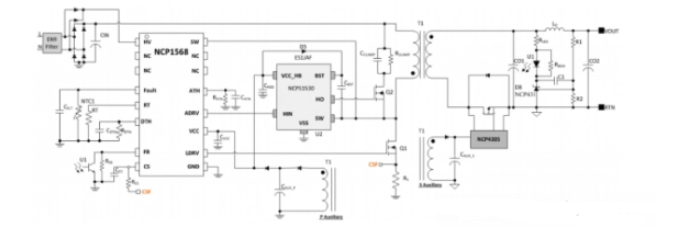

安森美半導(dǎo)體的NCP1568是一款高度集成的AC-DC脈寬調(diào)制(PWM)控制器,旨在實(shí)現(xiàn)ACF拓?fù)洌▓D9),從而使ZVS能夠用于高效,高頻和高功率密度應(yīng)用。不連續(xù)傳導(dǎo)模式(DCM)操作可在待機(jī)功率<30 mW的輕負(fù)載條件下實(shí)現(xiàn)高效率。

NCP1568 LDRV輸出能夠直接驅(qū)動(dòng)市場(chǎng)上大多數(shù)超結(jié)(SJ)MOSFET,而無(wú)需外部組件。 ADRV驅(qū)動(dòng)器是5V邏輯電平驅(qū)動(dòng)器,用于將驅(qū)動(dòng)信號(hào)發(fā)送到NCP51530等高壓驅(qū)動(dòng)器。高壓驅(qū)動(dòng)器應(yīng)具有較小的延遲,并適合高達(dá)400 kHz的工作頻率。

圖9 NCP1568 ACF驅(qū)動(dòng)超結(jié)MOSFET Q1。資料來(lái)源:安森美半導(dǎo)體

ACF驅(qū)動(dòng)GaN

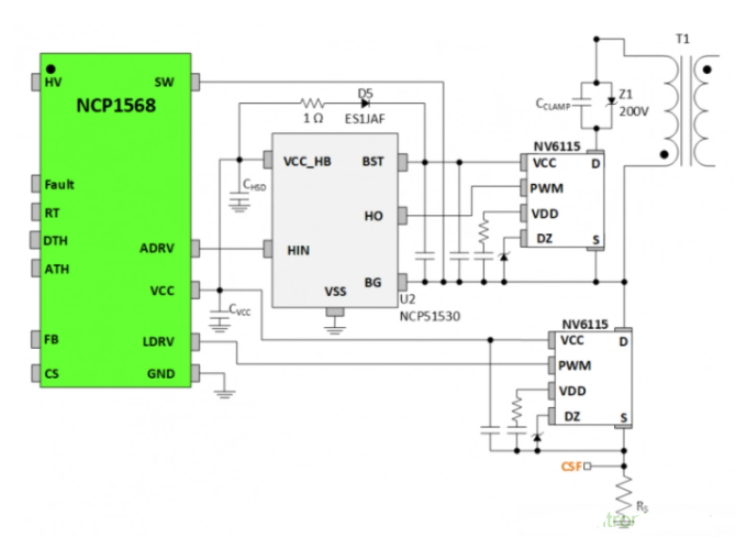

用于GaN晶體管的SJ MOSFET可以實(shí)現(xiàn)更快的開(kāi)關(guān)頻率,這主要是由于GaN的寄生電容較低。當(dāng)然,GaN的成本要高于SJ FET。Navitas Semiconductor的NV6115驅(qū)動(dòng)器接受來(lái)自12V或5V驅(qū)動(dòng)器的輸入信號(hào)。驅(qū)動(dòng)器調(diào)節(jié)已在GaN內(nèi)部完成。圖10的配置顯示了來(lái)自NCP1568和NCP51530的驅(qū)動(dòng)信號(hào)以滿(mǎn)足系統(tǒng)需求。

圖10 NCP1568 ACF驅(qū)動(dòng)NV6115 GaN功率晶體管。資料來(lái)源:安森美半導(dǎo)體

USB-C供電2.0與3.0 PPS

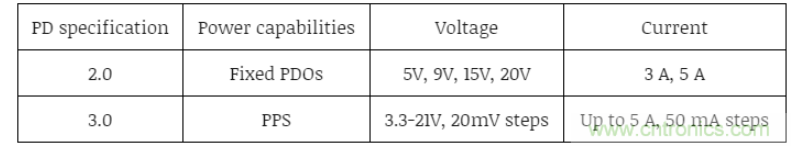

USB-C PD源最多可以播報(bào)七個(gè)電源數(shù)據(jù)對(duì)象(PDO),用于將源端口的電源功能公開(kāi)給支持PD的接收器。PD 2.0 PDO是固定的,而PD 3.0 PDO是從3.3V到21V的可編程電壓(20mV步進(jìn))設(shè)置,以及高達(dá)50A的可編程電流(以50mA步進(jìn))(表1)。PPS的優(yōu)勢(shì)在于該源可提供更精細(xì)的電壓/電流粒度,從而提高USB-C源與散熱之間的效率。

表1 USB-C PD 2.0與3.0 PPS

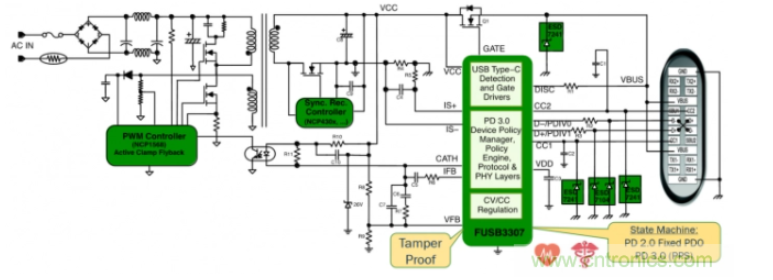

FUSB3307是完全自主的PD 3.0 v1.2和C型v1.3、100 W、源控制器,能夠提供3.3-21V(20mV步進(jìn))和高達(dá)5A(50mA步進(jìn))的VBUS,最高可提供七個(gè)固定和PPS PDO。FUSB3307是不帶MCU的低成本硬件狀態(tài)機(jī)解決方案。無(wú)需開(kāi)發(fā)固件,可以加快產(chǎn)品上市時(shí)間,并提供防篡改的全功能解決方案。

FUSB3307控制通過(guò)光耦合器的CATH引腳電流,向初級(jí)側(cè)控制器提供反饋以調(diào)節(jié)VBUS電壓。

圖11 FUSB3307 PD 3.0 PPS控制器是防篡改的全功能解決方案。資料來(lái)源:安森美半導(dǎo)體

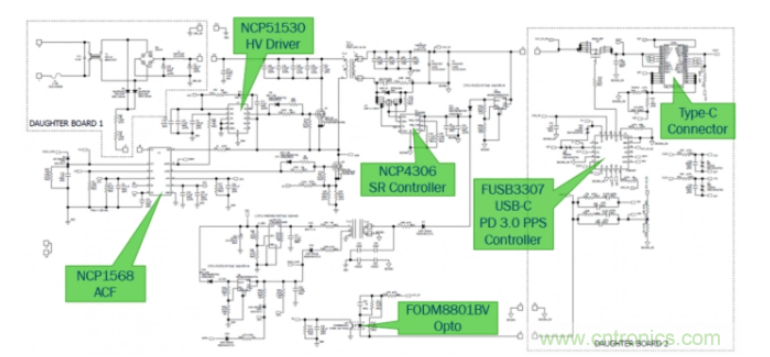

圖12說(shuō)明了安森美半導(dǎo)體采用USB-C PD 3.0和PPS的29 W / in3、60 W ACF參考設(shè)計(jì)。 NCP1568 ACF(U2)通過(guò)NCP51530(U7)3.5 A,700V半橋驅(qū)動(dòng)器控制SJ電源開(kāi)關(guān)(Q1)和SJ有源鉗位(Q2)。NCP4306(U5),7A(漏極),2A(源極)柵極驅(qū)動(dòng)器用于同步整流器控制。FUSB3307(子板2的U1)是基于狀態(tài)機(jī)的USB-C PD 3.0端口控制器,可通過(guò)FODM8801BV(U8)光耦合器控制NCP1568 FB輸入及其CATH輸出來(lái)調(diào)節(jié)VBUS(5-20V)。

圖12這種60 W USB-C PD 3.0 PPS參考設(shè)計(jì)包含NCP1568 ACF,NCP51530驅(qū)動(dòng)器,NCP4306控制器,F(xiàn)USB3307控制器和FODM8801BV光耦合器。資料來(lái)源:安森美半導(dǎo)體

圖13的4點(diǎn)平均效率圖的每個(gè)數(shù)據(jù)點(diǎn)都捕獲了以下四個(gè)額定功率輸出的平均效率。使用超結(jié)MOSFET達(dá)到25%,50%,75%和100%,開(kāi)關(guān)頻率高達(dá)450kHz。可以看到,從5V輸出到20V輸出4點(diǎn)平均的NCP1568 115 Vac(藍(lán)線)和230 Vac(綠線)遠(yuǎn)高于DoE要求的VI級(jí)最低限制(紅線) 。

圖13該4點(diǎn)平均效率圖顯示NCP1568超過(guò)了DoE Level VI的最低限制。資料來(lái)源:安森美半導(dǎo)體

許多應(yīng)用都對(duì)UHD電源提出了很高的要求,包括100 W USB-C PD 3.0 PPS。ACF是在成本和性能之間實(shí)現(xiàn)最佳平衡的首選架構(gòu)。這是因?yàn)樵诓辉黾覩aN成本的情況下,可以獲得29 W / in3的功率密度,最高可達(dá)92%的4點(diǎn)效率。而且,如果應(yīng)用允許更高的成本和更高的效率,那么ACF也可以驅(qū)動(dòng)GaN,以實(shí)現(xiàn)更高的效率和更高的功率密度。

(來(lái)源:安森美,作者:鮑勃·卡德(Bob Card),安森美北美高級(jí)解決方案部門(mén)(ASG)的市場(chǎng)經(jīng)理)

編輯:hfy

-

變壓器

+關(guān)注

關(guān)注

159文章

7462瀏覽量

135134 -

開(kāi)關(guān)電源

+關(guān)注

關(guān)注

6459文章

8328瀏覽量

481751 -

適配器

+關(guān)注

關(guān)注

8文章

1951瀏覽量

67997 -

可編程電源

+關(guān)注

關(guān)注

3文章

82瀏覽量

24207 -

耦合電感器

+關(guān)注

關(guān)注

0文章

13瀏覽量

5463

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用LMG3622EVM-082 65W USB-C PD高密度準(zhǔn)諧振反激式轉(zhuǎn)換器

使用UCC28782EVM-030 65W USB-C PD高密度有源鉗位反激式轉(zhuǎn)換器

使用LMG3624EVM-081 65W USB-C PD高密度準(zhǔn)諧振反激式轉(zhuǎn)換器

使用LMG3626EVM-074 USB-C PD高密度準(zhǔn)諧振反激式轉(zhuǎn)換器

什么是反激式開(kāi)關(guān)電源,與正激式有什么區(qū)別

使用有源鉗位反激式控制器(UCC28780)增大功率密度

反激式開(kāi)關(guān)電源反饋回路分析

ZVS 反激式轉(zhuǎn)換器芯片組,適用于先進(jìn)USB-C PD適配器和充電器

140 W超高功率密度USB-C EPR適配器,采用ZVS反激式轉(zhuǎn)換器和PFC +混合反激式控制器

PMP40974.1-使用有源鉗位反激式控制器的高功率密度65W USB Type-C? 充電器 PCB layout 設(shè)計(jì)

PMP21639.1-采用 GaN 的 65W USB Type-C? 高密度有源鉗位反激式 PCB layout 設(shè)計(jì)

基于USB-C PD 3.0有源鉗位反激的開(kāi)關(guān)電源方案

基于USB-C PD 3.0有源鉗位反激的開(kāi)關(guān)電源方案

評(píng)論