ADC,也即數模轉換轉換器。對于ADC,小編在往期文章中有所介紹,如管道ADC的優缺點、流水線ADC結構分析等。為增進大家對ADC的認識,本文將對ADC外圍電路設計方法予以介紹。如果你對ADC,抑或是對本文即將闡述的內容具有興趣,不妨繼續往下閱讀哦。

在使用ADC芯片時,由于ADC的型號多樣化,其性能各有局限性,所以為了使ADC能夠適應現場需要以及滿足后繼電路的要求,必需對ADC的外圍電路進行設計。ADC外圍電路的設計通常包括模擬電路、數字電路和電源電路的設計。

一、模擬電路設計

1.1 前置放大器電路的設計

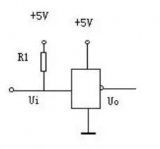

市場上除了少數的ADC本身帶有放大電路外,多數ADC都不具備此結構,而一般模/數轉換系統的模擬輸入信號是比較小的,因此通常需要使用模擬放大器,來提升輸入電壓。模擬放大器一般選用集成運算放大器、儀表放大器或隔離放大器等。使用模擬放大器時要著重考慮放大器的帶寬和精度,當選擇運算放大器時,其帶寬和精度都應當優于所選擇的ADC。

模擬放大器不僅能放大模擬輸入信號,而且還具有阻抗變化的作用。對于輸入電阻比較小的ADC,而信號源的內阻又比較大時,需要選用高輸入阻抗、低輸出阻抗的放大器,有時也可以加接電壓跟隨器,以提高輸入阻抗,從而達到匹配的目的。

1.2 采樣保持電路的設計

采樣保持電路可以使ADC轉換器在轉換期間保持電壓不變,因此對于沒有采樣保持電路的ADC,必需在模擬輸入之前加接采樣保持電路。在選用采樣保持器時,要注重捕獲時間和頂級率的選擇,因為它們直接關系到模/數轉換系統的整體性能。捕獲時間實質就是采樣保持器的采樣階段所需的時間,它要與ADC的轉換時間合理配合,過大則影響ADC的轉換速率,過小則容易產生功能混亂或數據丟失等現象。

在ADC進行轉換的過程中,采樣保持電路進入保持階段。通常采樣保持電路是靠電容來進行電壓保持的,由于電容和采樣開關中漏電流以及保持電路中偏置電流的影響,使保持的模擬電壓隨時間的延續而有所下降(或上升),其下降的速率就是采樣保持電路的頂級率。頂級率過大就會影響轉換精度。頂級率和捕獲時間不但與采樣保持電路有關,而且還與外接的保持電容有關,增大電容時,可以減小頂級率,但捕獲時間將增大,因此需要全面考慮。對于模擬輸入電壓變化緩慢的系統,可以不使用采樣保持電路,一般模擬輸入電壓變化不超過1/2LSB時,就可不用。

1.3 多路開關的設計

多路開關也是ADC的主要外圍設備之一。設計時需要注意以下問題:實際中,部分ADC的輸入電阻較小,而模擬多路開關并不是理想開關,其導通電阻較大,因此ADC與模擬多路開關之間的阻抗并不匹配,這將影響整個系統的運行精度,因此不容忽視,這時可在多路開關與ADC之間加接高輸入阻抗的電壓跟隨器;此外模擬多路開關存在漏電流,而且各路開關是并聯的,當開關的路數較多時,漏電流就不能忽視,這時可采用分級模擬開關來解決這個問題;在多通道的數據采集系統中,當通道切換時,模擬電壓將產生階躍變化,這時應等階躍變化穩定后,再讓采樣保持電路進入采樣階段;具有分級流水結構的ADC和∑-△型的ADC,其輸出的數據是滯后的,因此需要全面考慮轉換器外圍電路所需的穩定時間以及ADC對多路開關的階躍變化所需的響應時間等。

二、數字外圍電路的設計

ADC的輸出是數字電路,它與后繼電路相連接所需要的數據線可以分為并行接口和串行接口兩種型式。

2.1 并行接口電路的設計

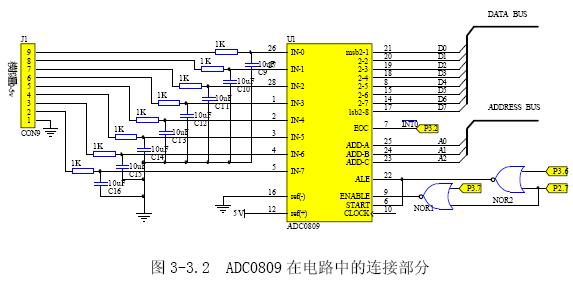

絕大多數ADC的數據輸出都具備并行接口,可以很方便地與下級電路(微處理器等)的數據總線相連接,數據傳送速度快。ADC的數據總線常用的有8位和16位,但一般10~16位的ADC既能與16位的接口方式與16位的微控制器直接相連,又能以8位接口方式與8位微控制器相連。并行接口除了并行的數據線外,還需要許多控制信號線和狀態信號線,如啟動轉換信號線、讀/寫信號線、片選信號線等。由于各種ADC的芯片各不相同,所以在設計時,必須弄清具體型號的各信號定義、時序以及使用微控制器的總線時序,從而才能設計出滿足時序要求的接口電路。

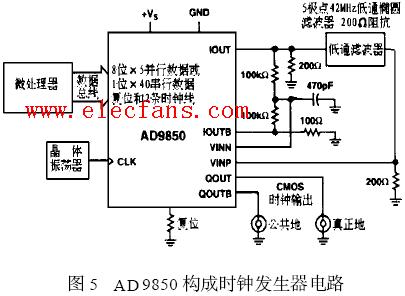

2.2 串行接口電路的設計

串行接口只需要1根雙向數據線、或者2條傳輸方向相反的數據線和少量的控制線。這樣能大大地減少芯片的引腳數目,進而簡化了整機的布線。實際中多數微型控制器都有串行接口,這樣給串行數據輸出的ADC使用提供了便利的條件,不過這種傳輸方式速度慢、效率低,但隨著芯片工作頻率的提高,串行傳輸速率也得到了改善。常見的串行接口有通用異步接收/發送器、串行外圍接口和I2C總線等,設計時應根據具體情況采取相應的方式。

-

放大器

+關注

關注

143文章

13583瀏覽量

213367 -

接口電路

+關注

關注

8文章

464瀏覽量

57076 -

adc

+關注

關注

98文章

6495瀏覽量

544461

發布評論請先 登錄

相關推薦

ADC外圍電路的設計

ADC外圍電路設計方法

電源外圍保外圍應用電路

用32的ADC對電腦輸出音頻采樣,外圍電路怎么搭?

ADC的外圍電路供電是從電源的VCC取電好還是從VDDA取電較好?

一文教你如何進行ADC的外圍電路設計!

STM32 ADC緩沖運放外圍電路的設計要求有哪些

adc0809外圍電路

單片機外圍電路應該如何設計詳細的設計攻略分享給你

ADC外圍電路應該如何設計

ADC外圍電路應該如何設計

評論