2020年12月,由日本工業技術研究院(AIST)和中國臺灣半導體研究中心(TSRI)代表的聯合研究小組宣布了用于2nm世代的Si(硅)/ Ge(硅)/ Ge層壓材料。他們同時宣布,已開發出一種異質互補場效應晶體管(hCFET)。

由于微加工技術的進步,電場效應晶體管(FET)已實現了高性能和低功耗。

在22nm世代中,它推進到被稱為“ FinFET”的三維柵極結構的FET。此外,GAA(全方位門)結構已作為替代版本出現。

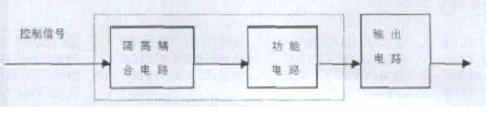

除此之外,還有一種稱為CFET結構的技術,該結構是將n型FET和p型FET彼此堆疊的結構。其面積可以大大減小,速度可以提高。

FET結構路線圖資料來源:AISTAIST

一直在研究和開發混合了硅n型FET和鍺p型FET的CMOS技術。另一方面,TSRI一直致力于開發精細工藝技術,以在2nm世代之后實現3D溝道。因此,兩家公司于2018年啟動了一項國際聯合研究項目,以利用各自的優勢。

該項目旨在開發可堆疊Si和Ge層的Si / Ge異質溝道集成平臺,并且是一種低溫異質材料鍵合技術(LT-HBT ),可在200°C或更低的溫度下堆疊高質量的Si和Ge層。開發了低溫異質層粘接技術。由于所有的層壓和刻蝕工藝都可以在低溫下進行,因此其特點是對Si層和Ge層的破壞極小,可以實現高質量的Si / Ge異質溝道集成平臺。

該產品制造過程如下。首先,準備在主晶片上外延生長Ge的“主晶圓”和“供體晶圓”。SiO2絕緣膜沉積在主硅片的每一個上以活化表面。然后,將其直接在200°C下粘合。然后,順序地去除施主硅片的Si襯底,BOX絕緣膜和Si層。最后,使用東北大學開發的中性束刻蝕(NBE)將Ge均勻薄化。

結果,實現了Si / Ge異質溝道層疊結構。這項技術可以大大簡化hCFET的制造過程,也可以用于其他多層結構。

使用低溫異種材料鍵合技術的Si / Ge異質通道層壓工藝過程來源:AIST

該研究小組使用已開發的Si / Ge異質溝道堆疊平臺創建了hCFET。形成具有相同溝道圖案的Si和Ge層,并且去除Si層和Ge層之間的絕緣層以形成納米片狀的層疊溝道結構。從SEM俯瞰圖,可以確認Ge和Si通道是暴露的。

在該結構上沉積高k柵絕緣膜(Al2 O3)和金屬柵(TiN)以覆蓋整個溝道,并且上下放置GAA結構“ 硅n型FET”和“ p型FET”。已經實現了堆疊的hCFET。從TEM截面圖,發現上部的Ge層和下部的Si層以具有約50nm的溝道寬度的納米片的形式層疊。這些結構也可以通過TEM EDX分析來確認。

此外,我們成功地通過單個柵極同時操作了這些“ n型FET”和“ p型FET”。事實證明,通過LT-HBT堆疊不同的通道作為2nm世代晶體管技術極為有效。

這項研究的結果是日本小組(AIST和東北大學),由高級CMOS技術研究小組的研究員Chang Wen Hsin,AIST的器件技術研究部門以及TSRI的Lee Yao-Jen Research代表。它是由研究員組成的中國臺灣團隊(交通大學,成功大學,南方國際大學,臺灣大學,國立中山大學,愛子大學,工業技術學院,臺灣日立高科技)的國際合作研究小組

。國際合作研究小組,連同急于向包括海外的私人公司建立一個高精度的異構渠道集成平臺,有望進行為期三年的技術轉讓。

責任編輯:PSY

-

半導體

+關注

關注

334文章

27442瀏覽量

219451 -

晶體管

+關注

關注

77文章

9701瀏覽量

138373 -

低功耗

+關注

關注

10文章

2407瀏覽量

103761 -

高性能

+關注

關注

0文章

157瀏覽量

20411 -

2nm

+關注

關注

1文章

206瀏覽量

4524

發布評論請先 登錄

相關推薦

結型場效應晶體管和N溝道場效應晶體管有什么區別

結型場效應晶體管的工作原理和特性

如何選擇場效應晶體管

什么是結型場效應晶體管

場效應晶體管和雙極性晶體管有什么區別

場效應晶體管利用什么原理控制

LF444-DIE 4路低功耗結型場效應晶體管(JFET)輸入運算放大器數據表

一種集成低功耗pH傳感器的離子敏感場效應晶體管(ISFET)

場效應晶體管怎么代替繼電器 晶體管輸出和繼電器輸出的區別

2nm異質互補場效應晶體管(hCFET)已開發,實現高性能和低功耗

2nm異質互補場效應晶體管(hCFET)已開發,實現高性能和低功耗

評論