作者:黃剛

眾所周知,原理圖是整個設計流程的前端,關系到后面的PCB設計、加工、焊接、整板功能的調試是否成功。如果原理圖出錯導致調試失敗的水平也分段位的話,大家說說看本文的這個案例的出錯水平屬于哪個段位呢?

這又是一個關于DDR系統的故事。高速先生這幾年深耕在DDR仿真設計這個領域中,基本上經過我們仿真設計的各種DDR系統都很少出現功能的問題了。但是與此同時,DDR設計的難度的確是逐年增加的,單通道容量越來越大,密度越來越高,層數越來越少,速率越來越高,因此高速先生能看到我們有些客戶們的DDR設計稍顯吃力,然后出現問題的幾率也慢慢增加。我們在最近的文章中也給大家分享了一些fail的例子,那么今天再給大家分享一個由于原理圖問題導致的fail案例哈。

這又是另外一個略帶點困意的午后,高速先生剛投入到下午的工作,突然就收到了一封醒神的郵件:

高速先生看到這封簡單而有力的郵件,的確shock到了我們,兩組基本一樣的設計居然一組能成功運行到額定的速率,另外一組居然連啟動都啟動不了!!!差別之大,可能是高速先生前所未見的。一般來說,同一個板的幾個DDR通道,最多會出現降頻能運行的差別,像這樣的差別真的只能用以下的詞語來形容了。

但是震驚歸震驚,分析還是要去分析的,PCB是我司進行設計和加工的,但是并沒有進行仿真,因此板子的設計到加工整個流程都并沒有經過高速先生的檢閱。因此高速先生看到板子的時候,基本上就和你們看到板子是同一個時候了。我們看看其中一路DDR的拓撲,發現還是一個比較有難度的設計,一個通道10個顆粒,1拖10的拓撲,采用正反貼的結構進行布局。

從布局到布線來看,我們設計工程師的水平還是可以信賴的,高速先生會經常在內部去一起討論DDR設計的細節方法,因此高速先生是相信我們設計團隊能力的,從本案例也可以看到,這個1拖10難度的DDR系統至少有一個通道是成功跑到了額定速率。

高速先生隱隱的感覺到這么大的調試差別,在PCB設計上應該在某些地方有明顯的區別,可能是乍眼一看沒發現吧,因此高速先生一邊在仔細檢閱PCB設計文件,一邊還是去指導客戶去做一些debug的調試,例如讓客戶換一下驅動和ODT的配置,改變一下Vref電壓幅度,甚至讓客戶只焊正面,去掉背面5個顆粒這種操作,但是很遺憾的事,客戶嘗試之后并沒有任何的改善和變化。

正當debug調試陷入僵局的時候,也不知道是不是看PCB文件看到眼花了,隱約發現兩個通道在端接VTT電阻的數量上好像不太一樣??!!!

趕緊猛的揉揉眼睛并而喝口水穩定下情緒,然后再認真的看一次!!!

這下看清楚了,還真是數量不一樣的,上面有問題的通道明顯少了一列VTT電阻,我們趕緊仔細檢查每一根地址控制信號,看看是不是他們在VTT電阻上有差別。

不檢查還好,一檢查不得了!居然有問題的通道有三根信號就沒連接到VTT電阻,也就是說,這三根信號壓根就沒有端接!

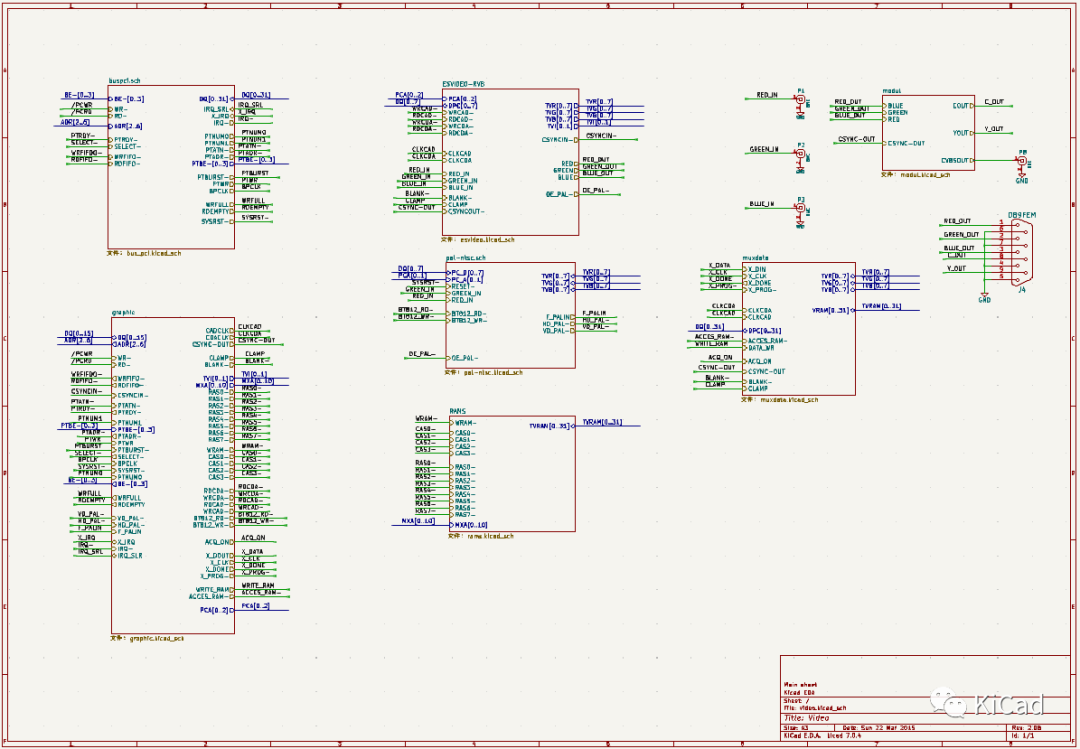

分析到這里,高速先生大概知道問題出在哪里了,在進行仿真來對比有VTT電阻端接和沒有端接的波形之前,我們還想搞清楚到底為什么PCB設計上會漏掉這幾根信號的端接。因此和我們PCB設計工程師確認后,我們要到了客戶的設計原理圖,找到相應的位置,果然有了驚人的發現。

我們找到了部分網表的對比,驚人的發現有問題的通道從客戶的原理圖上就已經漏了這幾根信號的端接,然后我們這邊工程師按照原理圖完成了設計,加工和焊接,板子出來的結果就是這樣了。

好吧,其實問題已經弄清楚了,最后我們再通過仿真來證明下有接端接和沒接端接情況下,信號質量到底能有多大的差異。

經過仿真后,波形結果的確也能很好的和測試情況相對應。

這種沒端接的情況,不要說2400M速率跑不上去,哪怕是降一半頻率,1200M也是妥妥的…有問題!

最后我們的PCB工程師也找到了這個原理圖的問題,并而把高速先生的結論告訴了客戶。

最后高速先生以一句很無奈的話結束了這個項目的debug。

這個時候,希望高速先生快速定位到問題會給客戶帶來一絲絲安慰和后續能快速的進行改板,這個原理圖出錯導致加工出來的DDR系統完全不能啟動的案例,希望能給大家在方案設計上有所思考哈。

審核編輯:符乾江

-

IC設計

+關注

關注

38文章

1296瀏覽量

103928 -

PCB設計

+關注

關注

394文章

4685瀏覽量

85573

發布評論請先 登錄

相關推薦

怎么樣提高verilog代碼編寫水平?

usb主機控制器無法啟動怎么解決

電動機無法啟動的原因有哪些

altium怎么把原理圖導入pcb

Altium怎么把原理圖換成pcb

制作ccomplete bt_hello_sensor,無法啟動 BTM_ENABLE_EVT是哪里的問題?

服務器數據恢復—VMware虛擬機無法啟動的數據恢復案例

利用DX-BST原理圖智能工具實現原理圖對比的技術方法

無法啟動,這個原理圖出錯的水平怎么樣

無法啟動,這個原理圖出錯的水平怎么樣

評論