12月17-18日,以“自立自強,在危機中育新機”為主題的2020中國(上海)集成電路創新峰會在上海科學會堂舉行。本次峰會由上海市經濟和信息化委員會、上海市科學技術委員會和上海推進科技創新中心建設辦公室指導,國家集成電路創新中心、上海市科學技術協會、中國電子學會聯合主辦,上海市集成電路行業協會、上海集成電路產業投資基金、上海市國際科技交流中心、上海科技發展基金會等承辦,峰會還得到了摩爾精英集團等機構的大力支持。 峰會期間,國家科技重大專項(01)專項專家組總體組組長、中國半導體行業協會副理事長、清華大學魏少軍教授帶來了主題為《關于集成電路創新的一些思考》的演講,從集成電路發展歷史到現狀,再到中國發展契機,囊括技術和產業。

筆者大致整理如下: 集成電路自誕生之日起,一直依靠創新驅動發展。計算也從人和物的交互,轉變為當下的機器與機器的交互,5G和AI在過去幾年對社會影響非常大。 集成電路的發展方向分為三個方向,芯片架構創新、微納系統集成、新器件新材料新工藝。這三個方向都是為了推動摩爾定律前行。 關于器件結構的變化,魏少軍表示,功耗曾是器件變革的重要原因。此前,體硅平面晶體管在20nm已經走到盡頭,無法獲得等比例縮小的性能、成本和功耗優勢。

產業界在28nm之后的器件結構選擇上曾經爭論不休,但英特爾公司在22nm節點上成功采用FinFET晶體管后,產業界在14nm節點采用FinFET達成共識。“因此,大公司對器件結構選擇的偏好,也會左右行業的發展,”魏少軍如此說道。此外,FinFET結構被認為可以一直使用到5nm節點,但必須找到降低成本的有效途徑。FD-SOI是一個重要選項,基于FD-SOI的FinFET技術也可能會占有一席之地。

目前來看,晶體管結構和材料也在不斷創新,新型晶體管結構如FinFET,Nanosheet/Nanowire等,新型晶體管材料如High mobilitychannel,2D,CNT等。此處,魏少軍提到全包圍柵晶體管(GAA),在應用了GAA技術后,業內樂觀估計應基本上可以解決3nm乃至更小尺寸的半導體制造問題。 這里的GAA是Gate-All-Around環繞式柵極技術的縮寫,也稱為全包圍柵極靜態技術,特點是實現了柵極對溝道的四面包裹,源極和漏極不再和基底接觸,而是利用線狀、平板狀或者片狀等多個源極和漏極橫向垂直于柵極分布后,實現MOSFET的基本結構和功能。

三星宣稱相比7nm工藝而言,GAA技術電壓可以下降至0.7V,并且能夠提升35%的性能、降低50%的功耗和45%的芯片面積。同時,三星給出工藝過程展示,雖然GAA的制造和FinFET有一定的相似之處,但是其技術要求更高,難度更大,相應成本也更昂貴。 魏少軍提到幾個晶體管相關的創新技術,一個是負電容技術,2008年的時候,美國加州大學伯克利分校的胡正明教授正在試驗中發現,如果在晶體管柵極采用鐵電材料,可以在一定條件下實現負電容效應,從而大大降低晶體管的耗電。

一個是新型二維材料,天然只有三個原子厚度~0.6nm,制造出1nm晶體管。還有分子級晶體管,新型晶體管中的12銦原子以正六邊形排列,每個銦原子的直徑是167皮米。可通過改變銦原子上的電荷分布來改變晶體管中心酞菁分子方向,實現“0”和“1”兩個狀態,但不是傳統晶體管的通斷開關狀態。 目前來看,材料和工藝創新是集成電路制造技術發展的主要任務。

關于芯片架構引領計算領域變革的思考中,魏少軍表示,目前美國和歐洲都在高度重視軟件定義芯片技術的研究。傳統的軟硬件劃分對完成芯片設計來說已經不夠了,芯片的架構設計必須包含芯片和軟件兩部分。而且由于軟件加入而產生的增值也許會超過芯片本身價值。硬件工程師不得不開始介入設計軟件。 魏少軍將目前的處理器歸類到以軟件可編程性為Y軸,硬件可編程性為Z軸的四個象限里(如下圖),其中通用處理器屬于第二象限,專用集成電路屬于第三象限,可編程邏輯器件為第四象限。軟件定義芯片在第一象限里,兼具優異軟硬件可編程性。

據介紹,軟件定義芯片架構的通用控制單元是一個可編程的有限狀態機。它從外部讀取數據流、控制流和配置流信息,即所謂的“軟件”;負責運行與任務對應的狀態流程圖,并以此控制各個子任務的執行,每個狀態對應一組數據通道要執行的子任務,控制數據通道完成配置和執行。 “應用定義軟件,軟件定義芯片”是集成電路設計技術的一次根本變革。目前我國在軟件定義芯片領域的突破早已于世界同行。軟件定義芯片技術是能夠替代ASIC和FPGA的新型電路架構技術,有望為我國集成電路設計業擺脫跟隨模仿、實現趕超,提供一條全新的技術路線。 在集成技術創新開辟摩爾定律延續新路徑的思考方面,魏少軍表示,如今隨著工藝節點不斷微縮,設計成本也在爆炸式增長,但是并非所有的器件都需要最先進的工藝。

比如AMD以實現性能、功耗和成本平衡為目標,提出performance/W和performance/$衡量標準,并推行Chiplet,從而實現了逆襲。 此外,業界在封裝技術上也從2.5D到3D封裝的進階,3D-IC系統集成也逐漸成為了主流。在此,魏少軍提到了英特爾的3D Foveros技術和臺積電的3D SoIC方案。 最后,魏少軍表示,芯片是支撐數字經濟發展的基礎,在可以預見的未來,尚不會出現能夠替代集成電路的其他技術。即使出現了,也需要數十年的時間和花費十數萬億美元才能替代今天的集成電路。 再者,經過60多年的發展,集成電路技術又一次站在岔路口上,主流器件、芯片架構和微納系統集成等三個領域的創新,將是集成電路跨過5nm需要克服的幾個關鍵技術。 器件結構的選擇將決定未來競爭的制高點,架構創新將引領計算領域的變革,而微納系統集成技術將開辟摩爾定律延續新路徑。三者相互支撐,互相影響,是在5nm之后掌握發展主動權的關鍵。

如今,我國在集成電路領域進步很快,但“核心技術受制于人,產品處于中低端”的情況還沒有徹底改觀,基礎研究和基礎人才的培養沒有跟上需求的發展是重要原因。未來十年,我們面臨器件結構更新,計算架構創新和系統集成路徑變革等重大機遇。抓住這些機遇將會大有所為。

原文標題:魏少軍:關于集成電路創新的一些思考

文章出處:【微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

456文章

50950瀏覽量

424763 -

集成電路

+關注

關注

5389文章

11574瀏覽量

362332 -

晶圓

+關注

關注

52文章

4931瀏覽量

128108

原文標題:魏少軍:關于集成電路創新的一些思考

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

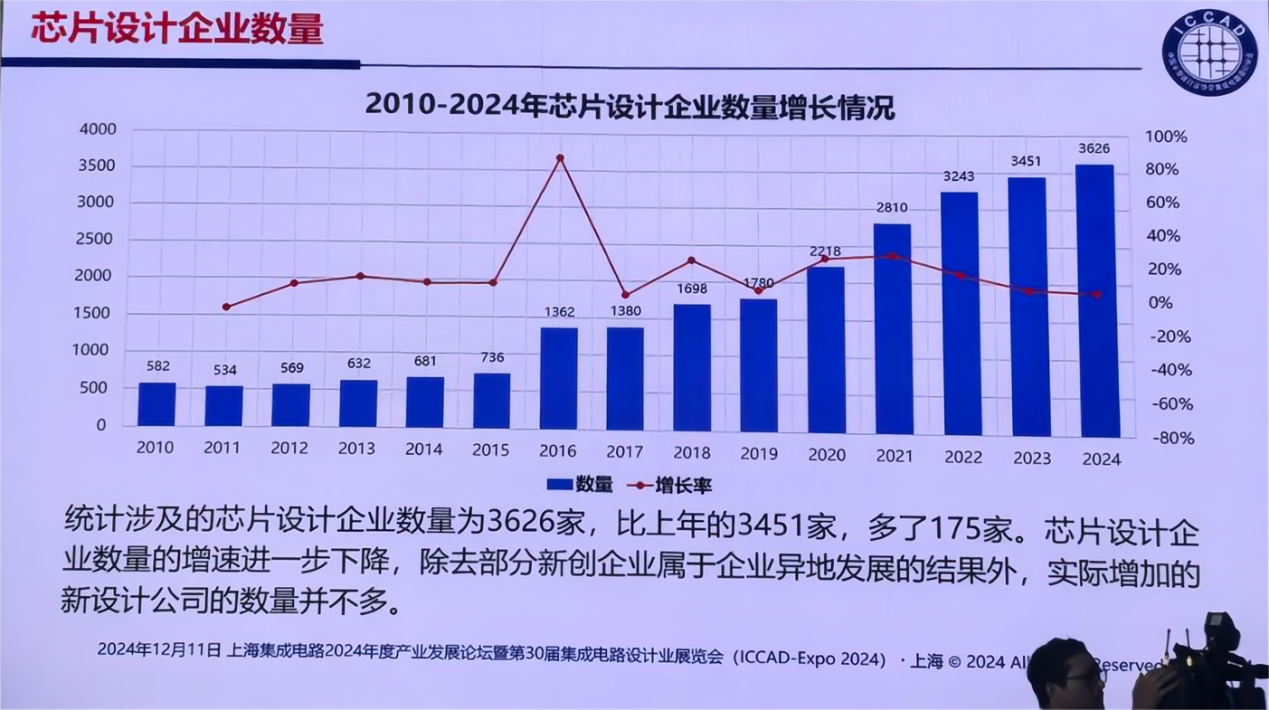

魏少軍:中國IC設計產業增速首次低于全球,該如何自強不息?

魏少軍教授ICCAD2024最新演講:中國芯片設計業要自強不息

魏少軍教授:關于集成電路創新的一些思考

魏少軍教授:關于集成電路創新的一些思考

評論