本文接續上一篇《FPGA雜記基礎篇》,繼續為大家分享IP例化和幾個基于FPGA芯片實現的Demo工程。

IP例化

IP即是一個封裝好的模塊,集成在相應的開發環境里面,以安路的TD軟件為例,不同系列的芯片集成了不同的IP模塊,可以通過軟件例化調用。

以下是安路TD4.6.5集成的EF3L40CG332B的相關IP。

1.1 PLL&RAM

以例化PLL和RAM為例,實現兩個異步雙口 RAM。

讀寫時鐘都設置 100Mhz, 兩個 RAM 為 RAMA 和RAMB, 深度為 1024,位寬為 8bit,寫入數據為 8bit,100Mhz 持續數據流, 當 RAMA被寫入 1024 字節數據后切換到寫 RAMB, RAMB 被寫入 1024 字節后切換 RAMA。以此循環類推。

當 RAMA 被寫入 1024 字節時, 給讀時序提供一個啟動信號讀取 RAMA 的數據, 讀取完 RAMA 的 1024 字節數據時, 切換讀 RAMB 以此類推。

這個工程的工程結構如下圖:

首先EF3L40CG332B_DEV開發板提供了25Mhz的晶振時鐘輸入到EF3L40CG332B的時鐘管腳。

想要得到100Mhz的讀寫速率,需要先用PLL得到倍頻時鐘。

在tools目錄下點擊IP Generator進入IP core頁面,并選擇PLL,輸入時鐘填入板子晶振25Mhz。

輸出時鐘填入所需要的100Mhz,并從C0輸出。

設置完成后,生成的module聲明如下(完整模塊可參考代碼)

再生成ram的IP模塊。

在IP core中選擇RAM。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603979 -

芯片

+關注

關注

456文章

50892瀏覽量

424335 -

電力電子

+關注

關注

29文章

565瀏覽量

48909

發布評論請先 登錄

相關推薦

詳解FPGA的基本結構

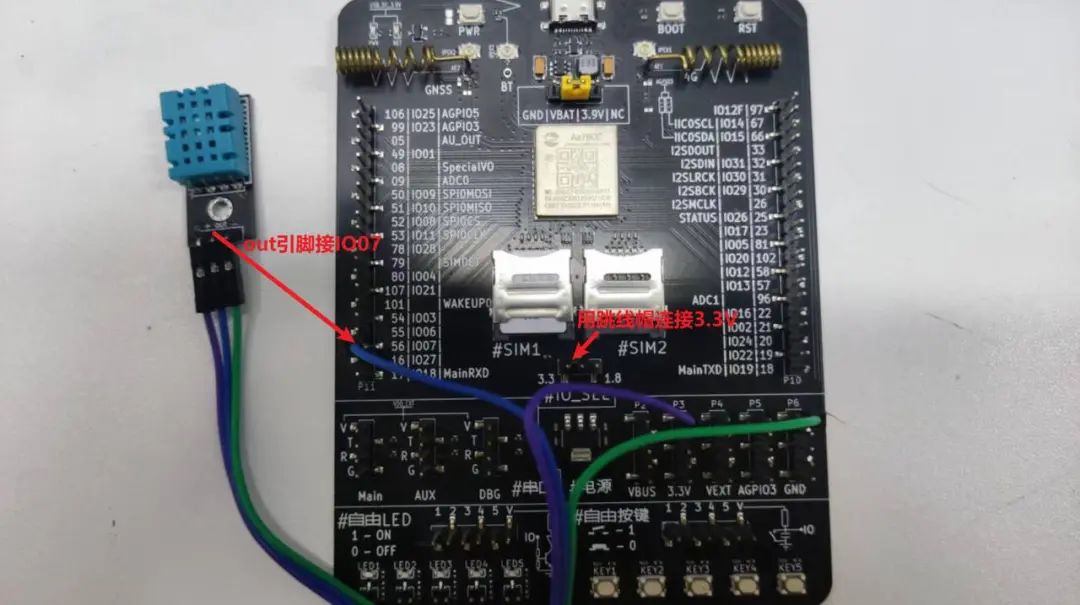

Air780E篇:采集溫濕度傳感器數據,并網頁查看

什么~FPGA可以自行二次開發了?

全新電池管理系統BMS (3串計量芯片) Demo

FPGA設計經驗之圖像處理

Xilinx FPGA編程技巧之常用時序約束詳解

AMD FPGA中MicroBlaze的固化流程詳解

Xilinx FPGA編程技巧之常用時序約束詳解

FPGA雜記之基礎篇二及Demo案例詳解

FPGA雜記之基礎篇二及Demo案例詳解

評論