串擾是通過近電場(電容耦合)和磁場(電感耦合)在相鄰導體之間耦合的噪聲。盡管任何相鄰導體都表現出串擾,但是當它出現在強干擾信號和敏感信號之間時,對信號完整性將造成很大的影響。

串擾的再定義:

攻擊者=高振幅+高頻+短上升時間

受害者=低振幅+高阻抗

某些信號由于其性質或在電路中的功能而對串擾特別敏感,這些信號是潛在的串擾受害者,如:

模擬信號:與數字信號相比,它們對噪聲更敏感,尤其是在振幅較低的情況下。

高阻抗控制信號:使能,復位,振蕩器和反饋信號是控制類信號。如果此類信號是由低阻抗源產生的,則它們很容易受到電容串擾的干擾。

另一類信號很容易在受害者身上引起噪聲,并被認為是串擾的潛在攻擊者。為了識別潛在的攻擊者,請記住串擾是由PCB走線之間的耦合電容和電感引起的。基于這些考慮,電路中的潛在攻擊者是:

高振幅信號(電壓或電流)

快速信號(上升時間短或者高頻)

最小化串擾的基本規則:使攻擊者和受害者盡可能遠離。

具體規則如下:

二帶狀線布置

串擾的明顯對策是使攻擊者和受害者盡可能遠離,以避免耦合電容和電感。這樣做的第一步是避免在同一層上有攻擊者和受害者。

布線層之間的參考平面將大大減少這些層上信號之間的串擾,因此,如果可能,將攻擊者和受害者分配給至少由接地層或供電層隔開的不同層。

帶狀線層上的串擾比微帶線層上的串擾小,因此,如果攻擊者和受害者必須共享同一區域和同一層,則它應該是帶狀線層。

三正交布線

通過為每個層分配單個方向并交替相鄰層的方向,可以大大減少電容耦合和電感耦合。該技術稱為“正交布線”,如圖1所示。

圖1 正交布線

當不能應用正交布線或對于沒有被參考平面分隔的具有相同布線方向的層時,也可以通過交錯信號跡線來減少串擾,如圖2所示。

圖2 交錯布線

四平行布線

如果無法在不同層上布置攻擊者和受害者,則應強制按照并行走線要求進行布線。平行走線之間的串擾噪聲量取決于平行走線的長度和它們之間的間隙。間隙越小,對于相同的串擾量,允許并行走線的長度越短。串擾不僅取決于并行度,而且還取決于信號和PCB特性。

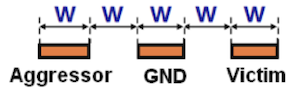

關于并行布線的經驗法則稱為“ 3W規則”,意思是為了避免在同一層布線的平行走線之間發生串擾,走線中心之間的最小間距應保持3W,圖3說明了3W規則。

圖3 3W規則

雖然通過應用3W規則確實可以減少串擾,但實際的3W值會導致電路板面積增大,可能很昂貴。因此通常在前邊規則無法滿足要求的情況下才使用3W規則。

五地防護線

減少在同一層上布線的平行走線之間串擾的另一種措施是使用兩端都接地的走線(稱為保護走線)將它們分開。圖4中必須將保護走線的所有末端都接地,否則它將像天線一樣把干擾帶出去。

圖4 地防護

對防護技術的實驗研究表明,通過簡單地將受害者與攻擊者分開,即使不存在防護走線,也可以實現相同的串擾降低(這等效于4W并行度規則)。但是,保護走線也會對周圍環境的電磁干擾產生有益的影響,因此,仍然建議保留地線來減少強干擾信號和敏感信號的串擾。

保護走線會影響信號走線的特征阻抗和傳輸時間,如果將其應用于高速信號線需考慮信號完整性!

原文標題:如何解決EMC設計中的串擾問題

文章出處:【微信公眾號:韜略科技EMC】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

信號

+關注

關注

11文章

2789瀏覽量

76730 -

emc

+關注

關注

170文章

3914瀏覽量

183121

原文標題:如何解決EMC設計中的串擾問題

文章出處:【微信號:TLTECH,微信公眾號:韜略科技EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高頻電路設計中的串擾問題

嵌入式開發中引起串擾的原因是什么?

PCB產生串擾的原因及解決方法

如何使用SigXplorer進行串擾的仿真

怎么樣抑制PCB設計中的串擾

如何解決EMC設計中的串擾問題?

如何解決EMC設計中的串擾問題?

評論