這是《創建 Vitis 加速平臺》系列的第 3 篇博文。在前文中,我們講解了如何創建硬件和軟件工程。在本文中,我們將講解如何在 Vitis 中將所有這些工程封裝在一起。

在 Vitis 中加速軟件功能(創建內核)即表示創建硬件 IP 核,并使用由此產生的基礎架構將此功能連接到現有平臺。

為此,Vitis 需要重構平臺。Vitis 使用 XSA 來重構 Vivado 工程。隨后,它將追加經過更新的硬件,并重新創建 Vivado 工程。

其它所有一切都保持不變,當然比特流和生成的內核應用除外。因此,啟動鏡像不能保持不變。而是由我們提供 BIF 文件,并在其中包含鏡像占位符用于在 Vitis 中創建這些鏡像。

此外,為了能夠執行內核,我們需要為目標硬件執行交叉編譯。此處使用的是 PetaLinux 中創建的 sysroot。

準備鏡像

為了便于使用,我在此對平臺文件進行了組織,但這并非必要步驟。重要的是,請牢記創建 BIF 文件時的啟動鏡像位置,因為我們使用的是占位符。

mkdir -p sw_comp/src/a53/xrt/image mkdir sw_comp/src/boot

將 image.ub、boot.scr 和 rootfs.cpio.gz 從 PetaLinux image/linux 文件夾復制到 sw_comp/src/a53/xrt/image

將 bl31.elf、uboot.elf、zynqmp_fsbl(已重命名為 fsbl.elf)和 pmufw.elf 從 PetaLinux image/linux 文件夾復制到 sw_comp/src/boot

創建 BIF

BIF 文件在 bootgen 中用于創建 SD 啟動鏡像。

其中包括 BOOT.BIN 文件中所有分區的位置。以下提供了一個模板。

此處請務必注意,我們只提供占位符文件名,而不提供實際文件名。工具將添加指向這些文件的路徑。因此,我建議將所有這些文件保存在相同啟動文件夾內。zcu104_base 將用作為平臺名稱。

the_ROM_image: { [fsbl_config] a53_x64 [bootloader]

將 linux.bif 復制到 sw_comp/src/boot

創建 init.sh 腳本

啟動時將運行此腳本以進行 XRT 設置,并將平臺名稱傳遞到 ZOCL。

將 init.sh 復制到 sw_comp/src/a53/xrt/image

cp ./platform_desc.txt /etc/xocl.txt export XILINX_XRT=/usr

將 init.sh 復制到

sw_comp/src/a53/xrt/image

創建 platform_desc.txt

這樣即可將平臺名稱傳遞到 XRT。此處名稱應與 Vivado 中提供的平臺名稱匹配:

zcu104_base

將 platform_desc.txt 復制到

sw_comp/src/a53/xrt/image

創建 QEMU 文件

Vitis IDE 支持軟件仿真和硬件仿真。QEMU 即可用于執行此操作。但我們需要傳遞 QEMU 機器詳細信息。

針對 PMU,需使用 pmu_args.txt 執行此操作

-M microblaze-fdt -device loader,file=

將 pmu_args.txt 復制到 sw_comp/src/boot

此外還需要通過 qemu_args.txt 傳遞 PSU 機器詳細信息:

-M arm-generic-fdt -serial mon:stdio -global xlnx,zynqmp-boot.cpu-num=0 -global xlnx,zynqmp-boot.use-pmufw=true -net nic -net nic -net nic -net nic -net user -m 4G -device loader,file=

將 qemu_args.txt 復制到

sw_comp/src/boot

在 Vitis 中封裝平臺

啟動 Vitis 并選擇“創建平臺工程 (Create Platform Project)”:

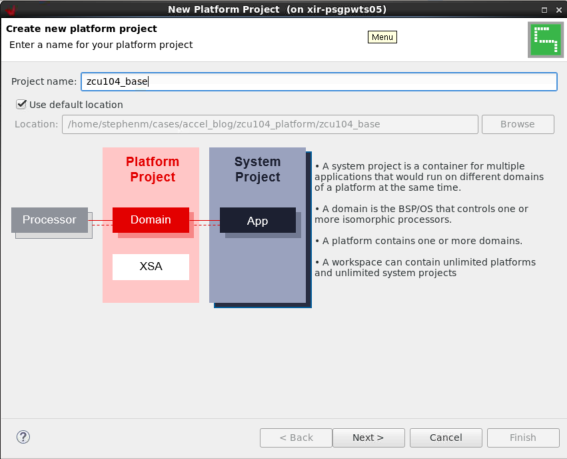

使用 BIF 中所提供的名稱:

選擇“根據硬件規范 (XSA) 創建 (Create from hardware specification (XSA))”:

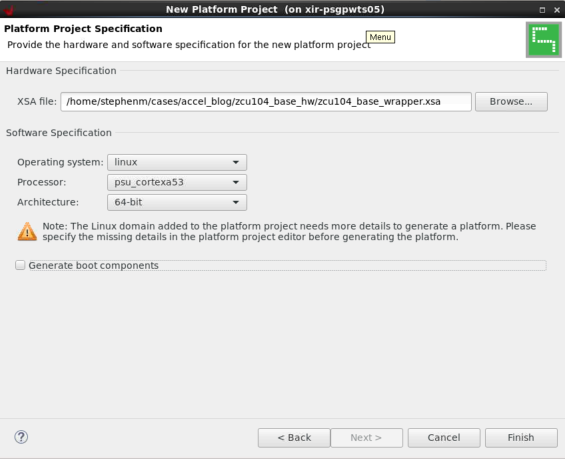

針對操作系統選擇 Linux,然后取消勾選“生成啟動組件 (generate boot components)”,因為在 PetaLinux 中已創建這些組件:

注:此處警告信息僅用于聲明需添加 sysroot。

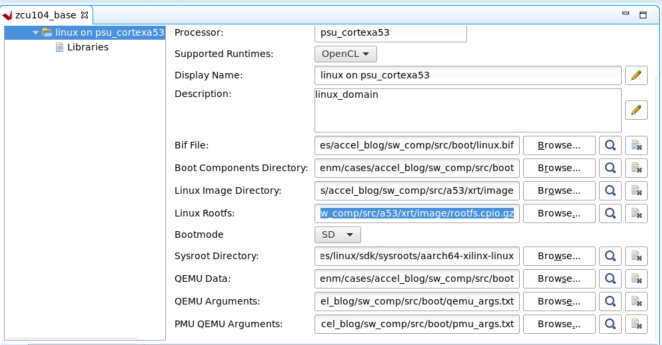

填入上一篇博文中創建的軟件鏡像:

然后執行構建:

完成此操作后,平臺將置于 exportzcu104_base.... 至此大功告成。

原文標題:創建 Vitis 加速平臺第 3 部分:在 Vitis 中封裝加速平臺

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

封裝

+關注

關注

126文章

7873瀏覽量

142894 -

Vitis

+關注

關注

0文章

146瀏覽量

7421

原文標題:創建 Vitis 加速平臺第 3 部分:在 Vitis 中封裝加速平臺

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMD Vitis Unified Software Platform 2024.2發布

GPU加速計算平臺是什么

如何在SOT-563封裝和SOT-236封裝之間實現共同布局

在Windows 10上創建并運行AMD Vitis?視覺庫示例

Vitis2023.2使用之—— updata to Vitis Unified IDE

Vitis2023.2使用之—— classic Vitis IDE

Micro LED中封裝技術的選擇

Vitis2023.2全新GUI的功能特性介紹

如何在Vitis中封裝加速平臺?

如何在Vitis中封裝加速平臺?

評論