EDA工具的出現,手動到自動的跨越

1958年誕生的芯片拉開了人類社會邁向信息社會的序幕,并逐漸形成了芯片產業。1965年,摩爾提出“由于工程師可以不斷縮小晶體管的體積,芯片中的晶體管和電阻器的數量每年會翻番”,此后又修正為“每隔24個月,晶體管的數量將翻番”。彼時,芯片上的元件大約只有60種,設計人員依靠手工完成芯片的設計、布線等工作。 從20世紀60年代中期開始,業界先后出現包括通過幾何軟件生成單色曝光圖像圖形化工具,第一個自動化的電路布局和布線工具等,這些工具奏響了EDA發展的序曲。80年代開始,隨著VHDL、Verilog、以及仿真器的出現,芯片設計仿真和可執行的設計有了其規范化的硬件描述語言和標準。

1986年新思科技創始人Aart de Geus博士發明了具有劃時代意義的邏輯綜合工具。邏輯綜合工具的出現,使原本用單個門來手動設計芯片電路的工程師用電腦語言來“寫”電路的功能,能夠通過邏輯綜合進行設計實現,極大提升了芯片設計的效率,從而讓工程師將更多精力集中在創造性的設計上。這項發明無論當時還是現在,都具有劃時代的意義,加速了芯片開發的進程,使大規模芯片開發變為可能,讓人類有機會在今天設計出包含數百億個晶體管的復雜芯片。

EDA工具推動芯片行業沿著摩爾預測的路徑發展,從10μm逐步演進到如今的5nm,芯片規模逐漸擴大,電子系統變得越發復雜。從系統架構開始,落實到功能的定義和實現,最終實現整個芯片的版圖設計與驗證,是一項復雜的系統工程,匯聚了人類智慧的最高成果。以蘋果2020年發布的新款A14芯片為例,這款芯片采用5nm工藝制造,將118億顆晶體管集成在面積僅為88平方毫米的內核上,靠手工已經無法完成。

2

邏輯綜合對于EDA設計領域來說是一個偉大的成就,能夠把描述RTL級的HDL語言翻譯成GTECH,然后再優化和映射成工藝相關的門級網表,作為輸入給自動布局布線工具生成GDSII文件用于芯片制造。新思科技的Design Compiler自1986年推出以來,得到全球幾乎所有的芯片供應商、IP供應商和庫供應商的支持和應用,到90年代中期,Design Compiler已經成為RTL邏輯綜合的事實標準,讓設計人員的生產力提高至10倍。Design Compiler作為業界歷史最悠久的設計實現工具,經過30年的不斷發展和技術積累,提供最可靠設計實現優化和性能結果,是目前業界使用最為廣泛的ASIC設計實現工具。

新思科技并未止步于一時的技術領先,而是前瞻性地預判到行業未來的發展趨勢和市場需求,持續對Design Compiler系列產品進行研發投資,帶來一次次突破性的創新綜合技術。例如,新思科技將Design Compiler升級迭代為Design Compiler Graphical,加入物理綜合,即在綜合前加入版圖的布局規劃信息(floorplan),然后調用庫信息和約束條件,生成帶有布局信息的門級設計結果,進一步提高了綜合與布局布線結果的相關一致性,不僅可以更精準地估算連線延時,還可以預測布線擁堵情況并進行相應優化。 Design Compiler系列產品已經引領市場超過30年,新思科技一次次以尖端的EDA技術,為當今極度復雜的前沿設計提供了有力支持。新版Design Compiler NXT集成了最新的綜合創新技術,支持5nm以下工藝,能夠大幅度縮短運行時間、實現具有絕對優勢的QoR,同時滿足了諸如人工智能(AI)、云計算、5G和自動駕駛等半導體市場對更小體積、更高性能、更低功耗的芯片需求,以及對研發周期越來越高的要求。

3

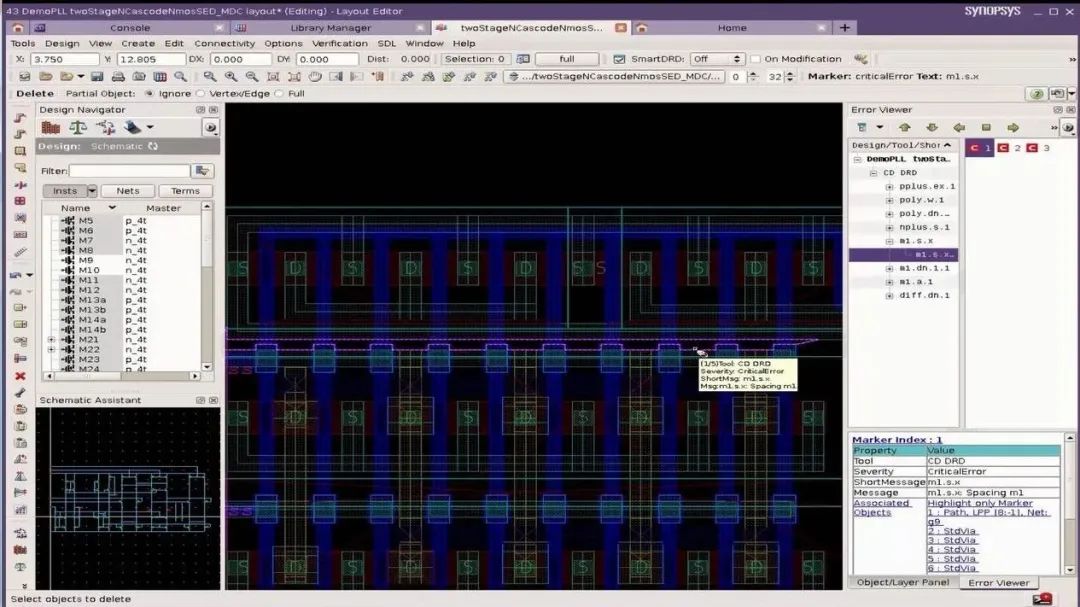

Fusion Compiler推動數字設計邁進新紀元

從2000年開始,由于復雜性日益增加,過程節點和設計時間持續縮減,使得在仍然能夠提供更好的結果和更快交付的同時,管理設計成本變得十分關鍵。于是新思科技開始著手開發一個全面的、緊密集成的實現平臺—— Galaxy Implementation Platform,能夠將芯片物理實現所需的所有工具集成到一個協調的環境中,簡化了工程師從一個工具變換到另一個工具的復雜度,有助于提高生產力并降低出錯幾率。IC Compiler是該平臺的一個主要組件,為設計人員提供了一個單一、聚合、芯片級物理實現工具,該工具實現了卓越的設計結果質量(QoR)、交付時間更短、設計成本減少以及易用性等優點。 進入21世紀, EDA技術開始深入制造領域,并與晶圓廠建立緊密的合作,將EDA工具的使用從制造不斷擴展到標準單元庫、SRAM設計。而隨著領先晶圓廠每兩年開發一代工藝,不斷推動摩爾定律向前,EDA工具需要在早期工藝研發中介入,以確保芯片的設計能夠在新工藝上被精確應用、最終成功制造,EDA在產業鏈的作用更加凸顯。新思科技作為目前全世界唯一一家覆蓋了從硅的生產制造、芯片測試、到設計全流程的EDA公司,既能夠在芯片制造的所有流程環節提供核心技術和軟件,又能夠為芯片設計的全流程提供核心技術軟件的EDA和IP,有力推動了產業生態圈的良性合作。 工藝和設計的不斷發展,要求前后端有更好的一致性,以便更快速的收斂。新思科技推出創新性的RTL-to-GDSII產品Fusion Compiler,通過把新型高容量綜合技術、行業領先的布局布線技術、以及業界領先的golden signoff技術融合到統一可擴展的數據模型中,同時引入諸多機器學習技術,利用Fusion Compiler可以在最短的時間內提供同類最佳的設計實現質量,能夠更好地預測QoR,以應對行業最先進設計對更高性能、更低功耗、可靠性、安全性的要求。

Fusion Compiler是業界唯一的從RTL到GDSII解決方案,能夠實現前后端統一數據模型、統一的設計和優化引擎,讓整個設計實現中保持良好的一致性,促進了設計實現性能提升,加快了工具實現的時間和設計收斂的速度。同時,引入機器學習技術,對設計的實現和優化進行加速,顯著提高設計收斂的速度。這樣的融合技術已被市場領先的半導體公司進行了充分驗證,能夠提供最高質量的設計,包括通過臺積電5nm、3nm和三星5nm、3nm等最先進工藝的技術認證。

4

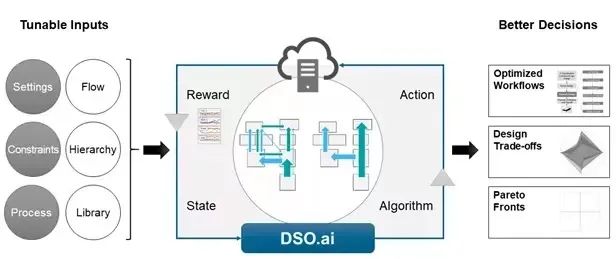

DSO.ai開啟芯片智能設計

當前,芯片行業正在經歷一個技術進步和創新浪潮的復興時期。人工智能、5G、自動駕駛等新興領域技術的不斷發展對芯片設計帶來全新的挑戰,包括工藝要求提升、豐富的應用場景、整體設計規模以及成本等。EDA工具進入2.0時代,其未來的發展著重在兩個大的方向,一是應用目前豐富的算力,提高并行和分布式處理能力,提升設計效率;二是更多的應用AI技術,促進設計的探索自動化,減少可替代的人工努力,解放工程師資源到更具創造性的工作。 新思科技于2020年初推出了業界首個用于芯片設計的智能化軟件——DSO.ai(Design Space Optimization AI),這是電子設計技術上又一次突破性技術,能夠在芯片設計的巨大求解空間里搜索優化目標。該解決方案大規模擴展了對芯片設計流程選項的探索,能夠自主執行次要決策,幫助芯片設計團隊以專家級水平進行操作,并大幅提高整體生產力,從而在芯片設計領域掀起新一輪革命。三星已經采用新思科技DSO.ai實現性能、功耗與面積優化上的進一步突破。原本需要多位設計專家耗時一個多月才可完成的設計,DSO.ai只要短短3天即可完成,提速近10倍。

在摩爾定律走向極限、電子領域急需轉變突破的關鍵點、人工智能和量子等新興技術及產業不斷涌現的當下,新一代EDA(NG-EDA)的呼聲越來越高。DSO.ai這種AI驅動的設計方法將引領EDA進入2.0時代——支持大規模并行運算、可部署在云端的EDA智能化設計系統。 EDA作為整個電子產業的根技術,從最初作為輸入與仿真的工具確保芯片的正確設計、到通過優化與映射確保芯片設計的最佳性能、再到如今不斷提升自主化和智能化來引領芯片設計,EDA通過自身的不斷演進和迭代升級,將保障芯片的持續創新,為人類邁入數字經濟時代提供源源不斷的動力。

原文標題:從EDA技術演變看芯片創新之未來

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

455文章

50803瀏覽量

423503 -

IC

+關注

關注

36文章

5948瀏覽量

175582 -

eda

+關注

關注

71文章

2758瀏覽量

173253 -

新思科技

+關注

關注

5文章

798瀏覽量

50337

原文標題:從EDA技術演變看芯片創新之未來

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

從MCU到SoC:汽車芯片核心技術的深度剖析

從特斯拉看智能駕駛未來發展

兆易創新推出EtherCAT從站控制芯片

概倫電子榮獲“中國芯”EDA技術創新獎

西門子EDA全面賦能芯片創新

從IC設計到系統創新,新思科技為AI創新提速

飛凌嵌入式技術創新日(深圳站)精彩回顧

思爾芯亮相CCF Chip 2024,展示創新EDA技術與產學研合作

AI+EDA加速雙向賦能,引領萬物智能時代的創新

芯片新戰場,EDA如何擁抱新挑戰?

從EDA技術演變里看芯片創新之未來

從EDA技術演變里看芯片創新之未來

評論