在大數據和人工智能盛行的今天,金融科技(Fintech)領域數據日益密集和敏感,在高頻交易、風險分析等金融應用由來已久卻一直不溫不火,高處不勝寒的賽靈思FPGA,迎來了前所未有的市場熱潮。

FPGA 在 Fintech 領域之所以受青睞,歸功于其內部擁有豐富且靈活的邏輯與計算單元,可以支持定制低延時、高吞吐率的設計,從而一方面能夠為Fintech提供遠超軟件實現的性能優勢,另一方面還可以為金融企業提供可以跟隨最新科技演進而發展的靈活應變成本優勢。然而,曾經高高在上的FPGA也一直被一些用戶詬病使用“門檻”太高。

換句話說,開發人員在采用FPGA產品時必須在技能上“軟硬兼備”,既要軟件,還要會硬件。而且,寫RTL 代碼和驗證耗時耗力,在分秒必爭,時間就是金錢的金融行業,開發者們面對FPGA 是愛恨交織,如那句歌詞“想說愛你并不是很容易的事,那需要太多的勇氣“

正當開發者們苦苦糾結時,賽靈思兩款劃時代“利器”橫空出世,將FPGA的開發難度“從金字塔尖拉到了金字塔底”,大幅降低了軟件和硬件程序員開發FPGA應用的難度:從此,軟硬件程序員開發FPGA應用可以信手拈來,再也不必受那分配管腳、手寫RTL的苦。那么,這兩件利器是什么呢?那就是賽靈思Vivado HLS高層次綜合工具和Alveo自適應計算加速器板卡。為什么它們這么神奇呢?請聽我細細道來。

壹

高層次綜合工具:Vivado HLS

Vivado HLS是一款能將C/C++代碼轉化為RTL代碼的自動轉化工具,其自帶驗證、封裝等功能。開發者只需將頂層C/C++程序配合C/C++驗證代碼,通過軟件驗證,而后就可以用Vivado HLS將其轉化為RTL代碼。其次,Vivado HLS可以利用原有C/C++驗證代碼協同生成RTL代碼,進行仿真并驗證功能正確性。最后,Vivado HLS支持一鍵封裝并生成IP,供Vivado工具或SDAccel開發環境使用。

圖1:Vivado HLS工具算法流程

這么簡單?性能從何而來? 那就是Vivado HLS設計套件強大的性能:它能利用指令流水線(pipeline)、任務級流水(dataflow)和操作展開(unroll)功能,實現所有操作在時間軸上片刻不停地運轉,而這些只需輕點鼠標,插入幾條指令(pragma)即可實現。

圖2:Vivado HLS中的并行處理

貳

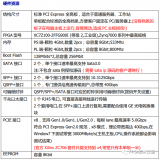

自適應加速器卡:Alveo

我們再來看看Alveo 板卡能給我們帶來什么,它又強大在哪里。Alveo賽靈思為適應靈活應變、萬物智能的新時代而推出的自適應加速器卡系列,它配有標準PCIE、網口(可達100G),還提供了整套部署及開發的軟件堆棧,使開發者可以通過安裝軟件包輕松部署。同時,Alveo還配備了殼(shell),可以將PCIE、DMA等功能固化,開發者只需開發最具創新性的、專有的內核(kernel),使用標準的AXI-4接口,即可自動將內核與殼相連,生成完整的平臺硬件。在軟件層面,開發者只需調用Open CL或賽靈思提供的API,即可完成所有板卡調度、數據傳輸等任務。

圖3:Alveo及SDAccel開發環境的平臺模型和執行模型

Alveo自適應加速器卡的適用領域非常廣泛,如數據庫、機器學習、圖像處理、壓縮及解壓縮、加密及解密、金融計算等,每個領域里Alveo都有著出色的加速應用。盡管Alveo的加速倍數根據應用的不同而有所不同,但是在一些適合并行的領域,往往可以提供更加驚人的表現,例如,在不損失精度的情況下,歐式期權定價可以比CPU快3,000倍以上。下圖展示的就是Alveo在賽靈思及合作伙伴的多個領域的應用。

圖4:Alveo加速實例

開啟 Fintech 開發新時代

軟件擁有SDAccel開發環境及調度庫(runtime),硬件擁有Alveo自適應加速器卡和殼,設計上擁有Vivado HLS來開發定制化需求,加之豐富的案例和開源的實際應用,賽靈思為金融科技領域的開發者開啟了一個輕松上手FPGA加速的開發新時代。

此外,賽靈思還收購了在全球金融機構赫赫有名的 Solarflare公司,大大增強賽靈思在Fintech領域的實力,可以為客戶提供低延時網卡和各種金融領域定制化應用。

與此同時,賽靈思還打造了全方位的Fintech生態系統。公司不僅為開發者提供了一系列工具,還提供了多種IP,甚至一些金融領域的特殊需求,如TOE(TCP/UDP Offload Engine),也有相應開源HLS幫助實現。在HLS基礎庫中,涵蓋了定點庫、數學函數庫、線性代數庫等,而在更高層,賽靈思還實現了模塊級及軟件API級的HLS開源,如矩陣運算庫等。

除自身提供全套工具及開源庫,賽靈思還與獨立軟件提供商(ISV)共同提供各種解決方案。這些ISV往往擁有自己獨特的解決方案,而賽靈思要做的就是對他們的應用提供支持,以滿足眾多領域的需求。在Fintech領域,這些應用包含:

一鍵下單(Tic To Trade);

交易權風控;

解包及發包;

期權定價等等。

最快甚至可以實現納秒(ns)級的下單。在中國市場,從以太網收到交易所包到解包再到計算完成,整個流程可以在百毫微秒級實現。

圖6:SDAccel工具鏈級Fintech平臺示例

總之,賽靈思Vivado HLS和Alveo的到來,Fintech開發迎來了一個FPGA加速的新時代。開發人員無需在硬件平臺搭建與基礎支持工具上投入過多精力,而只需專注于自己的特長領域,借助Vivado HLS快速在Alveo加速器卡實現定制化應用,不斷突破低延時、高吞吐率的極限。

最后,如果您想親身實踐感受上述性能,強烈推薦賽靈思現有一款產品:二叉樹期權定價模型。它簡單易用、容易上手,同時可以實現比12核CPU高達60.8倍的加速,您可以點擊鏈接查看體驗https://github.com/Xilinx/BinomialModel。

圖7:Binomial期權定價模型

責任編輯:xj

原文標題:愛(AI)其實很簡單 — 金融科技(Fintech)開發迎來新時代

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604387 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131348 -

AI

+關注

關注

87文章

31156瀏覽量

269500

原文標題:愛(AI)其實很簡單 — 金融科技(Fintech)開發迎來新時代

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

易靈思FPGA產品的主要特點

Diodes推出兩款USB Sink控制器

思瑞浦推出兩款創新非同步升壓控制器與轉換器

萊迪思推出全新Certus-NX FPGA器件,加強低功耗、小型FPGA的領先地位

賽思快訊 | 發展新質生產力問道賽思?賽思如何下好“創新棋”?

森思泰克發布兩款全新激光雷達產品

開啟移動智慧屏+AI娛樂時代!Talenpal探樂派閨蜜機重磅亮相

Zynq-7000為何不是FPGA?

國產FPGA應用專題--易靈思Efinity軟件使用心得

AMD進軍低成本FPGA市場,滿足邊緣應用需求

解析FPGA競爭格局背后的驅動因素

賽靈思兩款劃時代“利器” 讓開發FPGA應用可以信手拈來

賽靈思兩款劃時代“利器” 讓開發FPGA應用可以信手拈來

評論