一、中斷概念

操作系統(tǒng)中,中斷是很重要的組成部分。出現(xiàn)某些意外情況需主機(jī)干預(yù)時(shí),機(jī)器能自動(dòng)停止正在運(yùn)行的程序并轉(zhuǎn)入處理新情況的程序,處理完畢后又返回原被暫停的程序繼續(xù)運(yùn)行。

有了中斷系統(tǒng)才可以不用一直輪詢(polling)是否有事件發(fā)生,系統(tǒng)效率才得以提高。

一般在系統(tǒng)中,中斷控制分為三個(gè)部分:「模塊、中斷控制器和處理器」。

其中模塊通常由寄存器控制是否使能中斷和中斷觸發(fā)條件等;中斷控制器可以管理中斷的優(yōu)先級(jí)等,而處理器則由寄存器設(shè)置用來(lái)響應(yīng)中斷。

二、GIC

作為 ARM 系統(tǒng)中通用中斷控制器的是 GIC(Generic Interrupt Controller),目前有四個(gè)版本,V1~V4(V2最多支持8個(gè)ARM core,V3/V4支持更多的ARM core,主要用于ARM64系統(tǒng)結(jié)構(gòu))。

【注意】對(duì)于一些老的ARM處理器,比如ARM11,Cortex-A8,中斷控制器一般是VIC(向量中斷控制器)。

1. GIC-400

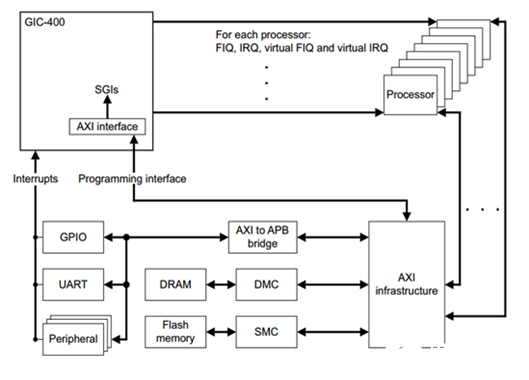

下面以GIC-400為例,它更適合嵌入式系統(tǒng),符合v2版本的GIC architecture specification。GIC-400通過(guò)AMBA(Advanced Microcontroller Bus Architecture)片上總線連接到一個(gè)或者多個(gè)ARM處理器上。

GIC中斷控制器全局圖

從上圖可以看出, GIC 是聯(lián)系外設(shè)中斷和 CPU 的橋梁,也是各 CPU 之間中斷互聯(lián)的通道(也帶有管理功能),它負(fù)責(zé)檢測(cè)、管理、分發(fā)中斷,可以做到:

使能或禁止中斷;把中斷分組到Group0還是Group1(Group0作為安全模式使用連接FIQ ,Group1 作為非安全模式使用,連接IRQ );多核系統(tǒng)中將中斷分配到不同處理器上;設(shè)置電平觸發(fā)還是邊沿觸發(fā)方式(不等于外設(shè)的觸發(fā)方式);虛擬化擴(kuò)展。

ARM CPU 對(duì)外的連接只有2 個(gè)中斷:「IRQ和FIQ」 ,相對(duì)應(yīng)的處理模式分別是一般中斷(IRQ )處理模式和快速中斷(FIQ )處理模式。所以GIC 最后要把中斷匯集成2 條線,與CPU 對(duì)接。

GIC中斷控制器結(jié)構(gòu)

分發(fā)器:負(fù)責(zé)各個(gè)子中斷使能,設(shè)置觸發(fā)方式,優(yōu)先級(jí)排序,分發(fā)到哪個(gè) CPU 上;接口:負(fù)責(zé)總的中斷的使能,狀態(tài)的維護(hù)。

2. 分發(fā)器功能

分發(fā)器的主要的作用是檢測(cè)各個(gè)中斷源的狀態(tài),控制各個(gè)中斷源的行為,分發(fā)各個(gè)中斷源產(chǎn)生的中斷事件到指定的一個(gè)或者多個(gè)CPU接口上。雖然分發(fā)器可以管理多個(gè)中斷源,但是它總是把優(yōu)先級(jí)最高的那個(gè)中斷請(qǐng)求送往CPU接口。分發(fā)器對(duì)中斷的控制包括:

(a)中斷使能或禁能控制。分發(fā)器對(duì)中斷的控制分成兩個(gè)級(jí)別,一個(gè)是全局中斷的控制(GIC_DIST_CTRL),一旦禁止了全局的中斷,那么任何的中斷源產(chǎn)生的中斷事件都不會(huì)被傳遞到CPU接口;另外一個(gè)級(jí)別是對(duì)針對(duì)各個(gè)中斷源進(jìn)行控制(GIC_DIST_ENABLE_CLEAR),禁止某一個(gè)中斷源會(huì)導(dǎo)致該中斷事件不會(huì)分發(fā)到CPU接口,但不影響其他中斷源產(chǎn)生中斷事件的分發(fā)。(b)控制將當(dāng)前優(yōu)先級(jí)最高的中斷事件分發(fā)到一個(gè)或者一組CPU接口。(c)優(yōu)先級(jí)控制。(d)中斷屬性設(shè)定,例如是電平觸發(fā)還是邊沿觸發(fā)。(e)中斷的設(shè)定。

分發(fā)器可以管理若干個(gè)中斷源,這些中斷源用ID來(lái)標(biāo)識(shí),我們稱之interrupt ID。

3. CPU接口功能

CPU接口主要用于和CPU進(jìn)行接口。

主要功能包括:

(a)使能或者禁止CPU接口向連接的CPU提交中斷事件。對(duì)于ARM,CPU接口和CPU之間的中斷信號(hào)線是nIRQCPU和nFIQCPU。如果禁止了中斷,那么即便是分發(fā)器分發(fā)了一個(gè)中斷事件到CPU接口,但是也不會(huì)提交指定的nIRQ或者nFIQ通知CPU。(b)ackowledging中斷。CPU會(huì)向CPU接口應(yīng)答中斷,中斷一旦被應(yīng)答,分發(fā)器就會(huì)把該中斷的狀態(tài)從pending狀態(tài)修改成active,如果沒有后續(xù)pending的中斷,那么CPU 接口就會(huì)deassert nIRQCPU和nFIQCPU信號(hào)線。如果在這個(gè)過(guò)程中又產(chǎn)生了新的中斷,那么分發(fā)器就會(huì)把該中斷的狀態(tài)從pending狀態(tài)修改成pending and active。此時(shí),CPU接口仍然會(huì)保持nIRQ或者nFIQ信號(hào)的asserted狀態(tài),也就是向CPU通知下一個(gè)中斷。(c)中斷處理完畢的通知。當(dāng)中斷處理器處理完了一個(gè)中斷的時(shí)候,會(huì)向?qū)慍PU 接口的寄存器從而通知GIC已經(jīng)處理完該中斷。做這個(gè)動(dòng)作一方面是通知分發(fā)器將中斷狀態(tài)修改為deactive,另外一方面,可以允許其他的pending的中斷向CPU接口提交。(d)設(shè)定優(yōu)先級(jí)掩碼。通過(guò)優(yōu)先級(jí)掩碼可以mask掉一些優(yōu)先級(jí)比較低的中斷,這些中斷不會(huì)通知到CPU。(e)設(shè)定中斷搶占的策略。(f)在多個(gè)中斷事件同時(shí)到來(lái)的時(shí)候,選擇一個(gè)優(yōu)先級(jí)最高的通知CPU。

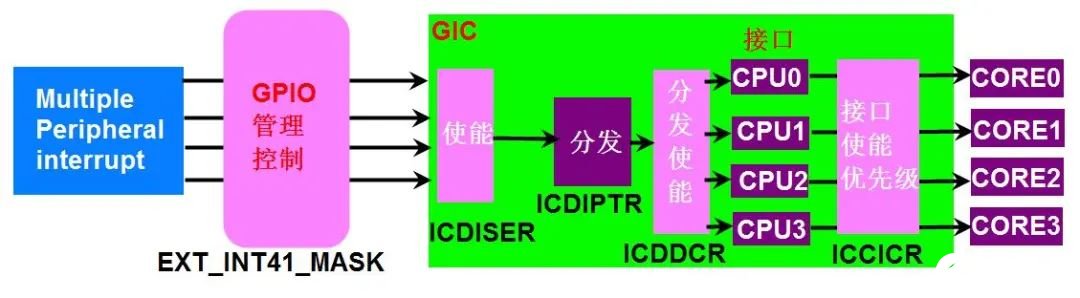

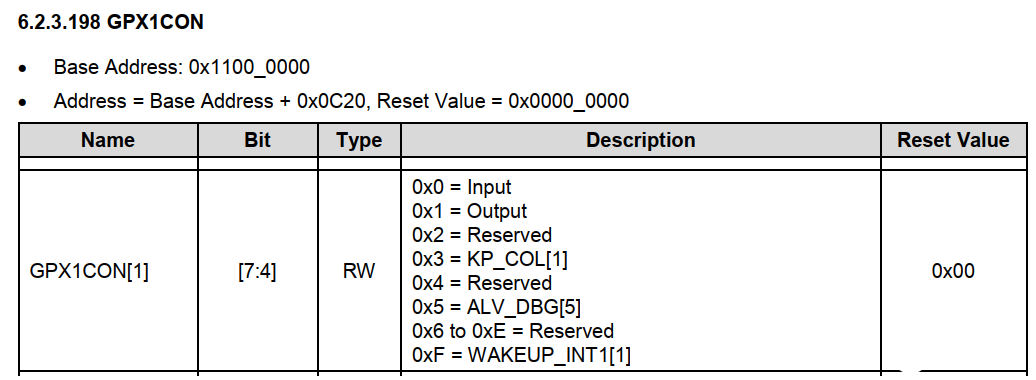

key中斷管理模塊圖

以上圖為例,該圖是按鍵產(chǎn)生的中斷信號(hào)要到達(dá)cpu所要經(jīng)過(guò)的路徑。

外設(shè)中斷源有很多,通常芯片廠商會(huì)設(shè)計(jì)若干個(gè)第一級(jí)中斷控制器,進(jìn)行第一次處理,key連接的是GPX1中斷控制器,寄存器EXT_INT41_M(jìn)ASK用于使能該中斷;GIC主要包括分排氣和cpu interface;ICDISER用于使能分派器,ICDIPTR用于將中斷信號(hào)分發(fā)給對(duì)應(yīng)的cpu interface;ICCICR用于使能CPU interface;CPU上有兩個(gè)引腳irq、fiq,gic最終會(huì)連接到CPU的irq,所有寄存器配置完畢后,按鍵一旦按下,那么就會(huì)給CPU的irq發(fā)送一個(gè)中斷信號(hào),cpu緊接著就會(huì)執(zhí)行“4大步3小步”,進(jìn)入中斷異常處理流程。

三、中斷分類

1. 中斷源硬件中斷(Hardware Interrupt)可屏蔽中斷(maskable interrupt)。硬件中斷的一類,可通過(guò)在中斷屏蔽寄存器中設(shè)定位掩碼來(lái)關(guān)閉。非可屏蔽中斷(non-maskable interrupt,NMI)。硬件中斷的一類,無(wú)法通過(guò)在中斷屏蔽寄存器中設(shè)定位掩碼來(lái)關(guān)閉。典型例子是時(shí)鐘中斷(一個(gè)硬件時(shí)鐘以恒定頻率—如50Hz—發(fā)出的中斷)。處理器間中斷(interprocessor interrupt)。一種特殊的硬件中斷。由處理器發(fā)出,被其它處理器接收。僅見于多處理器系統(tǒng),以便于處理器間通信或同步。偽中斷(spurious interrupt)。一類不希望被產(chǎn)生的硬件中斷。發(fā)生的原因有很多種,如中斷線路上電氣信號(hào)異常,或是中斷請(qǐng)求設(shè)備本身有問(wèn)題。軟件中斷(Software Interrupt)

軟件中斷SWI,是一條CPU指令,用以自陷一個(gè)中斷。由于軟中斷指令通常要運(yùn)行一個(gè)切換CPU至內(nèi)核態(tài)的子例程,它常被用作實(shí)現(xiàn)系統(tǒng)調(diào)用(System call)。

外部中斷I/O設(shè)備:如顯示器、鍵盤、打印機(jī)、A / D轉(zhuǎn)換器等。數(shù)據(jù)通道:軟盤、硬盤、光盤等。數(shù)據(jù)通道中斷也稱直接存儲(chǔ)器存取(DMA)操作中斷,如磁盤、磁帶機(jī)或CRT等直接與存儲(chǔ)器交換數(shù)據(jù)所要求的中斷。實(shí)時(shí)時(shí)鐘:如外部的定時(shí)電路等。在控制中遇到定時(shí)檢測(cè)和控制,為此常采用一個(gè)外部時(shí)鐘電路(可編程)控制其時(shí)間間隔。需要定時(shí)時(shí),CPU發(fā)出命令使時(shí)鐘電路開始工作,一旦到達(dá)規(guī)定時(shí)間,時(shí)鐘電路發(fā)出中斷請(qǐng)求,由CPU轉(zhuǎn)去完成檢測(cè)和控制工作。用戶故障源:如掉電、奇偶校驗(yàn)錯(cuò)誤、外部設(shè)備故障等。產(chǎn)生于CPU內(nèi)部的中斷源由CPU得運(yùn)行結(jié)果產(chǎn)生:如除數(shù)為0、結(jié)果溢出、斷點(diǎn)中斷、單步中斷、存儲(chǔ)器讀出出錯(cuò)等。執(zhí)行中斷指令swi非法操作或指令引起異常處理。2. 中斷類型

GIC 中斷類型有3種:SGI(Software-generated interrupt)、PPI(Private peripheral interrupt )、SPI(Shared peripheral interrupt)。

SGI: SGI為軟件可以觸發(fā)的中斷,統(tǒng)一編號(hào)為0~15(ID0-ID7是不安全中斷,ID8-ID15是安全中斷),用于各個(gè)core之間的通信。該類中斷通過(guò)相關(guān)聯(lián)的中斷號(hào)和產(chǎn)生該中斷的處理器的CPUID來(lái)標(biāo)識(shí)。通常為邊沿觸發(fā)。

PPI: PPI為每個(gè) core 的私有外設(shè)中斷,統(tǒng)一編號(hào)為 16-31 。例如每個(gè) CPU 的 local timer 即 Arch Timer 產(chǎn)生的中斷就是通過(guò) PPI 發(fā)送給 CPU 的(安全為29,非安全為30)。

通常為邊沿觸發(fā)和電平觸發(fā)。

SPI: SPI 是系統(tǒng)的外設(shè)產(chǎn)生的中斷,為各個(gè) core 公用的中斷,統(tǒng)一編號(hào)為 32~1019 ,如 global timer 、uart 、gpio 產(chǎn)生的中斷。通常為邊沿觸發(fā)和電平觸發(fā)。

Note:電平觸發(fā)是在高或低電平保持的時(shí)間內(nèi)觸發(fā), 而邊沿觸發(fā)是由高到低或由低到高這一瞬間觸發(fā);在GIC中PPI和SGI類型的中斷可以有相同的中斷ID。

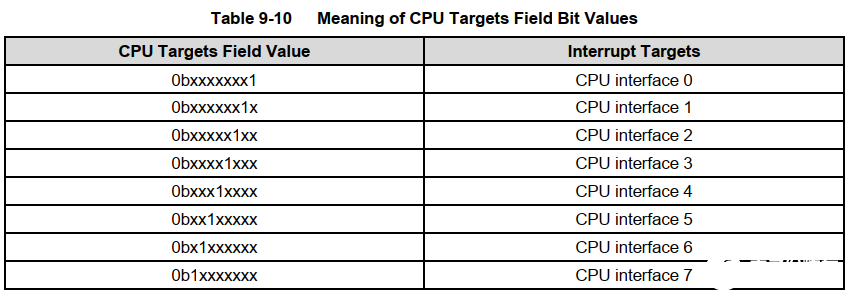

3. 中斷分派模式

1-N mode (SPIs using the GIC 1-N model)表示中斷可以發(fā)給所有的CPU,但只能由一個(gè)CPU來(lái)處理中斷;換句話說(shuō),這種類型的中斷有N個(gè)目標(biāo)CPU,但只能由其中一個(gè)來(lái)處理;當(dāng)某一個(gè)處理器應(yīng)答了該中斷,便會(huì)清除在所有目標(biāo)處理器上該中斷的掛起狀態(tài)。

N-N mode (PPIs and SGIs using the GIC N-N model)表示中斷可以發(fā)給所有CPU,每個(gè)CPU可以同時(shí)處理該中斷。當(dāng)該中斷被某一個(gè)處理器應(yīng)答了,這不會(huì)影響該中斷在其他CPU接口上的狀態(tài)。

舉兩個(gè)例子說(shuō)明:

1)UART 接收到一包數(shù)據(jù),產(chǎn)生了一個(gè)中斷給GIC,GIC可以將該中斷分配給CPU0-7中任何一個(gè)處理;假設(shè)該中斷分配給CPU0處理了,那么在中斷處理函數(shù)里面會(huì)把接收到的數(shù)據(jù)從UART FIFO讀出。可以想象一下,如果CPU0在讀數(shù)據(jù)時(shí),另外一個(gè)CPU也在處理該中斷,恰巧也在讀數(shù)據(jù),那么CPU0讀到的數(shù)據(jù)是不全的。這就是1-N model中斷,或者說(shuō)SPI中斷。

2)比如CPU0給CPU1-7發(fā)送中斷,想告知對(duì)方自己正在處理某個(gè)進(jìn)程A。這種場(chǎng)景下,CPU1-7都接收到中斷,都進(jìn)入中斷處理函數(shù),CPU1-7獲取到CPU0的信息后,在進(jìn)程調(diào)度時(shí),就可以繞開進(jìn)程A,而自己調(diào)度其他進(jìn)程。

注:這個(gè)例子只是說(shuō)明N-N model,實(shí)際上進(jìn)程調(diào)度不都全是這樣的。

4. 通用中斷處理

當(dāng)GIC接收到一個(gè)中斷請(qǐng)求,將其狀態(tài)設(shè)置為Pending。重新產(chǎn)生一個(gè)掛起狀態(tài)的中斷不影響該中斷狀態(tài)。

中斷處理順序:

① GIC決定該中斷是否使能,若沒有被使能對(duì)GIC沒有影響;

② 對(duì)于每個(gè)Pending中斷,GIC決定目標(biāo)處理器;

③ 對(duì)于每個(gè)處理器 ,Distributor根據(jù)它擁有的每個(gè)中斷優(yōu)先級(jí)信息決定最高優(yōu)先級(jí)的掛起中斷,將該中斷傳遞給目標(biāo)CPU Interface;

④ GIC Distributor將一個(gè)中斷傳遞給CPU Interface后,該CPU Interface決定該中斷是否有足夠的優(yōu)先級(jí)將中斷請(qǐng)求發(fā)給CPU;

⑤ 當(dāng)CPU開始處理該異常中斷,它讀取GICC_IAR應(yīng)答中斷。讀取的GICC_IAR獲取到中斷ID,對(duì)于SGI,還有源處理器ID。中斷ID被用來(lái)查找正確的中斷處理程序。

GIC識(shí)別讀過(guò)程后,將改變?cè)撝袛嗟臓顟B(tài):

a) 當(dāng)中斷狀態(tài)變?yōu)閍ctive時(shí),如果該中斷掛起狀態(tài)持續(xù)存在或者中斷再次產(chǎn)生,中斷狀態(tài)將從Pending轉(zhuǎn)化為pending & active

b) 否則,中斷狀態(tài)將從pending狀態(tài)變?yōu)閍ctive

⑥ 當(dāng)中斷完成中斷處理后,它需要通知GIC處理已經(jīng)完成。這個(gè)過(guò)程稱為 priority drop and interrupt deactivation:

a) 總是需要向EOIR寄存器寫入一個(gè)有效的值(end of interrupt register)b) 也需要接著向GICC_DIR寫入值(deactivate interrupt register)

5. 中斷優(yōu)先級(jí)

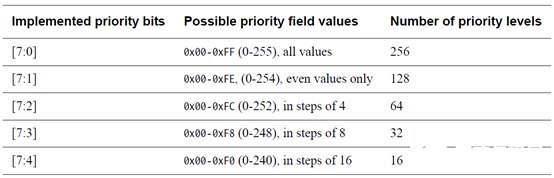

軟件可以通過(guò)給每一個(gè)中斷源分配優(yōu)先級(jí)值來(lái)配置中斷優(yōu)先級(jí)。優(yōu)先級(jí)的值是個(gè)8位的無(wú)符號(hào)二進(jìn)制數(shù),GIC支持最小16和最大256的優(yōu)先級(jí)級(jí)別。

如果GIC實(shí)現(xiàn)的優(yōu)先級(jí)少于256,那么優(yōu)先級(jí)字段的低階位為RAZ/WI。這就意味著實(shí)現(xiàn)的優(yōu)先級(jí)字段個(gè)數(shù)范圍是4~8,如下圖所示:

Effect of not implementing some priority field bits

Note:

1)、如何確定優(yōu)先級(jí)字段所支持的優(yōu)先級(jí)位?通過(guò)軟件往可寫GICD_IPRIORITYn優(yōu)先級(jí)字段寫入0XFF,然后回讀出該字段的值便可以確定優(yōu)先級(jí)字段所支持的優(yōu)先級(jí)位(因?yàn)橛行┪粵]實(shí)現(xiàn)是RAZ/WI)

2)、ARM 推薦在檢查中斷優(yōu)先級(jí)范圍之前先:? 對(duì)于外設(shè)中斷,軟件先禁用該中斷? 對(duì)于SGI,軟件先檢查該中斷確定為inactive

6. 中斷搶占

在一個(gè)active中斷處理完之前,CPU interface支持發(fā)送更高優(yōu)先級(jí)的掛起中斷到目標(biāo)處理器。這種情況必要條件如下:

該中斷的優(yōu)先級(jí)高于當(dāng)前CPU interface 被屏蔽的優(yōu)先級(jí)該中斷的組優(yōu)先級(jí)高于正在當(dāng)前CPU interface處理的中斷優(yōu)先級(jí)7. 中斷屏蔽

CPU interface的GICC_PMR寄存器定義了目標(biāo)處理器的優(yōu)先級(jí)閥值,GIC僅上報(bào)優(yōu)先級(jí)高于閥值的pending中斷給目標(biāo)處理器。寄存器初始值為0,屏蔽所有的中斷。

四、FS4412中斷外設(shè)-key

下面我們來(lái)分析FS4412開發(fā)板的第一個(gè)中斷設(shè)備按鍵。

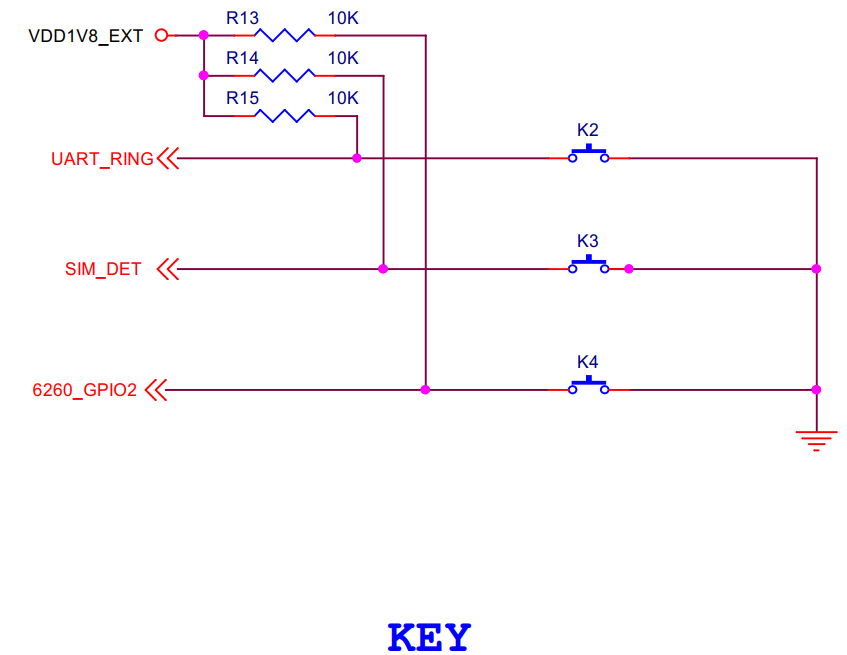

1. 電路圖

key

由該電路圖可得:

按鍵k2 連接在GPX1_1引腳

控制邏輯k2 按下 ---- K2閉合 ---- GPX1_1 低電壓k2 常態(tài) ---- K2打開 ---- GPX1_1 高電壓

以下是key2與soc的連接,

key與soc的連接

可以看到key2復(fù)用了GPIX1_1這個(gè)引腳,同時(shí)該引腳還可以作為中斷【XEINT9】使用。

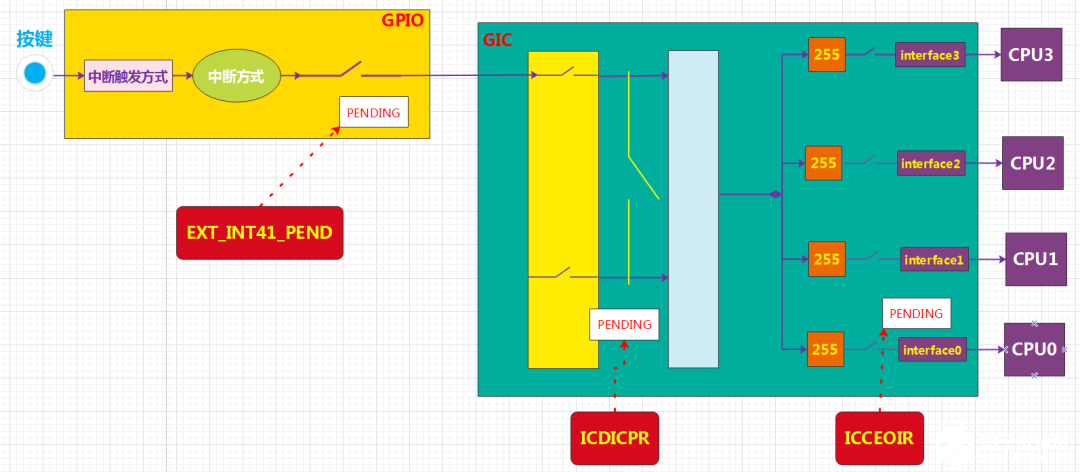

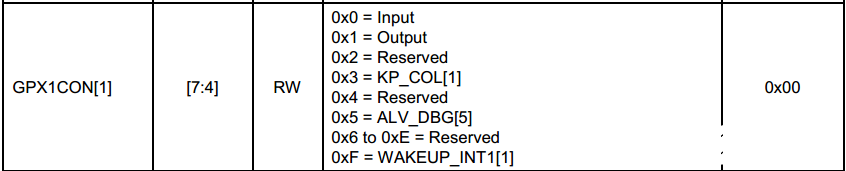

順便看下GPXCON寄存器的配置

GPX1CON

由上圖所示,

GPX1CON地址為0x1100C20;key2如果要做為輸入設(shè)備,只需要將GPX1CON[7:4]設(shè)置為0x0;key2如果要做為中斷信號(hào),只需要將GPX1CON[7:4]設(shè)置為0xf。2. key中斷處理中斷配置

key與soc的關(guān)系圖如下圖所示:

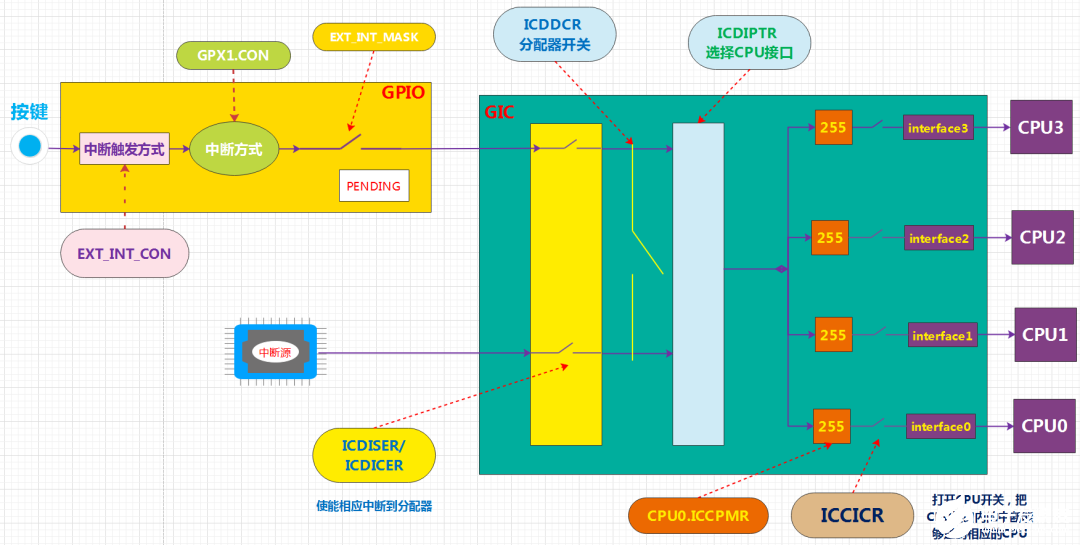

按鍵中斷寄存器配置流程

由上圖所示:

按鍵是直接連到GPIO控制器的EXT_INT_CON用來(lái)設(shè)置按鍵中斷的觸發(fā)方式,下降沿觸發(fā)GPX1CON寄存器用于設(shè)置該GPIO位中斷信號(hào)輸入EXT_INT_M(jìn)ASK用于使能該中斷ICDISER用于使能相應(yīng)中斷到分配器ICDDCR分配器開關(guān)ICDIPTR選擇CPU接口ICCPMR設(shè)置中斷屏蔽優(yōu)先級(jí)ICCICR打開CPU開關(guān),把CPU接口內(nèi)的中斷能夠送到相應(yīng)的CPU清中斷

CPU處理完中斷,需要清除中斷,對(duì)于按鍵來(lái)說(shuō),有3個(gè)寄存器需要操作:

清中斷

由上圖所示:

EXT_INT41_PEND清相應(yīng)的中斷源ICDICPR中斷結(jié)束后,清相應(yīng)中斷標(biāo)志位,此標(biāo)志位由硬件置位ICCEOIR中斷執(zhí)行結(jié)束,清cpu內(nèi)相應(yīng)的中斷號(hào),由硬件填充3. 寄存器匯總

前面分析了按鍵連接的是GPX1_1,現(xiàn)在我們來(lái)看下對(duì)應(yīng)的寄存器應(yīng)該如何配置

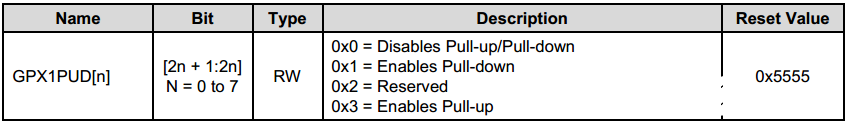

【1】、GPIO控制器GPX1PUD

將GPX1_1引腳的上拉和下拉禁止

GPX1PUD[3:2]= 0b00;

GPX1CON

GPX1CON

將GPX1_1引腳功能設(shè)置為中斷功能

GPX1CON[7:4] = 0xf

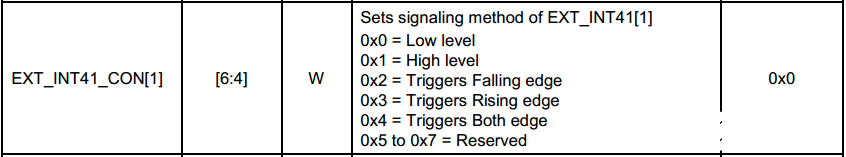

EXT_INT41CON

EXT_INT41CON

配置成成下降沿觸發(fā):

EXT_INT41CON[6:4] = 0x2

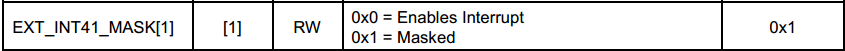

EXT_INT41_M(jìn)ASK

EXT_INT41_M(jìn)ASK

中斷使能寄存器

EXT_INT41_M(jìn)ASK[1] = 0b0

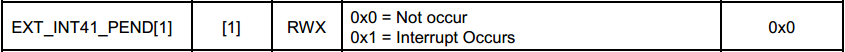

EXT_INT41_PEND 中斷狀態(tài)寄存器

EXT_INT41_PEND

當(dāng)GPX1_1引腳接收到中斷信號(hào),中斷發(fā)生,中斷狀態(tài)寄存器EXT_INT41_PEND 相應(yīng)位會(huì)自動(dòng)置1注意:中斷處理完成的時(shí)候,需要清除相應(yīng)狀態(tài)位。置1清0.

EXT_INT41_PEND[1] =0b1

【2】GIC

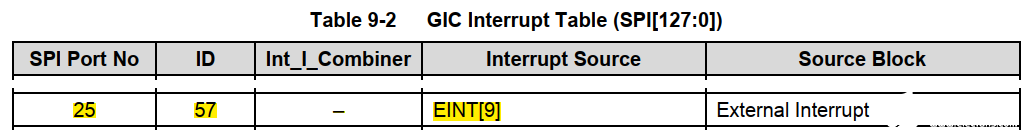

根據(jù)外設(shè)中斷名稱EINT9來(lái)查看該中斷對(duì)應(yīng)的GIC中維護(hù)的HW id。【所有的中斷源在芯片廠商設(shè)計(jì)的時(shí)候都分配了唯一的一個(gè)ID,GIC通過(guò)該ID來(lái)驅(qū)動(dòng)中斷源】

查看芯片手冊(cè)(datasheet -- 9.2表)

GIC中斷源表

通過(guò)【9.2中斷源表】找到和外設(shè)中斷標(biāo)示對(duì)應(yīng)的中斷控制器中斷標(biāo)識(shí)(GPIO有32個(gè)可被喚醒寄存器)其對(duì)應(yīng)「EINT[9],中斷ID為57」,這是非常重要的,在后面的寄存器設(shè)置中起很大作用;

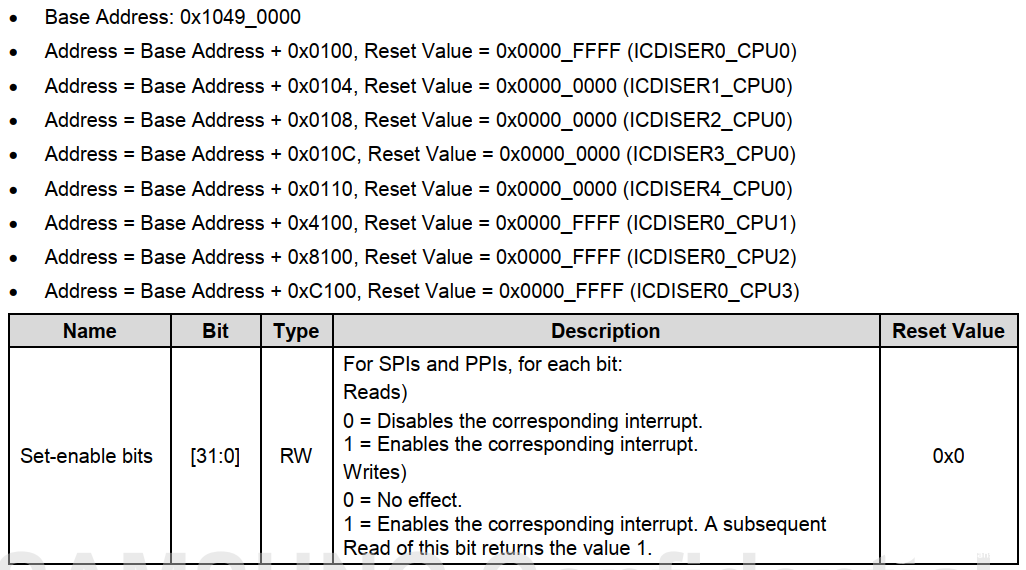

1) ICDISER使能相應(yīng)中斷到分配器

ICDISER

ICDISER用于使能相應(yīng)中斷到分配器,一個(gè)bit控制一個(gè)中斷源,一個(gè)ICDISER可以控制32個(gè)中斷源,這里INT[9] 對(duì)應(yīng)的中斷ID為57,所以在ICDSER1中進(jìn)行設(shè)置,57/32 =1余25,所以這里在ICDISER1第25位置一。

ICDISER.ICDISER1 |= (0x1 << 25); //57/32 =1...25 取整數(shù)(那個(gè)寄存器) 和余數(shù)(哪位)

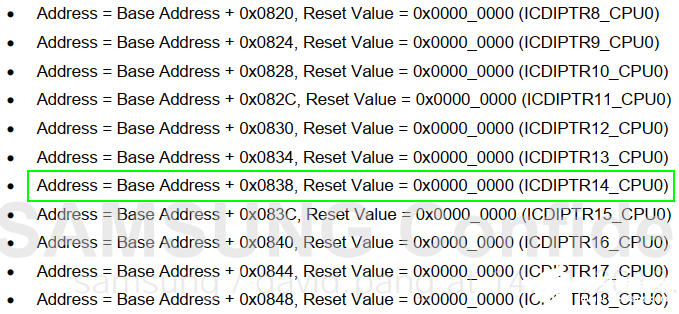

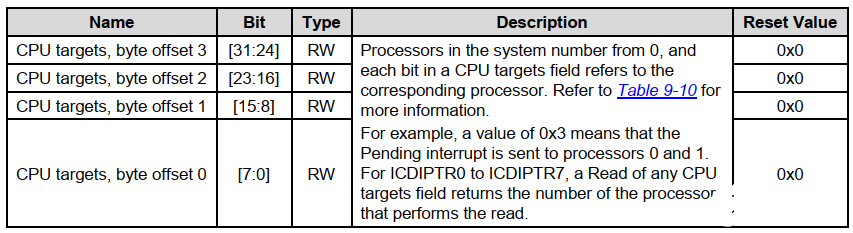

ICDIPTR選擇CPU接口

ICDIPTR

ICDIPTR

選擇cpu

ICDIPTR寄存器每8個(gè)bit 控制一個(gè)中斷源,其中CPU0可以處理160個(gè)中斷源,所以需要40個(gè)寄存器。要選擇cpu0第一個(gè)bit必須是1。

設(shè)置SPI[25]/ID[57]由cpu0處理,57/4=16余1 所以選擇寄存器ICDIPTR14的第2個(gè)字節(jié)[15:8]。

//SPI 25 interrupts are sent to processor 0

//57/4 = 14..1 14號(hào)寄存器的[15:8]

ICDIPTR.ICDIPTR14 |= 0x01<<8;

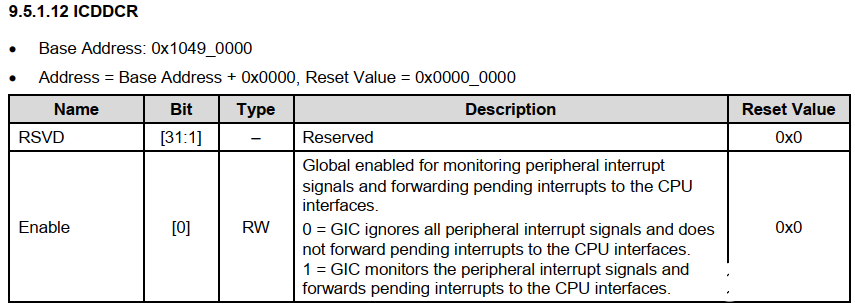

ICDDCR使能分配器

還寄存器用于使能分配器。

ICDDCR =1;

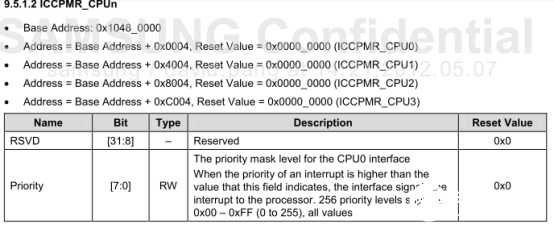

ICCPMR優(yōu)先級(jí)屏蔽寄存器,設(shè)置cpu0能處理所有的中斷。比如中斷屏蔽優(yōu)先級(jí)為255,該值表示優(yōu)先級(jí)最低,所有的中斷都能響應(yīng)。

ICCPMRCPU0.ICCPMR = 0xFF;//設(shè)置cpu0 中斷屏蔽優(yōu)先級(jí)為255 最低,所有中斷都能響應(yīng))

ICCICR 全局使能cpu0中斷處理

ICCICR

EXYNOS 4412一共有4個(gè)cpu,用4個(gè)寄存器分別來(lái)控制4個(gè)cpu,每個(gè)寄存器的bit[0]用于全局控制對(duì)應(yīng)的cpu。我們選擇cpu0處理中斷,將bit[0]置1即可。

CPU0.ICCICR |= 0x1;

使能中斷到CPU。

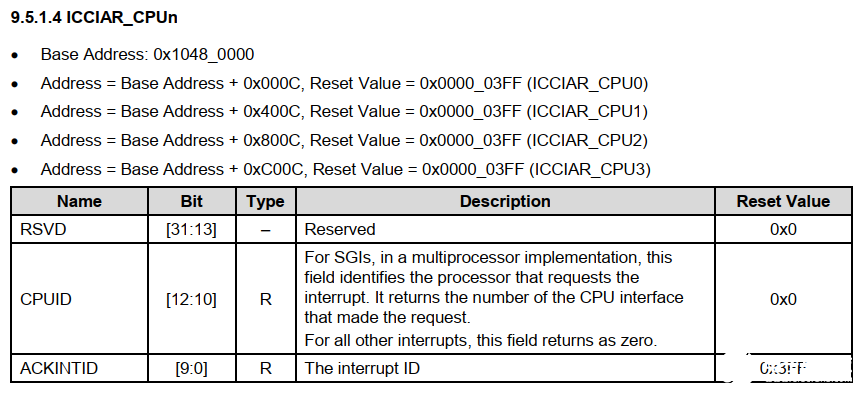

ICCIAR

ICCIAR

當(dāng)中斷發(fā)生之后,中斷的HW id值會(huì)由硬件寫入到寄存器ICCIAR[9:0]中;對(duì)于SGIs來(lái)說(shuō),多處理器環(huán)境下,CPU的interface值寫入到[12:10]中。

讀取HW id:

int irq_num;

irq_num = CPU0.ICCIAR&0x3ff; //獲取中斷號(hào)

五、代碼實(shí)現(xiàn)

要處理中斷異常,必須安裝異常向量表,異常的處理流程可以參考前面的文章《6. 從0開始學(xué)ARM-異常、異常向量表、swi》

1. 異常向量表基址

異常向量表地址是可以修改的,比如uboot在啟動(dòng)的時(shí)候,會(huì)從flash中搬運(yùn)代碼到RAM中,而flash的異常向量表地址和ram的地址肯定不一樣,所以搬運(yùn)完代碼后,就必須要修改對(duì)應(yīng)的異常向量表地址。

修改異常向量表的地址的需要借助協(xié)處理器指令mcr:

ldr r0,=0x40008000

mcr p15,0,r0,c12,c0,0 @ Vector Base Address Register

上述命令是將地址0x40008000設(shè)置為異常向量表的地址,關(guān)于mcr指令,我們沒有必要深究,知道即可。

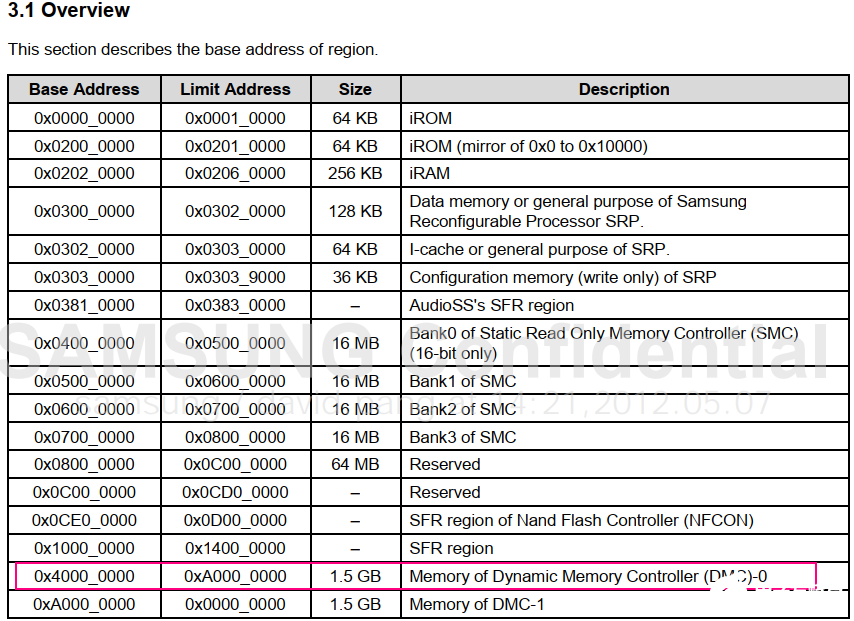

RAM中異常向量表地址我們選用的是0x40008000,以下是exynos4412 地址空間分布。

exynos4412 地址分布2. 異常向量表安裝.text

.global _start

_start:

b reset

ldr pc,_undefined_instruction

ldr pc,_software_interrupt

ldr pc,_prefetch_abort

ldr pc,_data_abort

ldr pc,_not_used

ldr pc,=irq_h(yuǎn)andler

ldr pc,_fiq

reset:

ldr r0,=0x40008000

mcr p15,0,r0,c12,c0,0 @ Vector Base Address Register

init_stack:

//初始化棧

……

b main //跳轉(zhuǎn)至c的main函數(shù)

irq_h(yuǎn)andler: //中斷入口函數(shù)

sub lr,lr,#4

stmfd sp!,{r0-r12,lr}

.weak do_irq

bl do_irq

ldmfd sp!,{r0-r12,pc}^

stacktop: .word stack+4*512//棧頂

.data

stack: .space 4*512 //棧空間

中斷入口函數(shù)do_irq()

void do_irq(void)

{

static int a = 1;

int irq_num;

irq_num = CPU0.ICCIAR&0x3ff; //獲取中斷號(hào)

switch(irq_num)

{

case 57:

printf("in the irq_h(yuǎn)andler");

//清GPIO中斷標(biāo)志位

EXT_INT41_PEND = EXT_INT41_PEND |((0x1 << 1));

//清GIC中斷標(biāo)志位

ICDICPR.ICDICPR1 = ICDICPR.ICDICPR1 | (0x1 << 25);

break;

}

//清cpu中斷標(biāo)志

CPU0.ICCEOIR = CPU0.ICCEOIR&(~(0x3ff))|irq_num;位

}

實(shí)現(xiàn)按鍵中斷的初始化函數(shù)key_init():

void key_init(void)

{

GPX1.CON =GPX1.CON & (~(0xf << 4)) |(0xf << 4); //配置引腳功能為外部中斷

GPX1.PUD = GPX1.PUD & (~(0x3 << 2)); //關(guān)閉上下拉電阻

EXT_INT41_CON = EXT_INT41_CON &(~(0xf << 4))|(0x2 << 4); //外部中斷觸發(fā)方式

EXT_INT41_M(jìn)ASK = EXT_INT41_M(jìn)ASK & (~(0x1 << 1)); //使能中斷

ICDDCR = 1; //使能分配器

ICDISER.ICDISER1 = ICDISER.ICDISER1 | (0x1 << 25); //使能相應(yīng)中斷到分配器

ICDIPTR.ICDIPTR14 = ICDIPTR.ICDIPTR14 & (~(0xff << 8))|(0x1 << 8); //選擇CPU接口

CPU0.ICCPMR = 255; //中斷屏蔽優(yōu)先級(jí)

CPU0.ICCICR = 1; //使能中斷到CPU

return ;

}

六、輪詢方式

除了中斷方式之外我們還可以通過(guò)輪詢方式讀取按鍵的信息,原理如下:

循環(huán)檢測(cè)GPX1_1引腳輸入的電平,為低電壓時(shí),按鍵按下,為高電平時(shí),按鍵抬起。

配置GPX1_1引腳功能為輸入,設(shè)置內(nèi)部上拉下拉禁止。 GPX1.CON = GPX1.CON &(~(0xf<<4)) ;

GPX1.PUD = GPX1.PUD & ~(0x3 << 2);

按鍵消抖:按鍵按下后由于機(jī)械特性,會(huì)在極短的時(shí)間內(nèi)出現(xiàn)電平忽0忽1,所以我們檢測(cè)到按鍵按下后,需要給一個(gè)延時(shí),然后再判斷按鍵是不是仍然按下。

代碼實(shí)現(xiàn)

int main (void)

{

led_init();

pwm_init();

GPX1.CON = GPX1.CON &(~(0xf<<4))|0x0<<4;

while(1)

{

if(!(GPX1.DAT & (0x1<<1))) // 返回為真,按鍵按下

{

delay_ms(10);

if(!(GPX1.DAT & (0x1<<1))) //二次檢測(cè),去抖

{

GPX2.DAT |= 0x1 << 7; //Turn on LED2

delay_ms(500);

beep_on();

GPX2.DAT &= ~(0x1<<7); //Turn off LED2

delay_ms(500);

while(!(GPX1.DAT & (0x1<<1)));

beep_off();

}

}

}

return 0;

}

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19348瀏覽量

230262 -

ARM

+關(guān)注

關(guān)注

134文章

9107瀏覽量

367990 -

總線

+關(guān)注

關(guān)注

10文章

2891瀏覽量

88174

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

實(shí)際項(xiàng)目開發(fā)中為何選擇ARM? Cortex?-M4 內(nèi)核的HK32MCU?

ARM處理器的異常中斷響應(yīng)過(guò)程

求助,請(qǐng)問(wèn)ESP32S2外設(shè)SPI2中斷及中斷函數(shù)怎么配置?

ARM Cortex-A53嵌入式開發(fā)平臺(tái)Android手冊(cè)

如何測(cè)試STM32中斷搶占,為何優(yōu)先級(jí)高的定時(shí)器2居然一次都搶不到中斷了呢?

STM32中斷分組及外部中斷的配置過(guò)程分享

使用stm8l的外部中斷的pin7的中斷,進(jìn)行中斷處理時(shí)會(huì)立刻造成新的pin7中斷,會(huì)有什么影響嗎?

STM32F103RCT6 uart1中斷方式接收后不返回主程序了,但新的中斷還能進(jìn)來(lái)是怎么回事?

適用于ARM? Cortex?-A8/A9 SOC 和 FPGA 的TPS65218電源管理數(shù)據(jù)表

基于Arm?Cortex-A35的微處理器MA35H0系列規(guī)格書

入門級(jí)64位ARM?CORTEX?-A55 MPU數(shù)據(jù)手冊(cè)

基于ARM Cortex-A9中斷的過(guò)程及詳細(xì)解答

基于ARM Cortex-A9中斷的過(guò)程及詳細(xì)解答

評(píng)論