Q1:HTOL算FIT的時候 老化電壓有很多組 那么計算電壓加速系數的時候,每組電壓都需要算嗎?還是怎么樣的?Answer:以core電壓為準,1.1V按照1.21V做也是在安全范圍內,沒有加壓。

Q2:Die表面鈍化層的具體作用有哪些?及不同種類芯片的鈍化層工藝是否存在差異?Answer:鈍化層一般是氮化硅,有些用氮氧化硅,有些在氮化硅上面再長一層PI Polyimide。

Q3:鈍化層氮化硅,和二氧化硅,厚度多少A?Answer: 3000+6000A。具體看工藝,不過差不多就是這個數據。可以直接問foundry 或者去查interconnect model document, 或者查XRC文件,都會有passivation厚度信息。

Q4:Sensor 和memory 之類的芯片做ATE測試時有必要做WLBI(提高溫度和電壓)測試,來對處于早期失效邊緣的芯片進行篩選和分類嗎?

Answer: WLBI 是指wafer level BI, NAND 根據產品等級, 高DPPM等級的要做BI, 50cycle full array 讀寫, week point stress 等。可以wafer level 也可以封裝后做。電壓corner 一樣都會做的。起碼worst corner 測試。還是看產品DPPM需求。高DPPM等級大概為每百萬顆芯片的缺陷數,還是1顆芯片每百萬像素的缺陷數呢?兩者都可以算,看產品卡什么樣spec,如果一個像素fail就認為這顆料fail,還是允許一些fail bit, 對于NAND 有redundancy Column,及CRC糾錯,一般客戶按芯片DPPM要求。

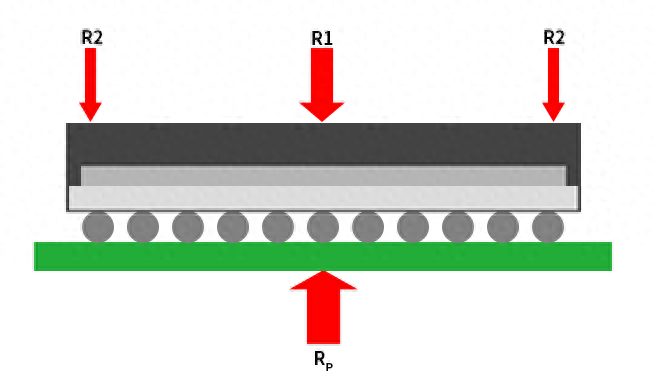

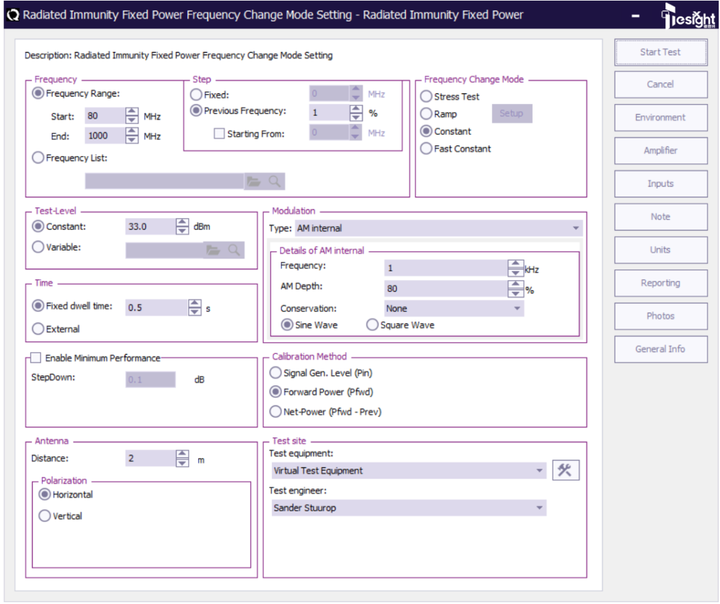

Q5:關于CSP封裝在FT測試中對芯片溫度校準的一些方法嗎?目的是需要通過測試當前芯片溫度從而對芯片內部T-sensor進行校準。

Answer: 可以的,chuck溫度就是設定溫度。一般TS測試用盡量低的功耗模式,最好只有TS在工作。 開放環境芯片TS要求0.5℃精度較難,用腔體結構的有可能。1%的精度還是可以達到的。 要準的話你可能要把斜率也要校準出來,單點還不行。一般應用時, 計算出來的溫度 = 25度 + 斜率 * (readout_code - TS_code@25c)。斜率和ts_code@25c 都是校準出來的。如果要求不高,斜率不校準,用個常數。

責任編輯:xj

原文標題:季豐電子IC運營工程技術知乎 – W51

文章出處:【微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

455文章

50771瀏覽量

423400 -

IC

+關注

關注

36文章

5947瀏覽量

175549 -

CSP

+關注

關注

0文章

124瀏覽量

28087

原文標題:季豐電子IC運營工程技術知乎 – W51

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

絕緣電阻測試儀的校準方法 絕緣電阻測試儀的工作原理

電子電器氣密性檢測儀使用方法:操作中的常見錯誤與糾正

CP測試與FT測試有什么區別

瑞沃微:一文詳解CSP(Chip Scale Package)芯片級封裝工藝

FPGA電路設計的一些技巧

咨詢一些關于LED燈具的問題

使用AD8495芯片+K型熱電偶搭建溫度采樣電路時遇到一些問題求解

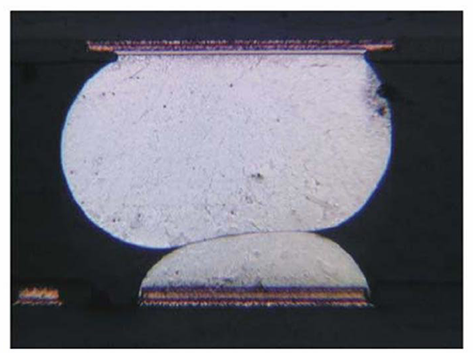

淺談BGA、CSP封裝中的球窩缺陷

關于CSP封裝在FT測試中對芯片溫度校準的一些方法

關于CSP封裝在FT測試中對芯片溫度校準的一些方法

評論