“在依然能夠獲得良好 SNR 結果的情況下,最差情況的 ADC 時鐘可怎樣呢?”雖然從來沒有客戶直接向我提及這一問題,但我的確定期地被問到有關采用不適合高分辨率 ADC 的時鐘源之問題。

通常,它需要一個可具有高達 1nsRMS 抖動的函數發生器。常常需要采用一個高質量的 RF 發生器或晶體振蕩器以從 16 或 18 位 ADC 獲得最佳的 SNR 值,即使在相對較低的輸入頻率下也不例外。本文我將使用安裝了 LTC2389-18 2.5Msps 18 位 ADC 和 LTC PScope 軟件的 DC1826A-A 演示板,來說明抖動對于 SNR 性能的影響以及怎樣降低一個噪聲時鐘源的抖動。

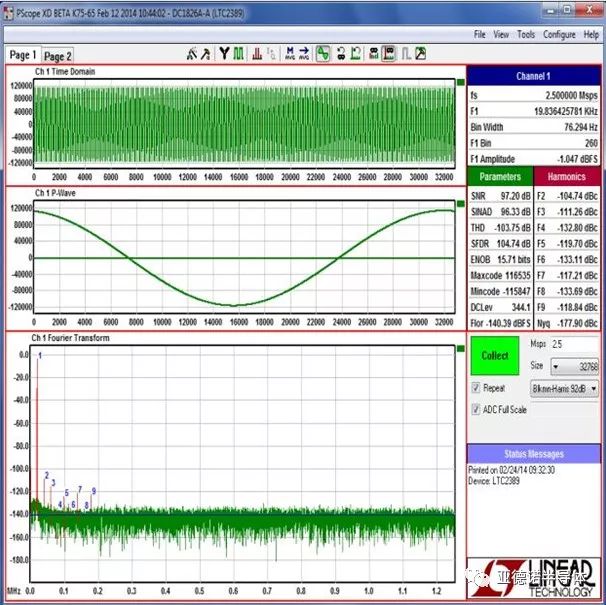

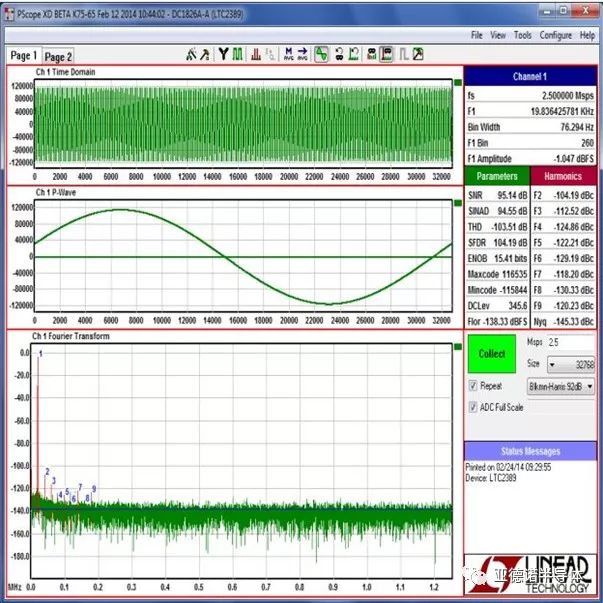

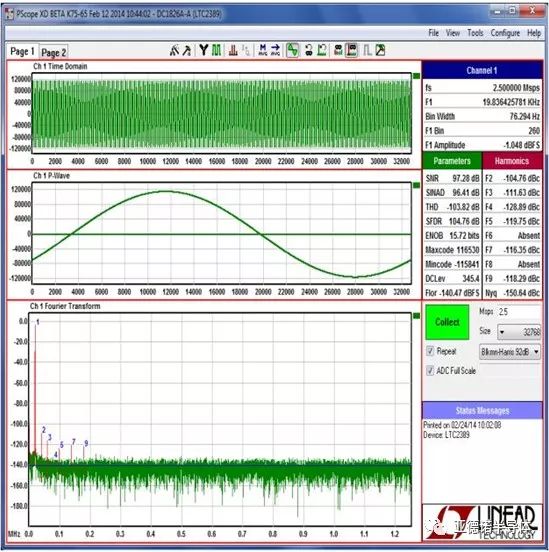

作為基線,DC1826A-A 的時鐘輸入采用一個羅德與施瓦茨 SMB100A RF 發生器來驅動,并由 Stanford Research SR1 提供模擬輸入。結果是圖 1 中的 PScope 數據,其產生一個 98.247dBFS SNR。

圖 1:基線 FFT 顯示:對于 LTC2389-18,SNR 為 98.247dBFS

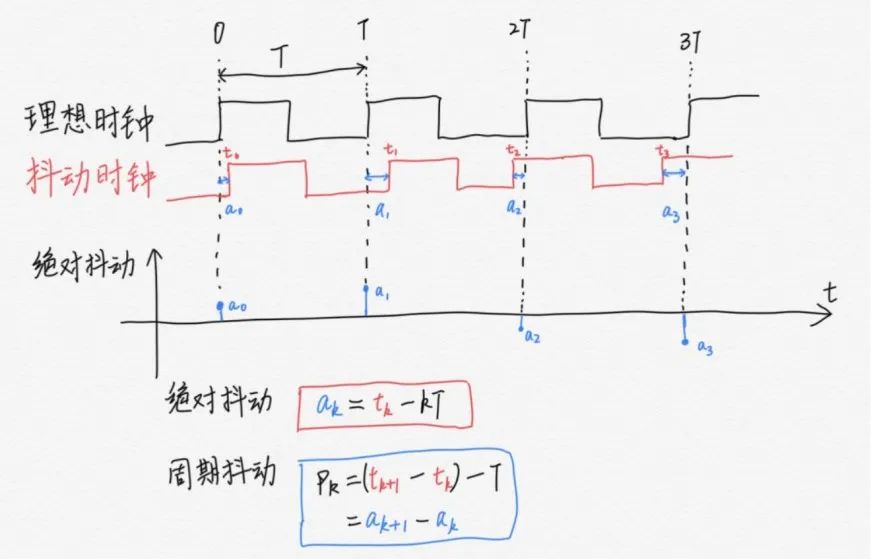

該 SNR 是通過將低于全標度的輸入電平 (-1.047dBFS) 加至已測 SNR 獲得的。ADC 之 CNV 輸入端上的 18.8psRMS 抖動可采用一臺 Agilent Infiniium 9000 系列示波器或同等檔次的示波器進行測量。基于抖動和輸入頻率的 SNR 理論極限值為

20 * log (2 * π * fIN * tjitter)

其中:

tjitter 為 RMS 抖動

fIN 為輸入頻率

代入針對該例的數值得出的SNR 為

20 * log (2 * π * 20kHz * 18.8ps) = 112.5dB

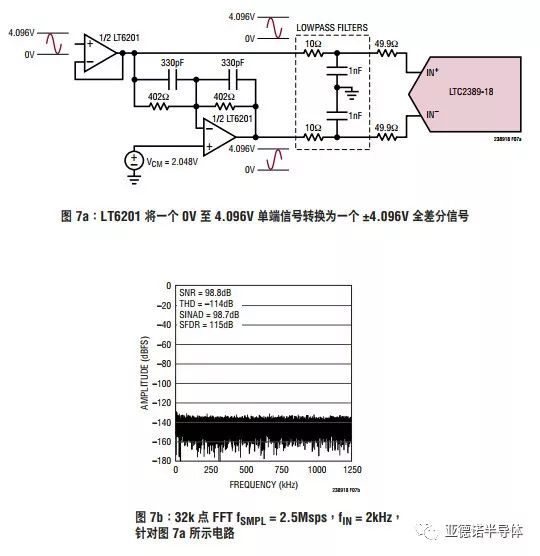

隨后必須將該值與 ADC SNR 進行 RMS 求和運算以產生一個有效 SNR。查看 LTC2389 的產品手冊,在 2kHz 頻率下用于演示板電路 (圖 7a 和 7b) 的典型 SNR 為 98.8dB。

LTC2389 的產品手冊,圖 7a 和 7b

產品手冊中給出的“SNR 與輸入頻率的關系曲線”顯示:在本實驗所采用的 20kHz 輸入頻率下,SNR 產生大約 0.3dB 的滾降,因此 98.8dB 的數字將調節至 98.5dB。98.5dB 與 112.5dB 的 RMS 之和為 98.3dB,這近似于圖 1 中獲得的結果。

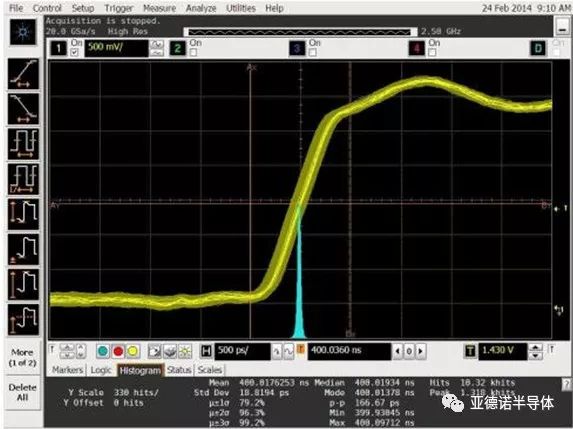

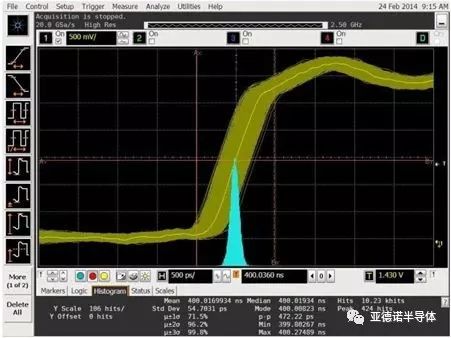

圖 2:DC1826A-A 之 CNV 輸入端上的 RMS 抖動 (采用 SMB100A 時鐘源)

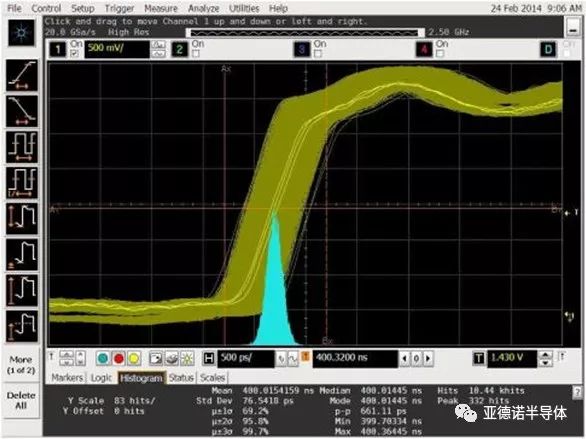

既然已經獲得了一個基線 SNR 測量結果,那么假如使用一個具較高抖動的時鐘源會發生什么呢? 如圖 3 所示,當采用 XXXX-YYYYY (制造商及型號隱去) 發生器時,測得的抖動為 76.5psRMS。在該抖動水平下的SNR 理論極限值為 100.3dB,當其與 LTC2389-18 的 98.5dB 進行 RMS 求和運算時,得出的結果為 96.3dB。

圖 3:噪聲時鐘源在 DC1826A-A 的 CNV 輸入端上產生 76.5psRMS 抖動

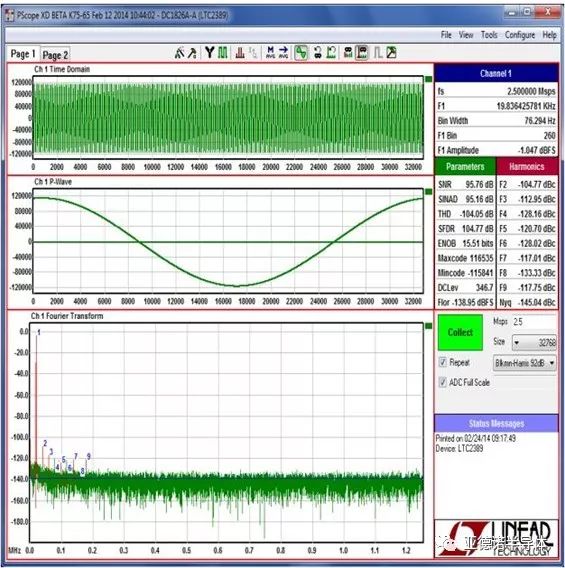

圖 4 的 PScope 截屏中示出的 96.2dBFS 測量 SNR 基本吻合。在相對較低的 20kHz 輸入頻率下,SNR 指標降低了 2dB,且附加的時鐘抖動小于 60ps。在 100kHz 輸入頻率下,SNR 將降至 86dB。

圖 4:采用噪聲時鐘源時 LTC2389-18 的 SNR 指標降低至 96.2dBFS

問

噪聲時鐘源 (例如:剛剛檢查的時鐘源) 上的抖動可以減低嗎?

采用先前的時鐘源,在時鐘的輸出和演示板的時鐘輸入之間插入一個 TTE 低通濾波器。測得的時鐘抖動減小至 54.7psRMS (如圖 5 所示),而最終的 SNR 則改善至 96.8dBFS (如圖 6 給出的 PScope 截屏所示)。

圖 5:噪聲時鐘源的低通濾波降低了 CNV 輸入端上的抖動

圖 6:噪聲時鐘源的低通濾波輕微改善了 SNR

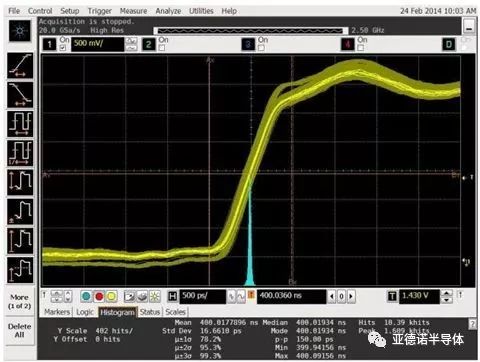

雖然取得了小幅改善,但其仍然不如基線 SNR 測量結果那么好。接著,插入一個 TTE 帶通濾波器以替代低通濾波器。現在,測得的時鐘抖動為 16.7psRMS (如圖 7 所示),而 SNR 的測量結果則顯著地改善至 98.3dBFS (如圖 8 給出的 PScope 截屏所示)。測得的 SNR 此時與基線 SNR 測量值相同。

圖 7:TTE 帶通濾波器極大地降低了抖動

圖 8:TTE 帶通濾波器顯著地改善了 LTC2389-18 的 SNR 指標

現在可以很容易的了解在評估高分辨率 ADC 時采用低抖動時鐘源的必要性。如果您現有可用的時鐘源不具備足夠低的抖動,那么通過利用一個優良的帶通濾波器對時鐘實施濾波仍然能夠獲得上佳的 SNR 測量結果。

責任編輯:lq

-

adc

+關注

關注

99文章

6658瀏覽量

548500 -

發生器

+關注

關注

4文章

1400瀏覽量

62583 -

晶體振蕩器

+關注

關注

9文章

688瀏覽量

30081

原文標題:在評估高分辨率 ADC 時,這個步驟很重要!

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

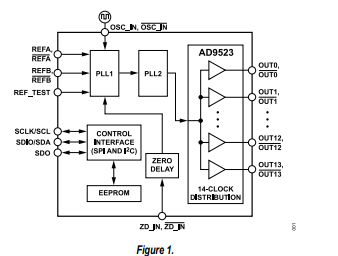

AD9523 14路輸出、低抖動時鐘發生器技術手冊

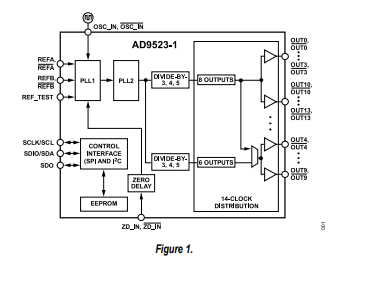

AD9523-1低抖動時鐘發生器,提供14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出技術手冊

評論