看到這個標題, 估計很多人已經笑了. 如果看完這篇文章你還在笑, 那說明你真的很了解.

如果你真的覺得自己了解, 那就不用繼續往下看了.

我記得當年畢業找工作時面試了大大小小10幾家公司, 形形色色的面試題也見了不少, 但關于RLC最最基本的電路相關問題幾乎是必問的, 更有甚者幾乎一半問題都是與此有關. 為什么? 一切都是從基礎開始的. 這是一句我以后會不斷重復的話, 這也是我目前為止對電路的理解. 再復雜再酷炫的電路也離不開這些, 如果真的搞明白了, 對以后理解更高級的東西會有很大的幫助.

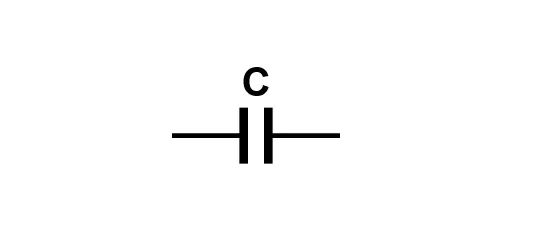

眾所周知, 電容, 兩邊加上電壓, 就能開始充電儲存電荷. 理想狀態下, 就是一個C:

可現實永遠是殘酷的, 你會發現你所做的一切幾乎都是和在這些非理想的問題作斗爭.

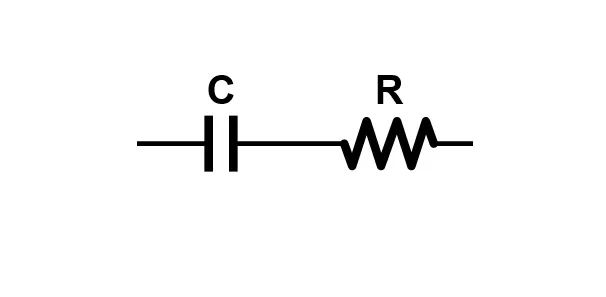

ESR(Equivalent Series Resistance)

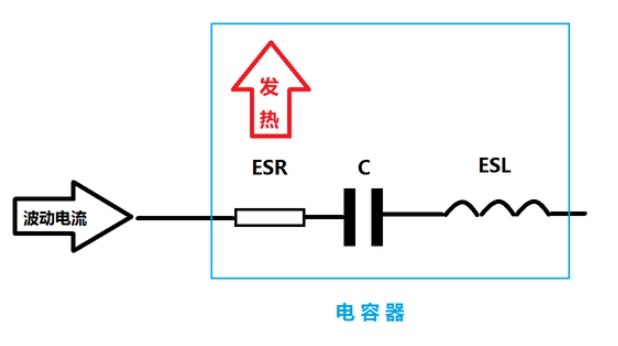

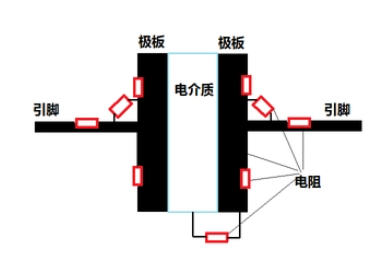

如果你去看電容的datasheet(比如去Murata的關網隨便找一個), 每個非理想電容都會有一個叫ESR的指標. 顧名思義, 電容本身會有一個等效串聯電阻, 那么電容的等效電路就變成了:

這個電阻一般有多大呢? 通常是在100mΩ ~ 1000mΩ不等, 具體數值大小根據電容種類和電容值大小來定, 這里先不細說, 我會在之后比較不同電容的區別時詳細講解.

那么肯定會有人問這么小的串聯電阻, 會有什么大的影響么? 不好意思, 還真會有, 在要求極其苛刻情況下還會把兩個電容并聯以減小ESR. 比如 LDO 的output capacitor, 如果這個ESR過大或者過小, 很有可能會引起LDO的stability問題.

另一方面, 當電容被用做電源的decoupling cap時, 你希望的是這個R越小越好. 當電容被用做的decoupling cap時, 其作用是為了提供高頻的電流供給. 假如你的芯片電源會有一個非常短暫的100mA的peak current, 而且這個電流幾乎是你的decoupling cap來提供的, 如果你的電容ESR有1Ω,想象一下100mA的電流流過這個電阻, 到達另一端的時候, 已然有了100mV的壓降了.

所以一句話: 通常情況下, 你希望這個電阻越小越好. 除了用于例如LDO的輸出電容, ESR的大小會影響到LDO的穩定性, 但這個問題說來話長, 有機會單獨開一篇細講.

說完R, 我們來講講L.

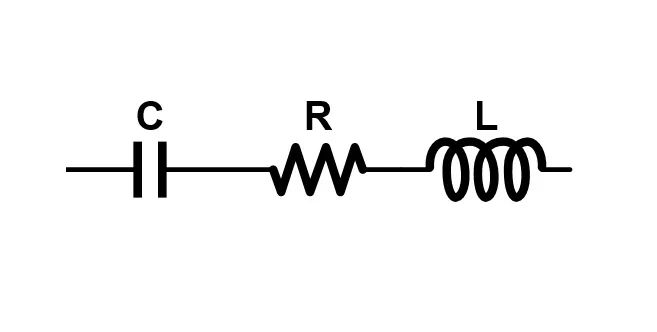

ESL(Equivalent Series Inductance)

很多情況下這是一個往往被人忽略的一個指標, 你經常會看到ESR的spec, 很多電容的datasheet往往都沒有ESL這個spec在里面. 但是隨著信號頻率的越來越高, ESL是完全不能被忽視的. 既然如此, 電容的等效電路又要變成這樣:

ESL主要影響的是電容的高頻特性. 通常這個ESL是很小的, 即便如此, 當信號的頻率高到一定程度, 這個L的阻抗會變得不可忽略, 當頻率繼續升高, Z_{L} 會逐漸的變大, 因此電容就開始逐漸的開始看起來像一個電感. 同樣的情況, decoupling cap其中一個重要的作用是用來提供瞬時的大電流的, 而這里的L會嘗試阻止電流的瞬時變化, 因而如果ESL太大, 會使得decoupling cap的作用大大降低, 尤其是在高頻的情況下.

上圖來自:

通常情況下, 當你打開一個電容的datasheet, 你會找到如上圖所示的一個電容阻抗 v.s. 頻率的一個圖表. 這張圖清楚的表示了ESR和ESL是如何改變理想電容的阻抗v.s. 頻率的曲線的.

責任編輯:lq

-

串聯電阻

+關注

關注

1文章

191瀏覽量

14787 -

電容

+關注

關注

100文章

6038瀏覽量

150274 -

ESR

+關注

關注

4文章

202瀏覽量

31111

原文標題:ESR、ESL,如何影響電容?一文解答!

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何通過等效串聯電阻(ESR)和等效串聯電感(ESL)來優化熱回路布局設計

PCM1704去藕電容器能否以超低ESR電容器來進行替換?

貼片電解電容如何選擇合適的?

濾波電容的選擇原則

關于LDL1117S33R輸出電容ESR選擇的疑問求解決

ESR對電容和電路的影響

ESR、ESL如何影響電容?

ESR、ESL如何影響電容?

評論