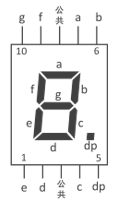

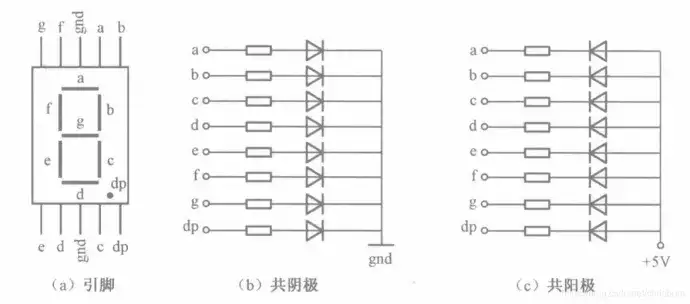

小腳丫板載的數(shù)碼管是7段數(shù)碼管(如果包括右下的小點(diǎn)可以認(rèn)為是8段),它分別由a、b、c、d、e、f、g位段和表示小數(shù)點(diǎn)的dp位段組成,見(jiàn)圖1。

圖1 7段數(shù)碼管

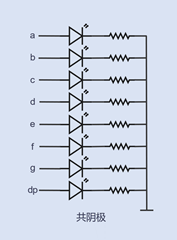

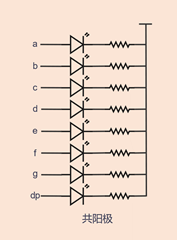

圖1 7段數(shù)碼管數(shù)碼管的各個(gè)段位是由LED燈組成的,控制每個(gè)LED的點(diǎn)亮或熄滅實(shí)現(xiàn)數(shù)字顯示。通常數(shù)碼管分為共陽(yáng)極數(shù)碼管和共陰極數(shù)碼管,結(jié)構(gòu)如圖所示。共陰8段數(shù)碼管的信號(hào)端低電平有效,而共陽(yáng)端接高電平有效。比如,使共陽(yáng)端數(shù)碼管的a段發(fā)光,則在a段信號(hào)端加上低電平即可。共陰極的數(shù)碼管則相反。

?

?

?

?小腳丫的板載數(shù)碼管為7段共陰極數(shù)碼管,可以顯示數(shù)字0-9以及字母A-F共計(jì)16種選擇。因此,如果我們需要數(shù)碼管能顯示所有的16種選擇,需要至少4位輸入碼(24=16)。表1列出了各個(gè)數(shù)碼管字符所對(duì)應(yīng)的LED燈段位。

表1各數(shù)碼管字符所對(duì)應(yīng)的LED燈段位

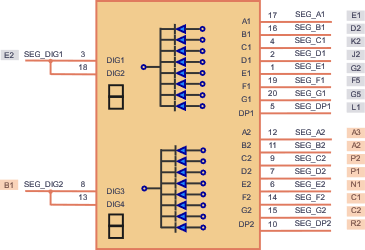

圖2標(biāo)注了小腳丫板載的兩個(gè)數(shù)碼管的各LED段位以及小腳丫上所對(duì)應(yīng)的引腳。其中SEG_DIP為公共端,因此在共陰極數(shù)碼管的設(shè)計(jì)中需要接低電平。可以看出,每一個(gè)數(shù)碼管都含有9個(gè)引腳,因此每一個(gè)字符的顯示都需要由一個(gè)9位的輸出信號(hào)來(lái)實(shí)現(xiàn)。

接下來(lái)我們通過(guò)Verilog實(shí)現(xiàn)對(duì)數(shù)碼管的控制。其中,我們將模塊的輸出定義為兩個(gè)7段數(shù)碼管,每個(gè)數(shù)碼管有9個(gè)引腳,分別由9位信號(hào)控制。輸入端由4路信號(hào)控制,可以分別對(duì)應(yīng)0-F等十六個(gè)字符選擇。

module segment(input wire[3:0] seg_data_1, //四位輸入數(shù)據(jù)信號(hào),可通過(guò)4個(gè)撥碼開(kāi)關(guān)控制input wire[3:0] seg_data_2, //四位輸入數(shù)據(jù)信號(hào),可通過(guò)4個(gè)按鍵開(kāi)關(guān)控制output wire[8:0] segment_led_1, //數(shù)碼管1,MSB~LSB =SEG,DP,G,F,E,D,C,B,Aoutput wire[8:0] segment_led_2 //數(shù)碼管2,MSB~LSB =SEG,DP,G,F,E,D,C,B,A);reg[8:0] seg [15:0]; //存儲(chǔ)7段數(shù)碼管譯碼數(shù)據(jù)initialbeginseg[0]=9'h3f; // 0seg[1]=9'h06; // 1seg[2]=9'h5b; // 2seg[3]=9'h4f; // 3seg[4]=9'h66; // 4seg[5]=9'h6d; // 5seg[6]=9'h7d; // 6seg[7]=9'h07; // 7seg[8]=9'h7f; // 8seg[9]=9'h6f; // 9seg[10]=9'h77; // Aseg[11]=9'h7C; // bseg[12]=9'h39; // Cseg[13]=9'h5e; // dseg[14]=9'h79; // Eseg[15]=9'h71; // Fendassign segment_led_1 = seg[seg_data_1]; // 將對(duì)應(yīng)字符導(dǎo)入數(shù)碼管1并顯示assign segment_led_2 = seg[seg_data_2]; // 將對(duì)應(yīng)字符導(dǎo)入數(shù)碼管2并顯示endmodule

上述代碼是定義7段共陰極數(shù)碼管的通用模塊,可以保存起來(lái)作為一個(gè)獨(dú)立模塊。這樣,在以后遇到需要用數(shù)碼管顯示的實(shí)驗(yàn)時(shí)我們可以直接調(diào)用(之后我們還會(huì)講解如何調(diào)用子模塊),而不用再重新寫一遍代碼。

接下來(lái)是提問(wèn)環(huán)節(jié):

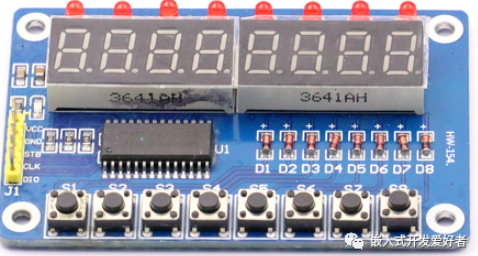

當(dāng)我們指定用撥碼開(kāi)關(guān)SW1-SW4來(lái)控制左邊數(shù)碼管,按鍵開(kāi)關(guān)K1-K4來(lái)控制右側(cè)數(shù)碼管,此時(shí)如果開(kāi)關(guān)的狀態(tài)分別如下圖所示,數(shù)碼管應(yīng)該顯示什么字符?

而為了幫助更多老師快速上手FPGA的使用和教學(xué),在即將到來(lái)的寒假,我們針對(duì)高校從事教學(xué)/實(shí)驗(yàn)室一線工作的教師,推出一個(gè)為期5天(2021年1月25日-1月29日)的FPGA設(shè)計(jì)及應(yīng)用快速培訓(xùn),通過(guò)實(shí)用性非常強(qiáng)的典型案例動(dòng)手實(shí)踐,幫助大家快速、有效地上手FPGA,并能夠在未來(lái)的教學(xué)、實(shí)踐、電賽中大顯身手,硬禾實(shí)戰(zhàn)營(yíng)也將成為參加培訓(xùn)的老師們長(zhǎng)期的教學(xué)后援。

責(zé)任編輯:xj

原文標(biāo)題:基于FPGA的數(shù)字電路實(shí)驗(yàn)3:點(diǎn)亮數(shù)碼管

文章出處:【微信公眾號(hào):FPGA入門到精通】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603993 -

數(shù)碼管

+關(guān)注

關(guān)注

32文章

1882瀏覽量

91193 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1608瀏覽量

80670

原文標(biāo)題:基于FPGA的數(shù)字電路實(shí)驗(yàn)3:點(diǎn)亮數(shù)碼管

文章出處:【微信號(hào):xiaojiaoyafpga,微信公眾號(hào):電子森林】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)碼管的使用方法和接線步驟

簡(jiǎn)述led數(shù)碼管的類型和顯示原理

led數(shù)碼管顯示器分哪兩種結(jié)構(gòu)類型

數(shù)碼管顯示屏的靜態(tài)顯示編程是什么

數(shù)碼管顯示屏的作用和功能是什么

數(shù)碼管在仿真軟件中叫什么

8位數(shù)碼管怎么不顯示數(shù)字

怎樣區(qū)分數(shù)碼管是共陰還是共陽(yáng)

數(shù)碼管驅(qū)動(dòng)芯片引腳功能

CW32數(shù)字電壓電流表軟件教程-實(shí)驗(yàn)三:數(shù)碼管顯示數(shù)字

CW32數(shù)字電壓電流表軟件教程(三):數(shù)碼管顯示數(shù)字

硬件模塊---數(shù)碼管基本原理與實(shí)現(xiàn)方法

通過(guò)小腳丫板載的兩個(gè)數(shù)碼管來(lái)顯示字符

通過(guò)小腳丫板載的兩個(gè)數(shù)碼管來(lái)顯示字符

評(píng)論