對(duì)于研發(fā)人員而言,大家總是在追求低功耗設(shè)計(jì)。采用低功耗設(shè)計(jì),無(wú)疑是能夠帶來(lái)諸多好處。為幫助大家了解如何降低功耗,本文中,小編將對(duì)降低 FPGA 功耗的設(shè)計(jì)技巧加以闡述。

新一代 FPGA 的速度變得越來(lái)越快,密度變得越來(lái)越高,邏輯資源也越來(lái)越多。那么如何才能確保功耗不隨這些一起增加呢?很多設(shè)計(jì)抉擇可以影響系統(tǒng)的功耗,這些抉擇包括從顯見的器件選擇到細(xì)小的基于使用頻率的狀態(tài)機(jī)值的選擇等。

為了更好地理解本文將要討論的設(shè)計(jì)技巧為什么能夠節(jié)省功耗,我們先對(duì)功耗做一個(gè)簡(jiǎn)單介紹。

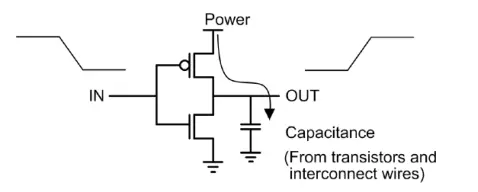

功耗包含兩個(gè)因素:動(dòng)態(tài)功耗和靜態(tài)功耗。動(dòng)態(tài)功耗是指對(duì)器件內(nèi)的容性負(fù)載充放電所需的功耗。它很大程度上取決于頻率、電壓和負(fù)載。這三個(gè)變量中的每個(gè)變量均在您的某種控制之下。

動(dòng)態(tài)功耗 = 電容×電壓 2×頻率

靜態(tài)功耗是指由器件中所有晶體管的泄漏電流(源極到漏極以及柵極泄漏,常常集中為靜止電流)引起的功耗,以及任何其他恒定功耗需求之和。泄漏電流很大程度上取決于結(jié)溫和晶體管尺寸。

恒定功耗需求包括因終接(如上拉電阻)而造成的電流泄漏。沒有多少措施可以采用來(lái)影響泄漏,但恒定功耗可以得到控制。

盡早考慮功耗

您在設(shè)計(jì)的早期階段做出的功耗決定影響最大。決定采用什么元件對(duì)功耗具有重大意義,而在時(shí)鐘上插入一個(gè) BUFGMUX 則影響甚微。對(duì)功耗的考慮越早越好。

恰當(dāng)?shù)脑?/p>

并不是所有元件都具有相同的靜止功耗。根據(jù)普遍規(guī)則,器件工藝技術(shù)尺寸越小,泄漏功耗越大。但并不是所有工藝技術(shù)都一樣。例如,對(duì)于 90 nm 技術(shù)來(lái)說(shuō),Virtex-4 器件與其他 90 nm FPGA 技術(shù)之間在靜止功耗方面存在顯著差異,

然而,在靜止功耗隨工藝技術(shù)縮小而增加的同時(shí),動(dòng)態(tài)功耗卻隨之減小,這是由于較小的工藝有著更低的電壓和電容。考慮好哪種功耗對(duì)你的設(shè)計(jì)影響更大——待機(jī)(靜止)功耗還是動(dòng)態(tài)功耗。

除通用切片邏輯單元外,所有 Xilinx 器件都具有專門邏輯。其形式有塊 RAM、18×18 乘法器、DSP48 塊、SRL16s,以及其他邏輯。這不僅在于專門邏輯具有更高的性能,還在于它們具有更低的密度,因而對(duì)于相同的操作可以消耗較少的功率。評(píng)估您的器件選項(xiàng)時(shí),請(qǐng)考慮專門邏輯的類型和數(shù)量。

選擇適當(dāng)?shù)?I/O 標(biāo)準(zhǔn)也可以節(jié)省功耗。這些都是簡(jiǎn)單的決定,如選擇最低的驅(qū)動(dòng)強(qiáng)度或較低的電壓標(biāo)準(zhǔn)。當(dāng)系統(tǒng)速度要求使用高功率 I/O 標(biāo)準(zhǔn)時(shí),計(jì)劃一個(gè)缺省狀態(tài)以降低功耗。有的 I/O 標(biāo)準(zhǔn)(如 GTL/+)需要使用一個(gè)上拉電阻才能正常工作。因此如果該 I/O 的缺省狀態(tài)為高電平而不是低電平,就可以節(jié)省通過該終接電阻的直流功耗。對(duì)于 GTL+,將 50Ω終接電阻的適當(dāng)缺省狀態(tài)設(shè)置為 1.5V,可使每個(gè) I/O 節(jié)省功耗 30 mA。

數(shù)據(jù)使能

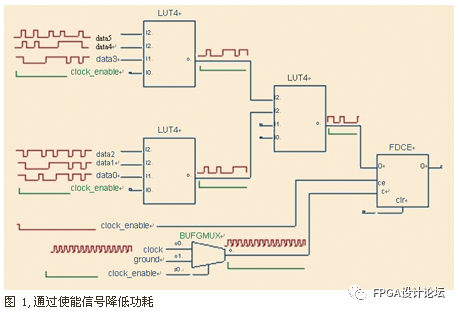

當(dāng)總線上的數(shù)據(jù)與寄存器相關(guān)時(shí),經(jīng)常使用片選或時(shí)鐘使能邏輯來(lái)控制寄存器的使能。進(jìn)一步來(lái)說(shuō),盡早對(duì)該邏輯進(jìn)行“數(shù)據(jù)使能”,以阻止數(shù)據(jù)總線與時(shí)鐘使能寄存器組合邏輯之間不必要的轉(zhuǎn)換,如圖 1 所示。紅色波形表示原設(shè)計(jì);綠色波形表示修改后的設(shè)計(jì)。

另一種選擇是在電路板上而不是在芯片上進(jìn)行這種“數(shù)據(jù)使能”。以盡可能減小處理器時(shí)鐘周期。此概念是使用 CPLD 從處理器卸載簡(jiǎn)單任務(wù),以便使其更長(zhǎng)時(shí)間地處于待機(jī)模式。

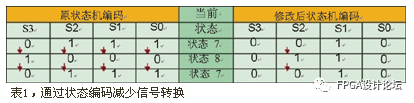

讓我們來(lái)看一個(gè)在狀態(tài) 7 和狀態(tài) 8 之間頻繁進(jìn)行狀態(tài)轉(zhuǎn)換的狀態(tài)機(jī)。如果您為該狀態(tài)機(jī)選擇二進(jìn)制編碼,將意味著對(duì)于每次狀態(tài) 7 和狀態(tài) 8 之間的狀態(tài)轉(zhuǎn)換,將有四位需要改變狀態(tài),如表 1 所示。如果狀態(tài)機(jī)采用格雷碼而不是二進(jìn)制碼來(lái)設(shè)計(jì),則這兩個(gè)狀態(tài)之間的轉(zhuǎn)移所需的邏輯轉(zhuǎn)換的數(shù)量將降至僅一位。另外,如果將狀態(tài) 7 和 8 分別編碼為 0010 和 0011,也可以達(dá)到同樣的效果。

時(shí)鐘管理

在一個(gè)設(shè)計(jì)的所有吸收功耗的信號(hào)當(dāng)中,時(shí)鐘是罪魁禍?zhǔn)住km然一個(gè)時(shí)鐘可能運(yùn)行在 100 MHz,但從該時(shí)鐘派生出的信號(hào)卻通常運(yùn)行在主時(shí)鐘頻率的較小分量(通常為 12% ~ 15%)。此外,時(shí)鐘的扇出一般也比較高——這兩個(gè)因素顯示,為了降低功耗,應(yīng)當(dāng)認(rèn)真研究時(shí)鐘。

如果設(shè)計(jì)的某個(gè)部分可以處于非活動(dòng)狀態(tài),則可以考慮使用一個(gè) BUFG-MUX 來(lái)禁止時(shí)鐘樹翻轉(zhuǎn),而不是使用時(shí)鐘使能。時(shí)鐘使能將阻止寄存器進(jìn)行不必要的翻轉(zhuǎn),但時(shí)鐘樹仍然會(huì)翻轉(zhuǎn),消耗功率。不過采用時(shí)鐘使能總比什么措施也沒有強(qiáng)。

隔離時(shí)鐘以使用最少數(shù)量的信號(hào)區(qū)。不使用的時(shí)鐘樹信號(hào)區(qū)不會(huì)翻轉(zhuǎn),從而降低該時(shí)鐘網(wǎng)絡(luò)的負(fù)載。仔細(xì)布局可以在不影響實(shí)際設(shè)計(jì)的情況下達(dá)到此目標(biāo)。

對(duì) FPGA 顯然也可以使用同一概念。雖然 FPGA 不一定擁有待機(jī)模式,但使用一個(gè) CPLD 中途欄截總線數(shù)據(jù)并有選擇地將數(shù)據(jù)饋送到 FPGA 也可以省去不必要的輸入轉(zhuǎn)換。

CoolRunner-II CPLD 包含一種稱為“數(shù)據(jù)門控”的功能,可以禁止引腳上的邏輯轉(zhuǎn)換到達(dá) CPLD 的內(nèi)部邏輯。該數(shù)據(jù)門控使能可通過片上邏輯或引腳來(lái)控制。

狀態(tài)機(jī)設(shè)計(jì)

根據(jù)預(yù)測(cè)的下一狀態(tài)條件列舉狀態(tài)機(jī),并選擇常態(tài)之間轉(zhuǎn)換位較少的狀態(tài)值。這樣,您就能夠盡可能減少狀態(tài)機(jī)網(wǎng)絡(luò)的轉(zhuǎn)換量(頻率)。確定常態(tài)轉(zhuǎn)換和選擇適當(dāng)?shù)臓顟B(tài)值,是降低功耗且對(duì)設(shè)計(jì)影響較小的一種簡(jiǎn)單方法。編碼形式越簡(jiǎn)單(一位有效編碼或格雷碼),使用的解碼邏輯也會(huì)越少。

功耗估算工具

賽靈思提供了兩種形式的功耗估算工具:一種叫做 Web Power Tools 的設(shè)計(jì)前工具和一種叫做 Xpower 的設(shè)計(jì)后工具。利用它,您可以僅憑設(shè)計(jì)利用率估計(jì)就能獲得功耗評(píng)估,而無(wú)需實(shí)際設(shè)計(jì)文件。

XPower 是一種設(shè)計(jì)后工具,用于分析實(shí)際器件利用率,并結(jié)合實(shí)際的適配后 (post-fit) 仿真數(shù)據(jù)(VCD 文件格式),給出實(shí)際功耗數(shù)據(jù)。利用 Xpower,您可以在完全不接觸芯片的情況下分析設(shè)計(jì)改變對(duì)總功耗的影響。

基于 Web 的功耗工具

基于 Web 的功耗估計(jì)是在設(shè)計(jì)流程的早期獲得器件功耗情況的最快捷和最方便的方法。這些工具每個(gè)季度都會(huì)發(fā)布新版本,因此信息總是最新的,且不需要安裝或下載,只需要擁有互聯(lián)網(wǎng)連接和 Web 瀏覽器即可。您可以指定設(shè)計(jì)參數(shù)并保存和加載設(shè)計(jì)設(shè)置,免去了通過交互使用重新輸入設(shè)計(jì)參數(shù)的麻煩。只要有對(duì)設(shè)計(jì)行為的估計(jì)并選定目標(biāo)器件即可開始。

Xpower:集成的設(shè)計(jì)專用功耗分析

Xpower 是所有 Xilinx ISE 設(shè)計(jì)工具的一個(gè)免費(fèi)組件,您可以利用它對(duì)您的基于設(shè)計(jì)的功耗需求進(jìn)行詳細(xì)得多的估計(jì)。XPower 是在映射或布局和布線后設(shè)計(jì)的基礎(chǔ)上對(duì)器件功耗進(jìn)行估計(jì)的。

對(duì)于成熟的投產(chǎn)的 FPGA 和 CPLD,XPower 計(jì)算出的功耗估計(jì)的平均設(shè)計(jì)批量誤差 (suite error) 小于 10%。它將把器件數(shù)據(jù)與您的設(shè)計(jì)文件結(jié)合起來(lái)綜合考慮,并按照您的專門設(shè)計(jì)信息給出估計(jì)器件功耗的高精度報(bào)告。

XPower 直接集成在 ISE 軟件中,可提供層次化的詳細(xì)的功耗顯示、詳細(xì)的總結(jié)報(bào)告和功耗向?qū)В词故切掠脩粢部奢p易上手。XPower 可接受仿真的設(shè)計(jì)活動(dòng)數(shù)據(jù),并可以 GUI 模式和批處理模式運(yùn)行。

XPower 將考慮設(shè)計(jì)中的每個(gè)網(wǎng)絡(luò)和邏輯元素。ISE 設(shè)計(jì)文件提供準(zhǔn)確的資源使用情況;XPower 交叉參考布線信息以及特性化電容數(shù)據(jù)。于是物理資源針對(duì)電容進(jìn)行特性化。設(shè)計(jì)特性化將對(duì)新器件持續(xù)進(jìn)行,以給出最精確的結(jié)果。Xpower 使用了網(wǎng)絡(luò)翻轉(zhuǎn)速率和輸出負(fù)載。然后 XPower 計(jì)算功耗和結(jié)溫,還可以顯示單個(gè)網(wǎng)絡(luò)的功耗數(shù)據(jù)。

責(zé)任編輯:lq

-

FPGA

+關(guān)注

關(guān)注

1646文章

22063瀏覽量

619365 -

低功耗

+關(guān)注

關(guān)注

12文章

2822瀏覽量

105014 -

變量

+關(guān)注

關(guān)注

0文章

614瀏覽量

28992

原文標(biāo)題:低功耗成為標(biāo)配,三分鐘了解FPGA低功耗設(shè)計(jì)技巧

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

CYBT-213043-MESH如何降低低功耗節(jié)點(diǎn)的電流消耗?

新一代nRF54L系列:進(jìn)一步降低功耗

低功耗、低功耗前端模塊,適用于藍(lán)牙?范圍擴(kuò)展應(yīng)用 skyworksinc

低功耗、低功耗前端模塊,適用于藍(lán)牙?信號(hào)范圍擴(kuò)展應(yīng)用 skyworksinc

藍(lán)牙低功耗模塊的原理和應(yīng)用介紹

關(guān)于低功耗藍(lán)牙連接功耗的評(píng)估

低功耗處理器的優(yōu)勢(shì)分析

AN-1111: 使用ADuCM360/ADuCM361時(shí)的降低功耗選項(xiàng)

如何降低AFE4400的功耗?

如何降低AD1247的功耗?

物聯(lián)網(wǎng)系統(tǒng)中TCP低功耗產(chǎn)品長(zhǎng)連接狀態(tài)下降低功耗功能的實(shí)現(xiàn)方案

柵極驅(qū)動(dòng)芯片選型低功耗原因

為低功耗FPGA、處理器和ASIC實(shí)施啟用LVDS鏈路

評(píng)論