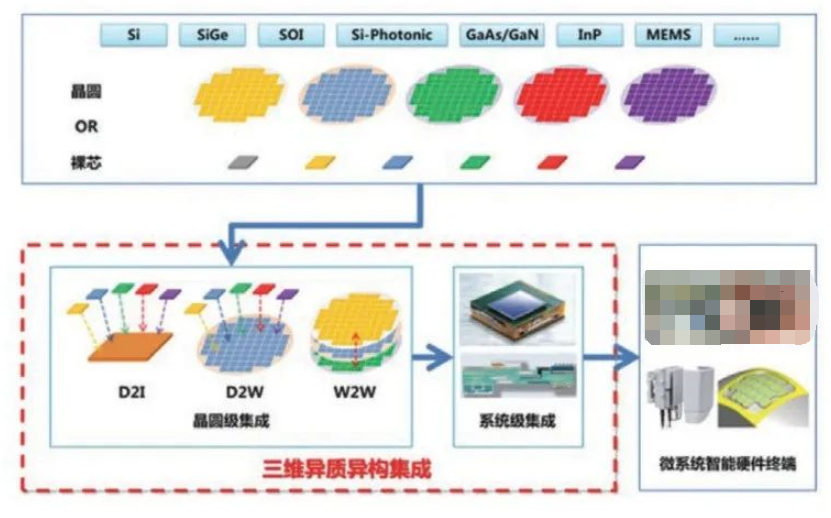

封裝技術(shù)已從單芯片封裝開始,發(fā)展到多芯片封裝/模塊、三維封裝等階段,目前正在經(jīng)歷系統(tǒng)級(jí)封裝與三維集成的發(fā)展階段。

隨著摩爾定律放緩,系統(tǒng)級(jí)封裝和三維集成通過功能集成的手段擺脫尺寸依賴的傳統(tǒng)發(fā)展路線,成為拓展摩爾定律的關(guān)鍵,是集成電路技術(shù)發(fā)展的重要?jiǎng)?chuàng)新方向。

對(duì)于三維集成,首先其系統(tǒng)需求要滿足高性能、高可靠性、可升級(jí)應(yīng)用的產(chǎn)品,在未來3-5年出現(xiàn)小批量、多品種的需求以及可控的產(chǎn)業(yè)鏈,從而實(shí)現(xiàn)系統(tǒng)性能目標(biāo),它會(huì)涉及到性能指標(biāo),包括數(shù)據(jù)傳輸速率,時(shí)延、插入損耗、功率、標(biāo)準(zhǔn)接口、電性能、可靠性、可用性等。

目前,先進(jìn)封裝與系統(tǒng)集成的核心技術(shù)還面臨著三大挑戰(zhàn)。其一是功能集成提出面向復(fù)雜系統(tǒng)級(jí)封裝的設(shè)計(jì)與制造;其二是互連密度提升對(duì)三維集成和高密度封裝基板提出新的要求;其三是前沿基礎(chǔ)問題的研究,包括新型層間互連和新型熱管理方法等。

在整個(gè)產(chǎn)業(yè)中,臺(tái)積電(TSMC)非常重視三維集成技術(shù),將CoWoS、InFO、SolC整合為3D Fabric的工藝平臺(tái)。蔡堅(jiān)表示,“從功能提升、成本降低以及工藝兼容來看,臺(tái)積電之所以有這么多三維集成的工藝出現(xiàn),在于其對(duì)三維集成進(jìn)行了特別深刻的研究。”

早在10年之前,行業(yè)就出現(xiàn)基于硅通孔(TSV)的三維集成。2011年Xilinx采用2.5D Interposer實(shí)現(xiàn)FPGA。隨后Samsung 、AMD、 Intel、AMD等公司也加速布局。不過,TSV并非三維集成/異質(zhì)集成的唯一選擇。

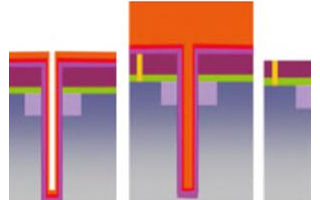

蔡堅(jiān)認(rèn)為,“高深寬比硅通孔(TSV)技術(shù)和層間互連方法是三維集成中的關(guān)鍵技術(shù)。采用化學(xué)鍍及ALD等方法,實(shí)現(xiàn)高深寬比TSV中的薄膜均勻沉積。并通過脈沖電鍍、優(yōu)化添加劑體系等方法,實(shí)現(xiàn)TSV孔沉積速率翻轉(zhuǎn),保證電鍍中的深孔填充。”

在層間互連方法方面,由于高密度集成導(dǎo)致層間互連節(jié)距減少。蔡堅(jiān)教授團(tuán)隊(duì)采取窄節(jié)距Cu-Sn-Cu擴(kuò)散鍵合,對(duì)打散機(jī)理與微觀組織演化的研究,提出了形成穩(wěn)定界面設(shè)計(jì)規(guī)則,可實(shí)現(xiàn)多層/多次鍵合。

關(guān)于技術(shù)成果轉(zhuǎn)化,蔡堅(jiān)表示,我的愿景是成為國(guó)內(nèi)頂尖、國(guó)際一流的封裝設(shè)計(jì)與系統(tǒng)級(jí)封裝一站式服務(wù)技術(shù)平臺(tái),具有完善的封裝設(shè)計(jì)與制作基本能力、集成產(chǎn)品的分析能力,支撐產(chǎn)業(yè)鏈中不同類型企業(yè)的需求。

為了更好的轉(zhuǎn)化技術(shù)成果,蔡堅(jiān)教授團(tuán)隊(duì)于2020年9月設(shè)立公司“清芯集成”,并于10月開始實(shí)際運(yùn)營(yíng),其布局領(lǐng)域包括高復(fù)雜度處理器、光電封裝、量子封裝、探測(cè)器封裝等;2021年計(jì)劃建成基本架構(gòu)、完成超凈間裝修、實(shí)現(xiàn)基本封裝工藝能力、開展小批量業(yè)務(wù)。

責(zé)任編輯:tzh

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423155 -

封裝

+關(guān)注

關(guān)注

126文章

7873瀏覽量

142894

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

系統(tǒng)級(jí)封裝(SiP)技術(shù)介紹

三維堆疊封裝新突破:混合鍵合技術(shù)揭秘!

硅通孔三維互連與集成技術(shù)

三維打印技術(shù)原理

泰來三維 工廠三維掃描建模技術(shù)服務(wù)

三維可視化運(yùn)維技術(shù)的主要特點(diǎn)和應(yīng)用

三維可視化系統(tǒng)平臺(tái)介紹及優(yōu)勢(shì)

江陰兩大產(chǎn)業(yè)項(xiàng)目開工,引領(lǐng)全球封裝技術(shù)創(chuàng)新

系統(tǒng)級(jí)封裝技術(shù)綜述

封裝技術(shù)新篇章:焊線、晶圓級(jí)、系統(tǒng)級(jí),你了解多少?

泰來三維|文物三維掃描,文物三維模型怎樣制作

半導(dǎo)體先進(jìn)封裝技術(shù)

傳統(tǒng)封裝和先進(jìn)封裝的區(qū)別

淺談三維單片異構(gòu)集成的發(fā)展歷程

蔡堅(jiān):封裝技術(shù)正在經(jīng)歷系統(tǒng)級(jí)封裝與三維集成的發(fā)展階段

蔡堅(jiān):封裝技術(shù)正在經(jīng)歷系統(tǒng)級(jí)封裝與三維集成的發(fā)展階段

評(píng)論