FPGA 是一堆晶體管,你可以把它們連接(wire up)起來做出任何你想要的電路。它就像一個納米級面包板。使用 FPGA 就像芯片流片,但是你只需要買這一張芯片就可以搭建不一樣的設計,作為交換,你需要付出一些效率上的代價。

從字面上講這種說法并不對,因為你并不需要重連(rewire)FPGA,它實際上是一個通過路由網絡(routing network)連接的查找表 2D 網格,以及一些算術單元和內存。FPGA 可以模擬任意電路,但它們實際上只是在模仿,就像軟件電路仿真器模擬電路一樣。這個答案不恰當的地方在于,它過分簡化了人們實際使用 FPGA 的方式。接下來的兩個定義能更好地描述 FPGA。

電路模擬是 FPGA 的經典主流用例,這也是 FPGA 最早出現的原因。FPGA 的關鍵在于硬件設計是用 HDL 形式編碼的,而且買一些便宜的硬件就可以得到和 ASIC 相同的效果。當然,你不可能在 FPGA 和真正的芯片上使用完全相同的 Verilog 代碼,但至少它們的抽象范圍是一樣的。 這是與 ASIC 原型設計不同的一個用例。和電路仿真不同,計算加速是 FPGA 的新興用例。這也是微軟最近成功加速搜索和深度神經網絡的原因。而且關鍵的是,計算實例并不依賴于 FPGA 和真正 ASIC 之間的關系:開發人員針對基于 FPGA 的加速編寫的 Verilog 代碼不需要與用來流片的 Verilog 代碼有任何的相似性。

這兩種實例在編程、編譯器和抽象方面存在巨大差異。我比較關注后者,我將其稱為「計算 FPGA 編程」(computaTIonal FPGA programming)。我的論點是,目前計算 FPGA 的編程方法都借鑒了傳統的電路仿真編程模型,這是不對的。如果你想開發 ASIC 原型的話,Verilog 和 VHDL 都是正確的選擇。但如果目標是計算的話,我們可以也應該重新思考整個堆棧。

讓我們開門見山地說吧。FPGA 是一類很特殊的硬件,它用來高效執行模擬電路描述的特殊軟件。FPGA 配置需要一些底層軟件——它是為了 ISA 編寫的程序。 這里可以用 GPU 做類比。 在深度學習和區塊鏈盛行之前,有一段時間 GPU 是用來處理圖形的。在 21 世紀初,人們意識到他們在處理沒有圖形數據的計算密集型任務時,也會大量使用 GPU 作為加速器:GPU 設計師們已經構建了更通用的機器,3D 渲染只是其中一個應用而已。

FPGA的定義以及和GPU的類比

計算 FPGA 遵循了相同的軌跡。我們的想法是要多多使用這一時興的硬件,當然不是為了電路仿真,而是利用適合電路執行的計算模式,用類比的形式來看 GPU 和 FPGA。

為了讓 GPU 發展成今天的數據并行加速器,人們不得不重新定義 GPU 輸入的概念。我們過去常常認為 GPU 接受奇特的、強烈的、特定領域的視覺效果描述。我們實現了 GPU 執行程序,從而解鎖了它們真正的潛力。這樣的實現讓 GPU 的目標從單個應用域發展為整個計算域。 我認為計算 FPGA 正處于類似的轉變中,現在還沒有針對 FPGA 擅長的基本計算模式的簡潔描述。但它和潛在的不規則并行性、數據重用以及大多數靜態的數據流有關。 和 GPU 一樣,FPGA 也需要能夠體現這種計算模式的硬件抽象,Verilog 用于計算 FPGA 的問題在于它在低級硬件抽象中效果不好,在高級編程抽象中的效果也不好。讓我們通過反證法想象一下,如果用 RTL(寄存器傳輸級)取代這些角色會是什么樣。 甚至 RTL 專家可能也無法相信 Verilog 是可以高效開發主流 FPGA 的方式。它不會把編程邏輯推向主流。對于經驗豐富的硬件黑客來說,RTL 設計似乎是友好而熟悉的,但它與軟件語言之間的生產力差距是不可估量的。

事實上,對現在的計算 FPGA 來說,Verilog 實際上就是 ISA。主要的 FPGA 供應商工具鏈會將 Verilog 作為輸入,而高級語言的編譯器則將 Verilog 作為輸出。供應商一般會對比特流格式保密,因此 Verilog 在抽象層次結構中會處于盡可能低的位置。

把 Verilog 當做 ISA 的問題是它和硬件之間的距離太遠了。RTL 和 FPGA 硬件之間的抽象差距是巨大的,從傳統角度講它至少要包含合成、技術映射以及布局布線——每一個都是復雜而緩慢的過程。因此,FPGA 上 RTL 編程的編譯/編輯/運行周期需要數小時或數天,更糟糕的是,這是一個無法預測的過程,工具鏈的深層堆棧可能會掩蓋 RTL 中的改變,這可能會影響設計性能和能源特性。

好的 ISA 應該直接展示底層硬件未經修飾的真實情況。像匯編語言一樣,它其實不需要很方便編程。但也像匯編語言一樣,它的編譯速度需要非常快,而且結果可預測。如果想要構建更高級的抽象和編譯器,就需要一個不會出現意外的低級目標。而 RTL 不是這樣的目標。

如果計算 FPGA 是特定類算法模式的加速器,那當前的 FPGA 并不能理想地實現這一目標。在這個游戲規則下能夠擊敗 FPGA 的新硬件類型,才可能帶來全新的抽象層次結構。新的軟件棧應該摒棄 FPGA 在電路仿真方面的遺留問題,以及 RTL 抽象。

責任編輯:lq

-

FPGA

+關注

關注

1646文章

22056瀏覽量

619009 -

gpu

+關注

關注

28文章

4955瀏覽量

131375 -

深度學習

+關注

關注

73文章

5561瀏覽量

122836

原文標題:FPGA難懂?與GPU類比一下就明白了

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

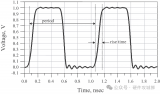

兩個不同頻率晶振靠的近會怎樣

如何把兩個數據返回給調用函數

兩個晶體管能如何實現高效正弦波振蕩?

從時域和頻域兩個角度對信號進行分析

評論