本文轉載自:FPGA開源工作室微信公眾號

在開發以太網接口的過程中經常看到 MII、RMII、GMII、RGMII等英文縮寫名稱。在開發接口前,先將這些名詞搞清楚。

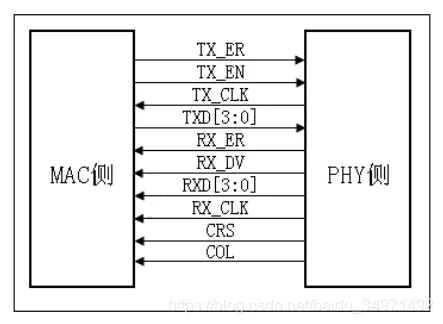

1 MII

MII(Medium Independent Interface)的縮寫,翻譯成中文是“介質獨立接口”,該接口一般應用于以太網硬件平臺的MAC層和PHY層之間,MII接口的類型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

MII支持10兆和100兆的操作,一個接口由14根線組成,它的支持還是比較靈活的,但是有一個缺點是因為它一個端口用的信號線太多

RXD(Receive Data)[3:0]:數據接收信號,共4根信號線;

TX_ER(Transmit Error):發送數據錯誤提示信號,同步于TX_CLK,高電平有效,表示TX_ER有效期內傳輸的數據無效。對于10Mbps速率下,TX_ER不起作用;

RX_ER(Receive Error):接收數據錯誤提示信號,同步于RX_CLK,高電平有效,表示RX_ER有效期內傳輸的數據無效。對于10Mbps速率下,RX_ER不起作用;

TX_EN(Transmit Enable):發送使能信號,只有在TX_EN有效期內傳的數據才有效;

RX_DV(Reveive Data Valid):接收數據有效信號,作用類型于發送通道的TX_EN;

TX_CLK:發送參考時鐘,100Mbps速率下,時鐘頻率為25MHz,10Mbps速率下,時鐘頻率為2.5MHz。注意,TX_CLK時鐘的方向是從PHY側指向MAC側的,因此此時鐘是由PHY提供的。

RX_CLK:接收數據參考時鐘,100Mbps速率下,時鐘頻率為25MHz,10Mbps速率下,時鐘頻率為2.5MHz。RX_CLK也是由PHY側提供的。

CRS:Carrier Sense,載波偵測信號,不需要同步于參考時鐘,只要有數據傳輸,CRS就有效,另外,CRS只有PHY在半雙工模式下有效;

COL:Collision Detectd,沖突檢測信號,不需要同步于參考時鐘,只有PHY在半雙工模式下有效。

MII接口一共有16根線。

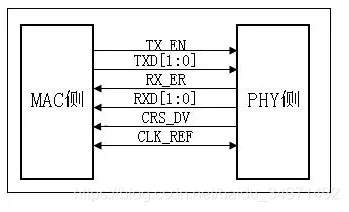

2 RMII

RMII是簡化的MII接口,在數據的收發上它比MII接口少了一倍的信號線,所以它一般要求是50兆的總線時鐘,是MII接口時鐘的兩倍。

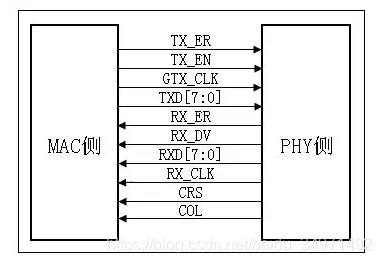

3 GMII

與MII接口相比,GMII的數據寬度由4位變為8位,GMII接口中的控制信號如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一樣,發送參考時鐘GTX_CLK和接收參考時鐘RX_CLK的頻率均為125MHz(1000Mbps/8=125MHz)。

在這里有一點需要特別說明下,那就是發送參考時鐘GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供給MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供給PHY芯片的。兩者方向不一樣。

在實際應用中,絕大多數GMII接口都是兼容MII接口的,所以,一般的GMII接口都有兩個發送參考時鐘:TX_CLK和GTX_CLK(兩者的方向是不一樣的,前面已經說過了),在用作MII模式時,使用TX_CLK和8根數據線中的4根。

GMII是千兆網的MII接口。GMII采用8位接口數據,工作時鐘125MHz,因此傳輸速率可達1000Mbps。同時兼容MII所規定的10/100 Mbps工作方式。

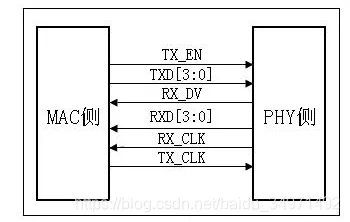

4 RGMII

RGMII接口表示簡化了的GMII接口。RGMII均采用4位數據接口,工作時鐘125MHz,并且在上升沿和下降沿同時傳輸數據,因此傳輸速率可達1000Mbps。同時兼容MII所規定的10/100 Mbps工作方式,支持傳輸速率:10M/100M/1000Mb/s ,其對應clk 信號分別為:2.5MHz/25MHz/125MHz。

審核編輯:何安

-

千兆以太網

+關注

關注

0文章

67瀏覽量

13859 -

以太網接口

+關注

關注

0文章

147瀏覽量

17092

發布評論請先 登錄

相關推薦

RT-Thread 發布 EtherKit開源以太網硬件!

MX60千兆以太網非接觸式連接解決方案

什么是工業以太網?有何特點?

工業以太網和普通以太網區別在哪

基于FPGA的千兆以太網設計

智嵌物聯100/1000BASE-T1千兆車載以太網交換機

關于FPGA千兆以太網的開發

關于FPGA千兆以太網的開發

評論