作者:falwat

版權聲明:本文為博主原創文章,遵循 CC 4.0 BY-SA 版權協議,轉載請附上原文出處鏈接和本聲明。

本文鏈接:https://blog.csdn.net/falwat/article/details/86171571

本文介紹如何在教程(三)基礎上, 關聯ELF輸出文件并使用vivado對系統進行行為仿真。

關聯ELF 文件

在vivado 開發教程(三) 在SDK中創建應用工程 中, 新建的工程經構建最終會生成ELF 輸出文件。 ELF 文件是一種用于二進制文件、可執行文件、目標代碼、共享庫和核心轉儲格式文件(參考:百度百科)。 可以在教程(三)中新建的“test”工程和導入的例程下找到。

切回Vivado, 在塊設計文件“system.bd”上右鍵,選擇菜單“Associate ELF Files.。.”關聯ELF文件。

在彈出的對話框中,點擊“Simulation Sources | sim_1 | system_i | microblaze_0 ”樹右側的“。..”按鈕, 彈出選擇文件對話框。

點擊“Add Files.。.” 按鈕,添加ELF文件。

切換目錄至“D:/Projects/test/test.sdk/test_bsp_xgpio_low_level_example_1/Debug”,選中“test_bsp_xgpio_low_level_example_1.elf”, 添加至列表中, 選中新加入的ELF文件并點擊“OK”完成。

在工程管理視圖 | “Sources”窗口 | “Simulation Sources”文件集 | sim_1 | ELF 下能夠看到剛剛關聯上去的ELF文件。

新建激勵文件

點擊“Sources”窗口頂部的“+”按鈕, 打開添加源文件對話框。 選中“Add or create simulation sources”, 點擊“Next”繼續。

點擊“Create File”按鈕, 在創建源文件對話框中, 輸入文件名。 點擊“OK”, 點擊“Finish”。

在彈出的“Define Module”對話框中, 點擊“OK”即可。 激勵文件不需要有定義輸入輸出端口。

雙擊打開“sim_system.v”文件, 復制“system_wrapper.v”文件中的如下內容到“sim_system.v”的模塊中。

wire [7:0]led_8bits_tri_o;

wire reset;

wire rs232_uart_txd;

wire sysclk_125_clk_n;

wire sysclk_125_clk_p;

system system_i

(.led_8bits_tri_o(led_8bits_tri_o),

.reset(reset),

.rs232_uart_rxd(rs232_uart_rxd),

.rs232_uart_txd(rs232_uart_txd),

.sysclk_125_clk_n(sysclk_125_clk_n),

.sysclk_125_clk_p(sysclk_125_clk_p));

修改sim_system.v“文件中, system_i的輸入信號為”reg“類型, 編寫”initial“塊對輸入信號進行初始化, 為時鐘信號編寫激勵, 將”timescale“ 設置為”1ns / 1ns“。 最終生成的代碼如下所示:

`timescale 1ns / 1ns

module sim_system;

wire [7:0]led_8bits_tri_o;

reg reset;

reg rs232_uart_rxd;

wire rs232_uart_txd;

reg sysclk_125_clk_n;

wire sysclk_125_clk_p = ~sysclk_125_clk_n;

system system_i

(.led_8bits_tri_o(led_8bits_tri_o),

.reset(reset),

.rs232_uart_rxd(rs232_uart_rxd),

.rs232_uart_txd(rs232_uart_txd),

.sysclk_125_clk_n(sysclk_125_clk_n),

.sysclk_125_clk_p(sysclk_125_clk_p));

initial begin

reset = 1;

rs232_uart_rxd = 1;

sysclk_125_clk_n = 0;

#100;

reset = 0; // 復位完成

end

always #4 sysclk_125_clk_n = ~sysclk_125_clk_n; // 125M

endmodule

從”Source“窗口中,選中激勵文件”sim_system.v“, 右鍵選擇菜單”Set as Top“, 將激勵文件設置為頂層。

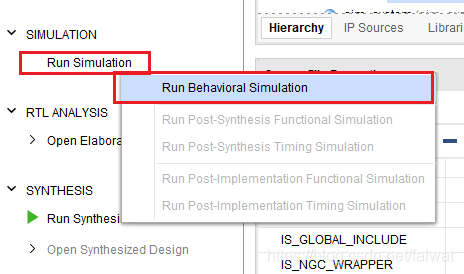

點擊左側”Flow Navigator“工具窗口中的”Simulation“ | ”Run Simulation“, 點擊”Run Behavioral Simulation“, 運行行為仿真。

編譯成功后會自動打開仿真(”SIMULATION“)視圖, 主工具欄會增加如下幾個工具圖標:

為了能夠快速看出仿真效果,縮短仿真時間, 在SDK 中修改”xgpio_low_level_example.c“文件中的宏常量”LED_DELAY“ 改為1000 并保存, SDK在保存后會自動進行編譯, 更新ELF文件。

#define LED_DELAY 1000

切回Vivado, 點擊重新仿真(”Relaunch Simulation“)按鈕。

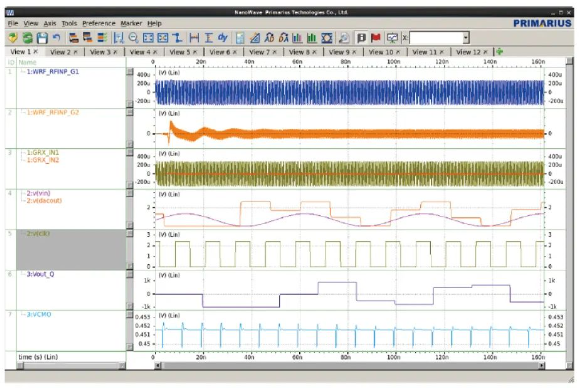

設置仿真時間為500us, 點擊運行指定時間(”Run for 500us“)按鈕。最終的仿真時序圖如下所示。

審核編輯:何安

-

Vivado

+關注

關注

19文章

835瀏覽量

68875

發布評論請先 登錄

飛凌嵌入式ElfBoard ELF 1板卡-文件系統之設置時區

飛凌嵌入式ElfBoard ELF 1板卡-文件系統常用命令之磁盤管理與維護常用命令

飛凌嵌入式ElfBoard ELF 1板卡-busybox構建根文件系統之Busybox編譯

概倫電子大容量波形查看器NanoWave介紹

KiCad 9 探秘(七):使用 Jobset 批量輸出文檔(歸檔)

Vivado Design Suite用戶指南:邏輯仿真

嵌入式學習-飛凌嵌入式ElfBoard ELF 1板卡-shell編程入門之提取字符并設置rtc時間

飛凌嵌入式ElfBoard ELF 1板卡-shell編程入門之提取字符并設置rtc時間

嵌入式學習-飛凌嵌入式ElfBoard ELF 1板卡-Linux C接口編程入門之實戰程序

飛凌嵌入式ElfBoard ELF 1板卡-應用編程示例控制LED燈之sysfs文件系統

飛凌嵌入式ElfBoard ELF 1板卡-Linux C接口編程入門之實戰程序

使用PSpice仿真器對TI智能高側開關中的熱行為進行建模

評論