?具有D寄存器的25位預(yù)加器,以增強(qiáng)A路徑的能力

?INMODE控件支持在乘法(A*B)和加法操作(A:B)之間動(dòng)態(tài)切換的平衡流水

?25*18乘法

?30位的輸入,其下25位為乘法器的A輸入,整個(gè)30位的輸入形成48位A:B的上30位串聯(lián)內(nèi)部總線。

?級(jí)聯(lián)A和B輸入

?直接路徑和級(jí)聯(lián)路徑之間的半獨(dú)立可選pipelining

?獨(dú)立的時(shí)鐘支持兩層的A和B輸入寄存器

?獨(dú)立的C輸入和C寄存器,具有獨(dú)立的復(fù)位和時(shí)鐘啟用。

?CARRYCASCIN和CARRYCASCOUT內(nèi)部級(jí)聯(lián)信號(hào)支持兩個(gè)DSP48E1片中的96位累加器/加法器/減法器

?MULTSIGNIN和MULTSIGNOUT內(nèi)部級(jí)聯(lián)信號(hào)與特殊的OPMODE設(shè)置,以支持一個(gè)96位的MACC擴(kuò)展

?單指令多數(shù)據(jù)(SIMD)模式的三輸入加法器/減法器,在第一階段排除了乘數(shù)的使用

?雙24位SIMD加法器/減法器/累加器,具有兩個(gè)獨(dú)立的結(jié)轉(zhuǎn)信號(hào)

?四路12位SIMD加法器/減法器/累加器,有四個(gè)獨(dú)立的輸出信號(hào)

?48位邏輯單元

?位邏輯操作-雙輸入AND,OR,NOT,NAND,NOR,XOR,XNOR

?邏輯單元模式可通過ALUMODE動(dòng)態(tài)選擇

?模式檢測(cè)器

?溢出/下溢的支持

?收斂舍入支持

?終端計(jì)數(shù)檢測(cè)支持和自動(dòng)復(fù)位

?級(jí)聯(lián)48位P總線支持內(nèi)部低功耗加法器級(jí)聯(lián)

?48位P總線允許12位/4位或24位/雙SIMD加法器級(jí)聯(lián)支持

?可選17位右移,使更廣泛的乘數(shù)實(shí)現(xiàn)

?動(dòng)態(tài)用戶控制的操作模式

?7位OPMODE控制總線提供X、Y和Z多路選擇信號(hào)

?Carryin第二階段加法器

?支持舍入

?支持更廣泛的增加/減少

?3位CARRYINSEL多路復(fù)用器

?Carryout第二階段加法器

?支持更廣泛的增加/減少

?每個(gè)SIMD加法器可用(最多4個(gè))

?級(jí)聯(lián)CARRYCASCOUT和MULTSIGNOUT允許MACC擴(kuò)展到96位

?可選的輸入、流水線和輸出/累加寄存器

可選控制信號(hào)寄存器(OPMODE、ALUMODE和CARRYINSEL)

?獨(dú)立的時(shí)鐘啟用和重置更大的靈活性,重置具有優(yōu)先級(jí)。

?為了在第一階段的乘法器不使用時(shí)節(jié)省電力,USE_MULT屬性允許客戶關(guān)閉內(nèi)部乘法器邏輯。

每個(gè)DSP48E1片都有一個(gè)雙輸入乘法器和一個(gè)三輸入加法器/減法器/累加器。DSP48E1乘法器具有非對(duì)稱的輸入,接受18位2的補(bǔ)數(shù)操作數(shù)和25位2的補(bǔ)數(shù)操作數(shù)。乘法器階段以兩個(gè)部分乘積的形式產(chǎn)生一個(gè)43位2的補(bǔ)碼結(jié)果。這些部分積在X多路復(fù)用器和Y多路復(fù)用器中被符號(hào)擴(kuò)展到48位,并被輸入到三輸入加法器中進(jìn)行最終求和。這將產(chǎn)生一個(gè)43位的乘法輸出,它已經(jīng)被簽名擴(kuò)展到48位。因此,當(dāng)乘法器被使用時(shí),加法器有效地變成一個(gè)雙輸入加法器。

第二階段加法器/減法器接受三個(gè)48位的補(bǔ)數(shù)操作數(shù),并產(chǎn)生一個(gè)48位的補(bǔ)數(shù)操作數(shù),當(dāng)乘法器通過設(shè)置USE_MULT屬性為NONE并使用適當(dāng)?shù)腛PMODE設(shè)置來繞過該乘法器時(shí),得到2的補(bǔ)數(shù)結(jié)果。在SIMD模式下,48位加法器/減法器也支持雙24位或雙12位SIMD算術(shù)運(yùn)算。在這種配置中,動(dòng)態(tài)ALUMODE控制信號(hào)也支持對(duì)兩個(gè)48位二進(jìn)制數(shù)的按位邏輯操作。

在DSP48E1列中,級(jí)聯(lián)各個(gè)DSP48E1片可以支持更高級(jí)的DSP功能。兩個(gè)數(shù)據(jù)路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級(jí)聯(lián)功能。級(jí)聯(lián)數(shù)據(jù)路徑的能力在過濾器設(shè)計(jì)中很有用。例如,有限脈沖響應(yīng)(FIR)濾波器的設(shè)計(jì)可以使用級(jí)聯(lián)輸入來安排一系列的輸入數(shù)據(jù)樣本,使用級(jí)聯(lián)輸出來安排一系列的部分輸出結(jié)果。級(jí)聯(lián)的能力提供了高性能和低功耗的DSP濾波器功能的實(shí)現(xiàn),因?yàn)橐话愕穆酚稍趂abric中沒有使用。

C輸入端口允許形成許多3-輸入數(shù)學(xué)函數(shù),如3-輸入加法或2-輸入加法乘法。這個(gè)函數(shù)的一個(gè)子集是對(duì)乘法趨近于零或無窮大的對(duì)稱舍入的寶貴支持。C輸入和模式檢測(cè)器也支持收斂舍入。

對(duì)于多精度算法,DSP48E1片提供了17的右移。因此,一個(gè)DSP48E1切片的部分積可以右對(duì)齊并添加到相鄰DSP48E1切片中計(jì)算的下一個(gè)部分積。使用這種技術(shù),DSP48E1片可以用來構(gòu)建更大的乘數(shù)。

可編程的輸入操作數(shù)、中間結(jié)果和累加器輸出流水線提高了吞吐量。48位的內(nèi)部總線(PCOUT/PCIN)允許將DSP片聚合到單個(gè)列中。當(dāng)跨越多個(gè)列時(shí),需要使用Fabric邏輯。

DSP48E1片輸出處的Thepatterndetector模式檢測(cè)器支持收斂舍入、溢出/下溢、塊浮點(diǎn)和累加器終端計(jì)數(shù)(計(jì)數(shù)器自動(dòng)復(fù)位)。模式檢測(cè)器可以檢測(cè)DSP48E1片的輸出是否符合模式(由掩碼限定)。

DSP48E1Tile和互連

兩個(gè)DSP48E1片和專用互連形成一個(gè)DSP48E1Tile(參見圖2-3)。DSP48E1Tile垂直地堆疊在DSP48E1列中。DSP48E1Tile的高度與五個(gè)可配置邏輯塊(CLBs)相同,并且與一個(gè)塊RAM的高度匹配。7系列設(shè)備中的塊RAM可分為兩個(gè)18K塊RAM。每個(gè)DSP48E1片與一個(gè)18K塊RAM水平對(duì)齊。7系列設(shè)備最多有20個(gè)DSP48E1列。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21735瀏覽量

603201 -

DSP48E1

+關(guān)注

關(guān)注

0文章

5瀏覽量

604

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

當(dāng)DSP與FPGA通訊的時(shí)候,XZCS0、XZCS6、XZCS7會(huì)影響ADS8556的工作嗎?

ED6H系列FPGA口袋實(shí)驗(yàn)室

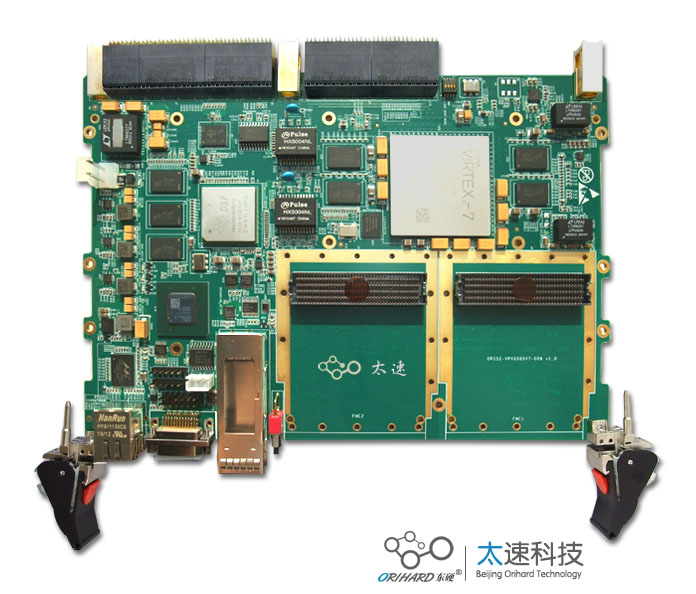

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號(hào)處理卡

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

【RA-Eco-RA2E1-48PIN-V1.0開發(fā)板試用】RA-Eco-RA2E1-48PIN-V1.0開發(fā)板基于Keil MDK環(huán)境搭建

【RA-Eco-RA2E1-48PIN-V1.0開發(fā)板試用】帶你認(rèn)識(shí)RA-Eco-RA2E1-48PIN-V1.0開發(fā)板

【RA-Eco-RA2E1-48PIN-V1.0開發(fā)板試用】1、開箱+環(huán)境搭建

DSP電機(jī)控制程序的概述

臺(tái)達(dá)VFD-E系列變頻器參數(shù)表手冊(cè)表

FPGA核心板 Xilinx Artix-7系列XC7A100T開發(fā)平臺(tái),米爾FPGA工業(yè)開發(fā)板

寬電壓輸入穩(wěn)壓電源模塊 E48_UHFCS-3W系列

Xilinx 7系列FPGA功能特性介紹

Xilinx fpga芯片系列有哪些

華普微強(qiáng)芯加持!低功耗SPI模塊E48系列,可替代多款芯片方案

AMD Xilinx 7系列FPGA的Multiboot多bit配置

7系列FPGA DSP48E1的參數(shù)特點(diǎn)概述

7系列FPGA DSP48E1的參數(shù)特點(diǎn)概述

評(píng)論