原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivado RTL ANALYSIS的使用。

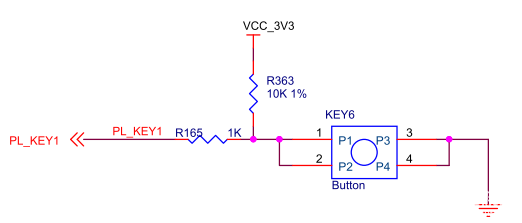

1.按鍵硬件電路

開發板按鍵部分電路

從圖中可以看到,電路的按鍵松開時是高電平,按下時是低電平。

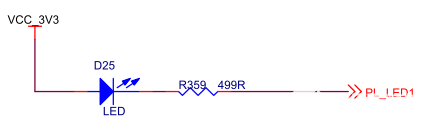

開發板LED部分電路

開發板LED部分電路

而LED部分,高電平滅,低電平亮

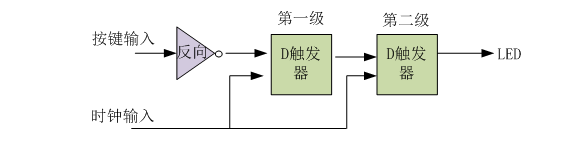

2. 程序設計

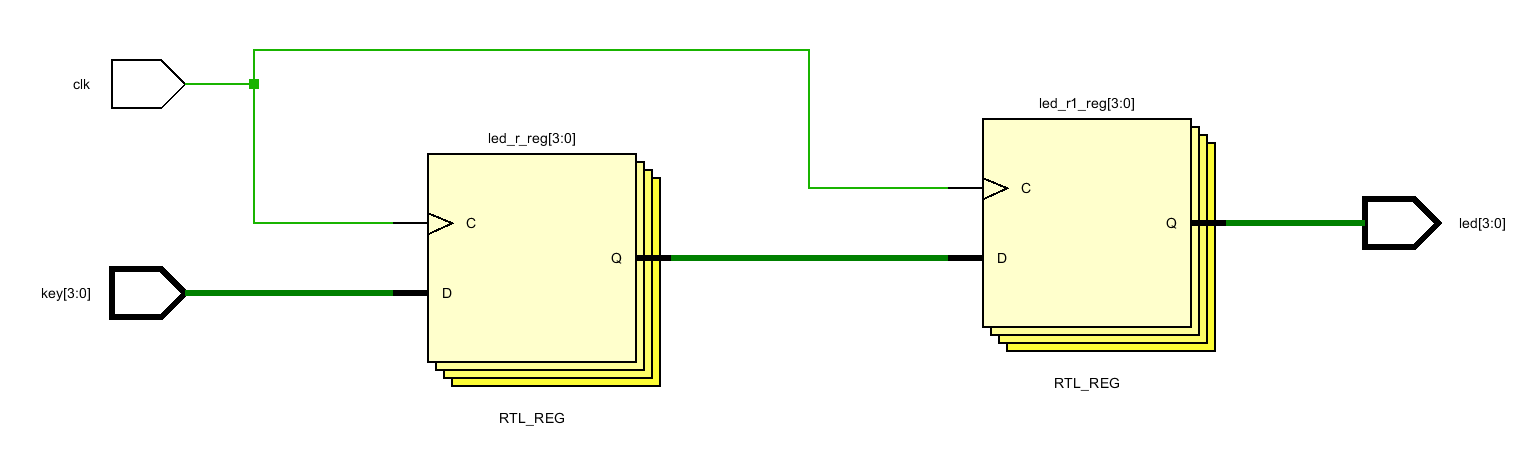

這個程序沒有設計的很復雜,通過簡單的硬件描述語言看透硬件描述語言和FPGA硬件的聯系。首先我們將按鍵輸入經過一個非門后再經過2組D觸發器。經過D觸發器的信號,會在D觸發器時鐘輸入的上升沿鎖存然后再送到輸出。

在進行硬件描述語言編碼之前,我們已經把硬件構建完成,這是一個正常的開發流程。有了硬件設計思路無論是通過畫圖還是通過Verilog HDL、VHDL都能完成設計,根據設計的復雜程序和對某種語言的熟悉程序來選擇工具。

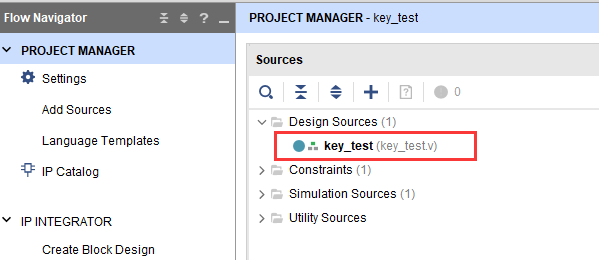

3. 創建Vivado工程

3.1 首先建立按鍵的測試工程,添加verilog測試代碼,完成編譯分配管腳等流程。

`timescale1ns/1psmodulekey_test( inputclk,//systemclock25Mhzonboard input[3:0]key,//inputfourkeysignal,whenthekeydown,thevalueis0 output[3:0]led//LEDdisplay,whenthesiganllow,LEDlighten);reg[3:0]led_r;//definethefirststageregister,generatefourDFlip-flop reg[3:0]led_r1;//definethesecondstageregister,generatefourDFlip-flopalways@(posedgeclk)begin led_r<=??key;//first?stage?latched?dataendalways@(posedge?clk)begin led_r1?<=?led_r;//second?stage?latched?dataendassign?led?=?led_r1;endmodule

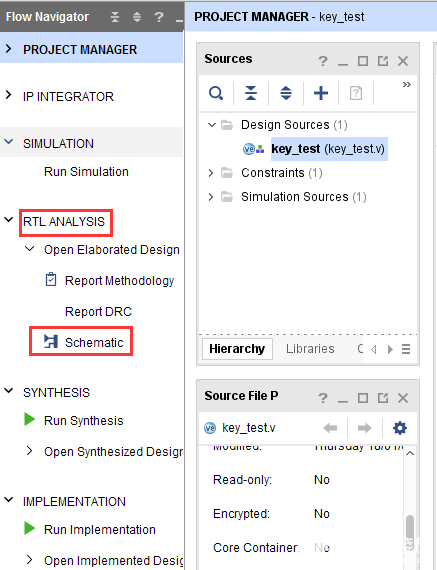

3.2 我們可以使用RTL ANALYSIS工具查看設計

3.3 分析RTL圖,可以看出兩級D觸發器,和預期設計一致。

4. 板上驗證

Bit文件下載到開發板以后,開發板上的"PL LED"處于亮狀態,按鍵“PL KEY1”按下“PL LED1”滅。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603018 -

按鍵

+關注

關注

4文章

223瀏覽量

57595 -

Zynq

+關注

關注

10文章

609瀏覽量

47175 -

MPSoC

+關注

關注

0文章

198瀏覽量

24272 -

Vivado

+關注

關注

19文章

812瀏覽量

66476

發布評論請先 登錄

相關推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

在米爾電子MPSOC實現12G SDI視頻采集H.265壓縮SGMII萬兆以太網推流

九章云極DataCanvas公司與云南聯通簽署合作協議

揚帆出海!九章云極DataCanvas公司驚艷亮相迪拜GITEX Global 2024

在米爾電子MPSOC實現12G SDI視頻采集H.265壓縮SGMII萬兆以太網推流

《DNK210使用指南 -CanMV版 V1.0》第九章 打印輸出實驗

九章云極DataCanvas算力包正式發布

使用TPS65086x PMIC為Xilinx Zynq UltraScale MPSoC供電

第九章-PID整定方法 STM32PID驅動編碼器 STM32PID控制電機轉速

一個更適合工程師和研究僧的FPGA提升課程

AMD推出全新Spartan UltraScale+ FPGA系列

AMD推出Spartan UltraScale+ FPGA系列產品

AMD推出全新Spartan UltraScale+ FPGA系列

在FPGA上為FPGA設計PCB的步驟詳解

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

評論