本文轉載自:VagueCheung的博客

賽靈思公司(Xilinx)推出Vitis——這是一款統一軟件平臺,可以讓包括軟件工程師和AI科學家在內的廣大開發者都能受益于硬件靈活應變的優勢。歷經5年、投入總計1000人打造而成,Vitis統一軟件平臺無需用戶深入掌握硬件專業知識,即可根據軟件或算法代碼自動適配和使用賽靈思硬件架構。此外,Vitis 平臺不限制使用專有開發環境,而是可以插入到通用的軟件開發工具中,并利用豐富的優化過的開源庫,使開發者能夠專注于算法的開發。Vitis獨立于Vivado設計套件,后者仍然繼續為希望使用硬件代碼進行編程的用戶提供支持。但是,Vitis也能夠通過將硬件模塊封裝成軟件可調用的函數, 從而提高硬件開發者的工作效率。

Vitis統一軟件平臺的四層架構

Vitis構建在基于堆棧的架構之上,共有四層。

第一層是基礎層,是Vitis目標平臺。該平臺由電路板和預編程I/O構成;

第二層是Vitis 核心開發套件,覆蓋開源賽靈思運行時庫,以管理不同域間的數據移動, 包括子系統、即將發布的Versal ACAP內的AI 引擎和必要的外部主機。此外,該層也提供編譯器、分析器和調試器等核心開發工具。這些工具均能與業界標準的構建系統與開發環境無縫集成;

在第三層,8個Vitis 庫提供400余種優化的開源應用。這8個庫分別是:Vitis 基本線性代數子程序(B LAS)庫、Vitis 求解器庫、Vitis安全庫、Vitis視覺庫、Vitis數據壓縮庫、Vitis計量金融庫、Vitis數據庫集和Vitis AI 庫。借助這些庫,軟件開發者可以使用標準的應用編程接口(API)來實現硬件加速;

Vitis AI是Vitis 平臺的第四層,也是最具有變革意義的一層。它集成了特定領域架構(DSA)。 DSA 提供了針對AI模型的硬件實現,開發者可以使用包括TensorFlow和Caffe等業界領先框架對其進行配置與編程。Vitis AI提供的工具鏈能在數分鐘內完成優化、量化和編譯操作,在賽靈思器件上高效地運行預先訓練好的AI模型。此外,它也為從邊緣到云端的部署提供了專用API,實現業界一流的推斷性能與效率。賽靈思陸續還將推出另一個DSA(Vitis Video),支持從FFmpeg直接進行編碼并提供同樣超級簡單且功能極強大的端到端視頻解決方案。目前,由合作伙伴公司提供的DSA包括:與GATK 集成用于基因分析的Illumina,與ElasticSearch 集成用于大數據分析的BlackLynx, 以及當前我們客戶正在使用的專有DSA。

Vitis擁有三大特點:第一是開放,第二是標準,第三是免費。首先,Vitis統一軟件平臺支持在賽靈思異構平臺上開發嵌入式軟件和加速應用,包括FPGA、SoC和Versal ACAP,為邊緣、云和混合計算應用 加速提供了統一編程模型。其次,Vitis可與高層次框架進行集成,可以通過加速庫采用C、C++或Python進行開發,也可以使用基于RTL的加速器和低層次運行是API對實現方案進行粒度更精確的控制。

硬件加速應用程序開發流程:

對于基于FPGA的加速,Vitis核心開發套件支持用戶通過API函數創建軟件應用程序,例如OpenCL函數,在Alveo加速卡上運行加速硬核。Vitis核心開發套件也支持將軟件程序運行在基于Linux的嵌入式處理器平臺上,例如ZYNQ的UltraScale+MPSOC設備。對于嵌入式處理器平臺Vitis開發套件執行模型也通過OpenCL API和基于Linux的Xilinx運行庫(XRT)來調度硬核和控制數據的搬移。(加速庫和xilinx運行庫在GitHub上可下載)

Vitis核心開發套件可支持Alveo U50、U200、U250、U280加速卡,也支持zcu102、zcu104、zc702、zc706嵌入式處理器平臺。除了以上比較流行的平臺外,同時也支持自定義平臺。

Vitis軟件平臺允許用戶將數據中心應用程序移植到嵌入式平臺上。Vitis核心開發套件不僅具有適用于硬核的V++編譯器。也具有運行在X86主機的g++編譯器和運行在Xilinx設備的嵌入式處理器的Arm編譯器

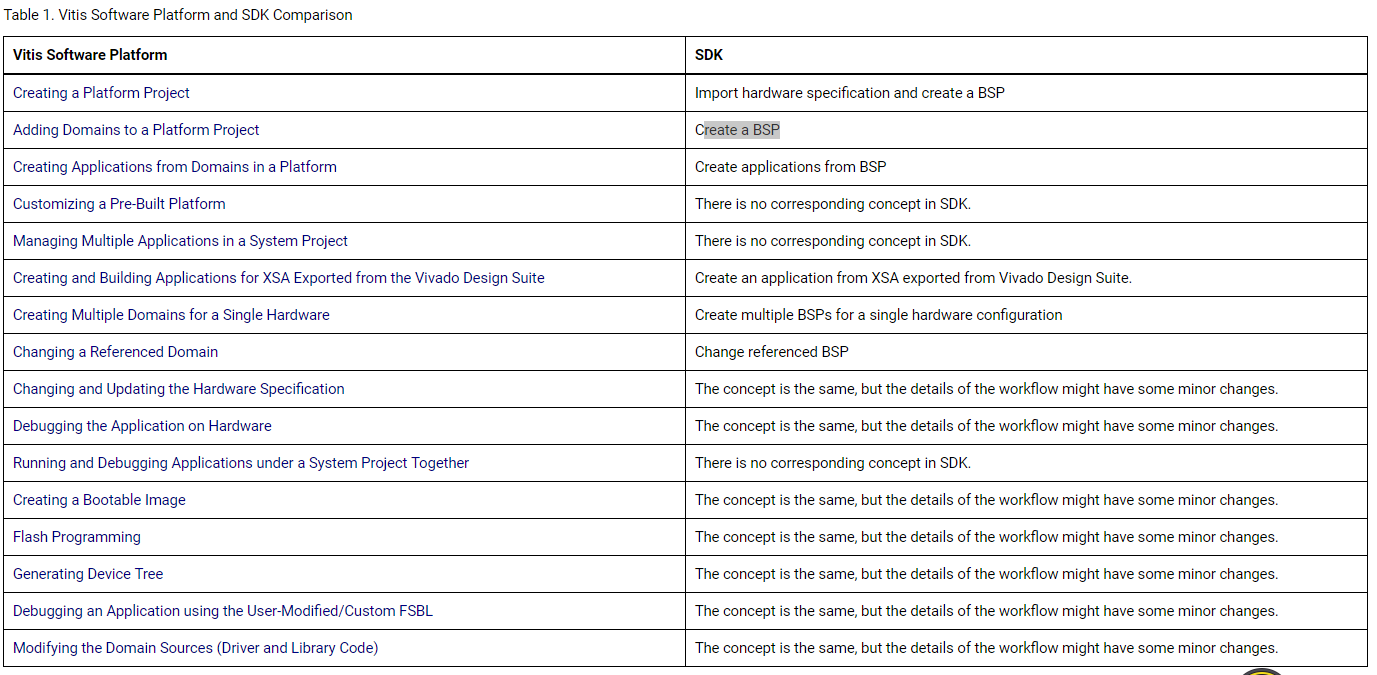

Vitis與SDK對比:

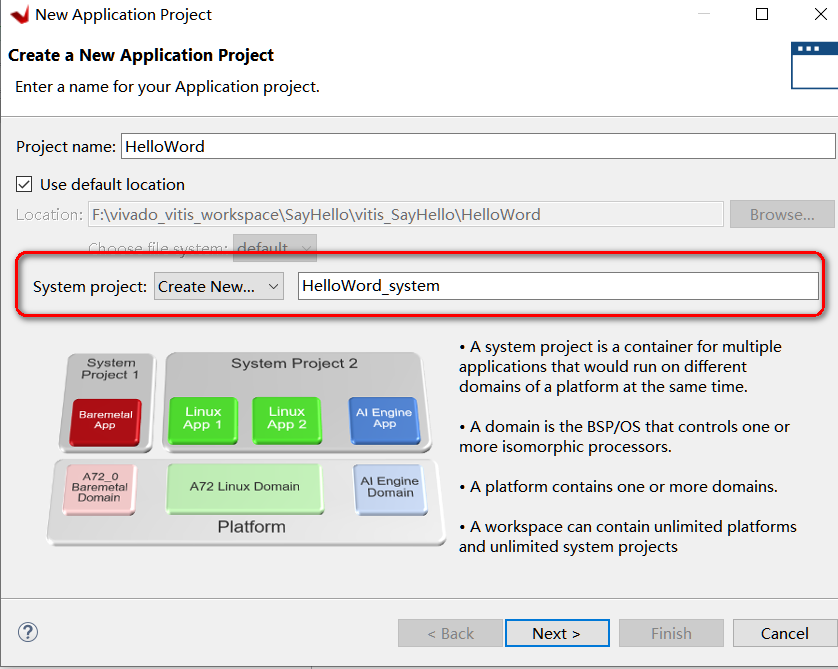

系統項目指的是什么?域domain可以理解成SDK中的BSP么?

系統項目就是指在Vitis中創建的application。

| Vitis軟件平臺 | SDK |

| 可在Vitis中直接創建一個平臺項目(需要添加vivado生成的XSA文件或者從平臺庫中添加任意平臺作為基礎例如vck190.xsa、zc702.xsa、zc706.xsa、zcu102.xsa、zed.xsa) | SDK是從vivado工程中導出硬件平臺項目 |

| 為平臺添加域 | 創建BSP |

| 創建應用程序(通過平臺的域) | 創建應用程序(通過BSP) |

| 改制一個預置平臺 | 無提及 |

| 可在一個系統項目中管理多個應用程序 | 無提及 |

| 修改并且更新硬件 | 基本相同,工作流程可能有細微改變 |

| 在硬件上調試應用程序 | 基本相同,工作流程可能有細微改變 |

| 在一個系統項目下運行和調試應用程序 | 無提及 |

| 創建boot image | 基本相同,工作流程可能有細微改變 |

| Flash 編程 | 基本相同,工作流程可能有細微改變 |

| 生成設備樹 | 基本相同,工作流程可能有細微改變 |

| 通過User-Modify/Custom FSBL測試應用程序 | 基本相同,工作流程可能有細微改變 |

| 修改域源文件 | 基本相同,工作流程可能有細微改變 |

實測Vitis編譯時間要比SDK編譯時間略長;

Vitis實現簡單的HelloWord

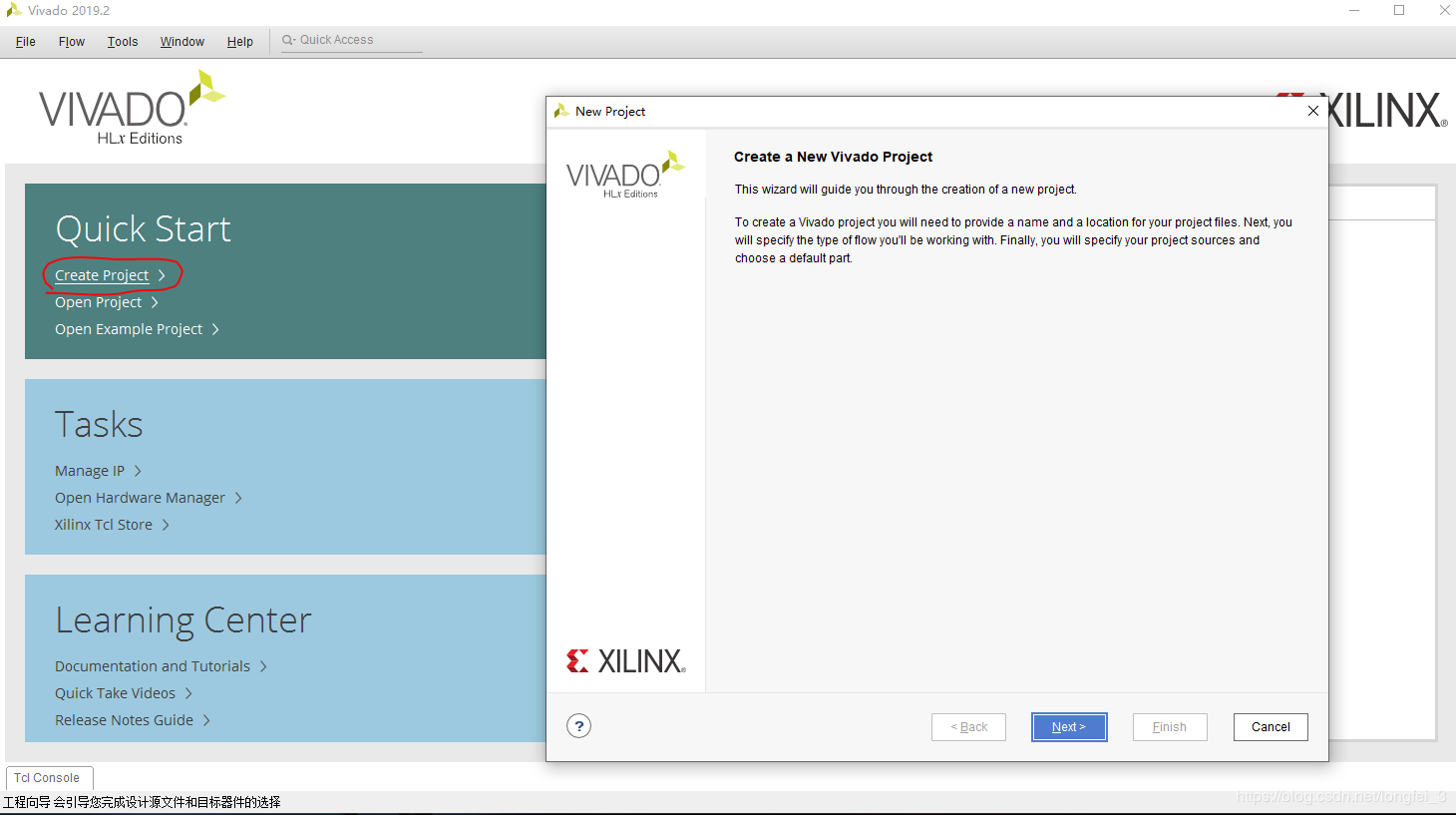

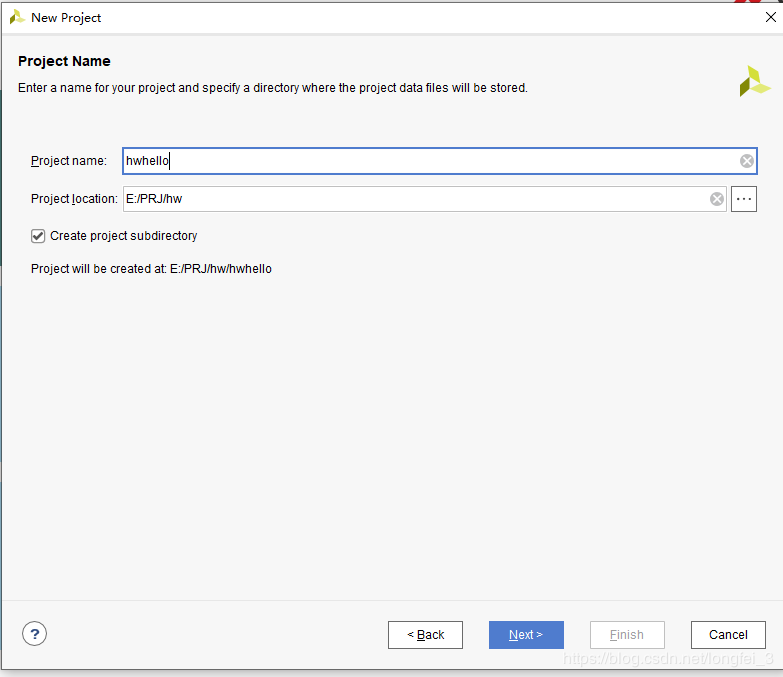

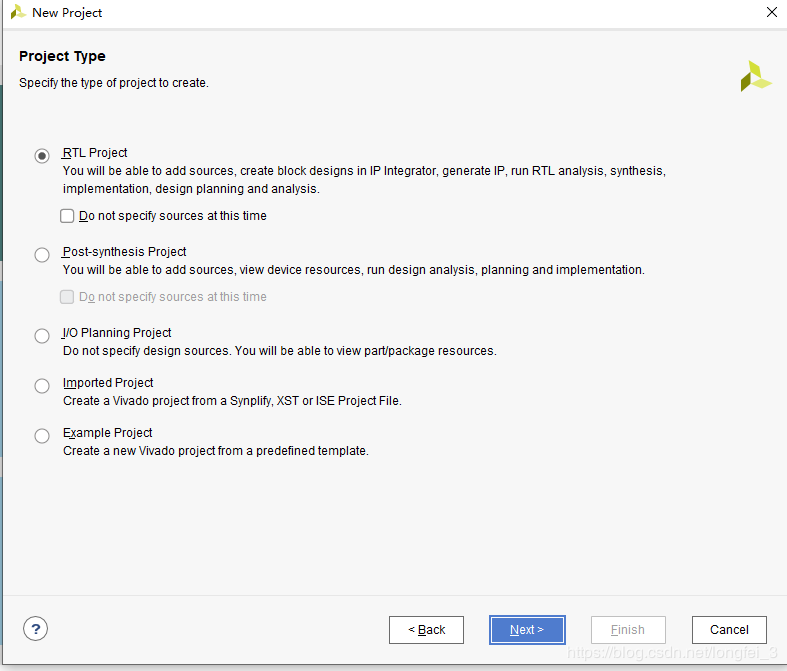

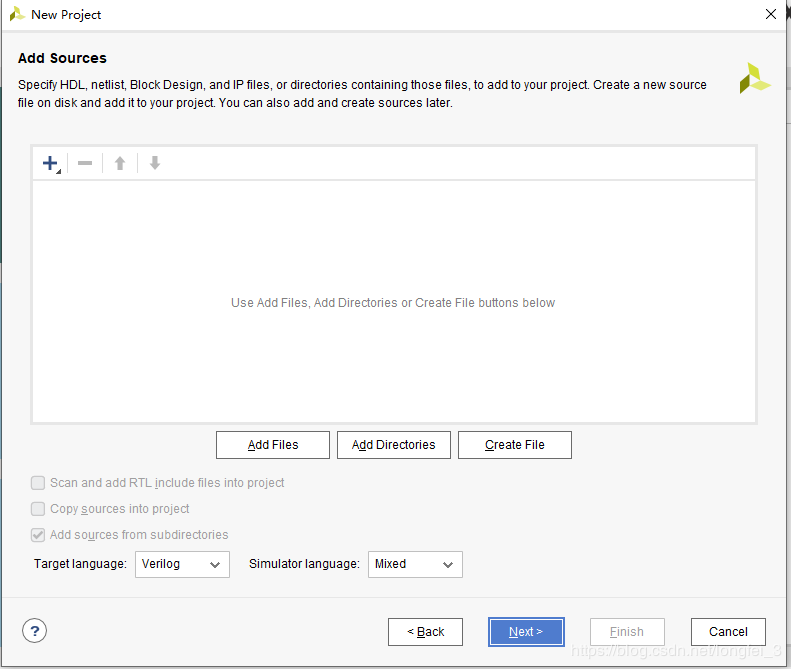

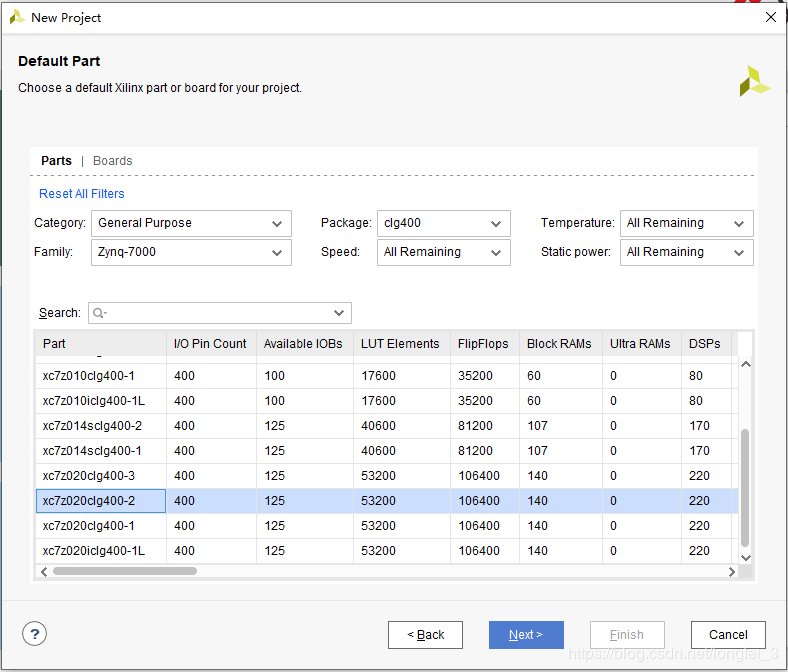

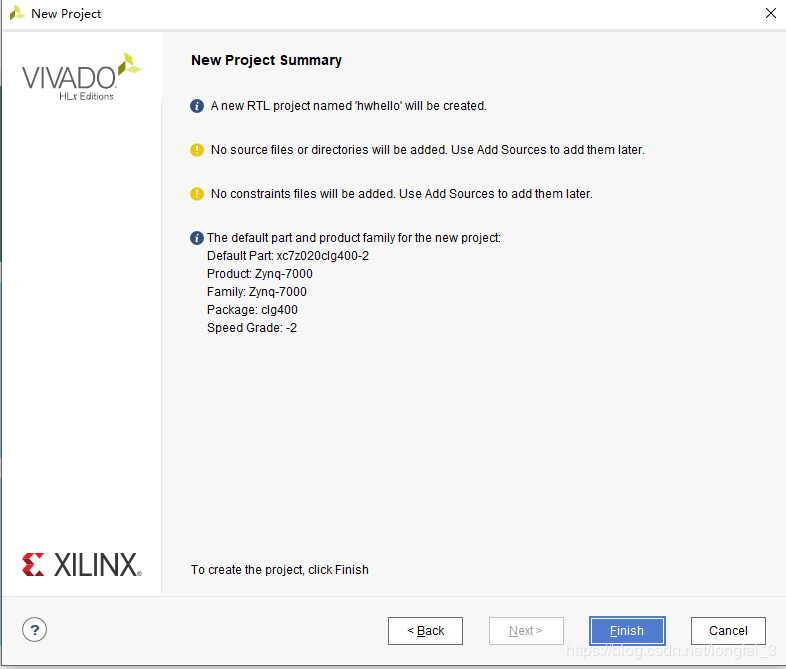

基于黑金ZYNQ 7020開發板創建工程,打開vivado2019.2一步步創建工程,vivado部分還是與之前一模一樣沒有任何改變。

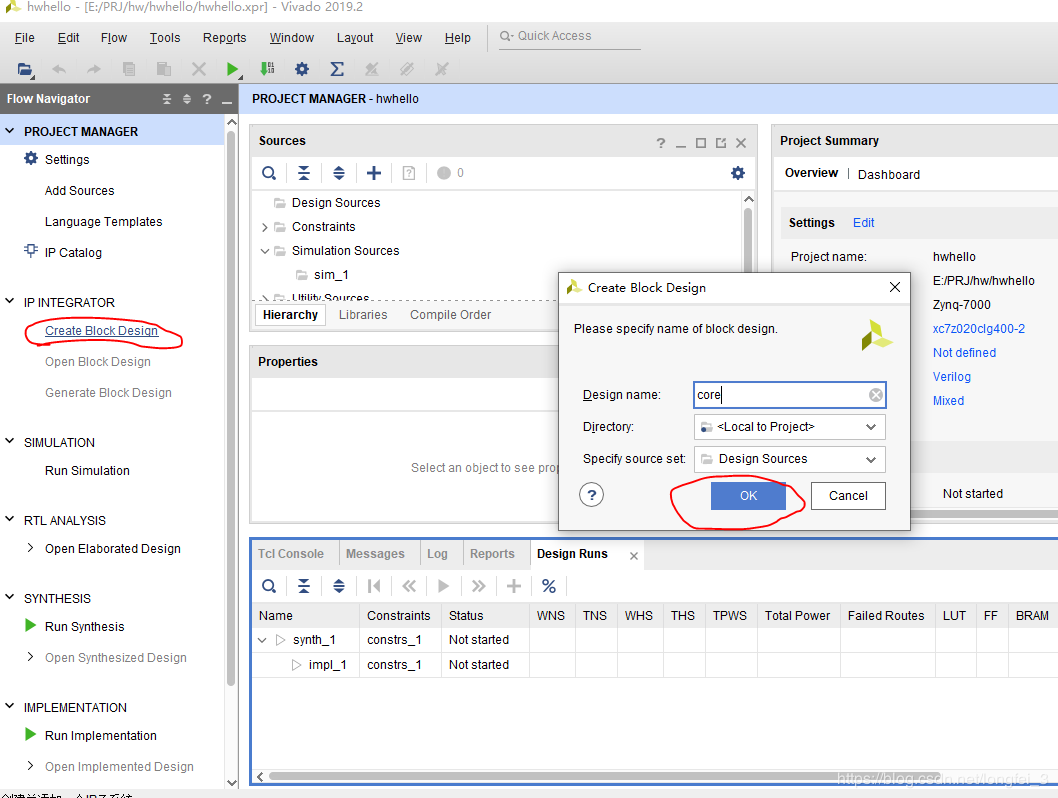

創建完工程,創建同一個 Block Design工程

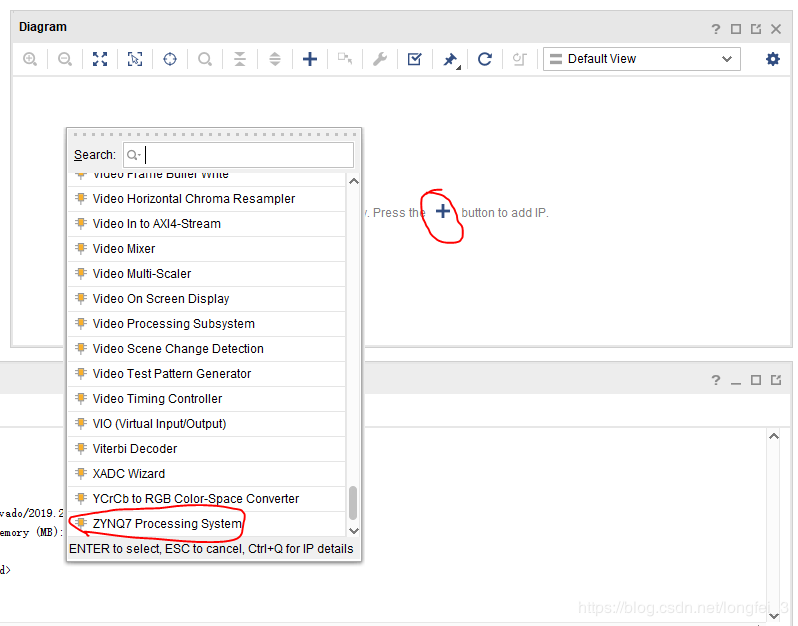

添加ZYNQ 核

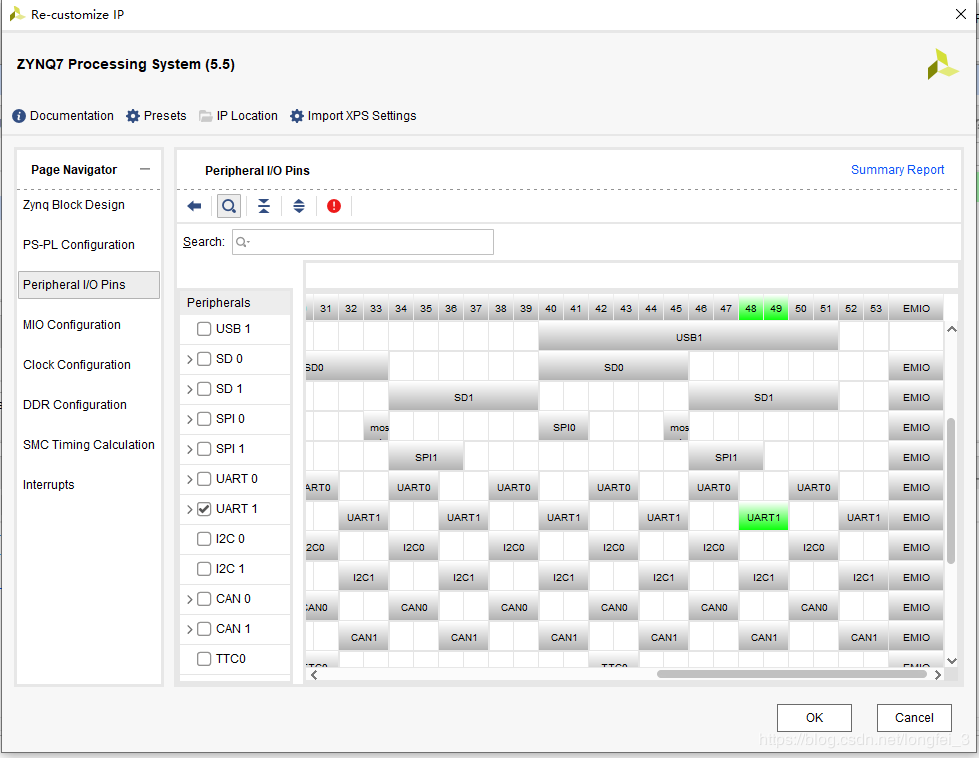

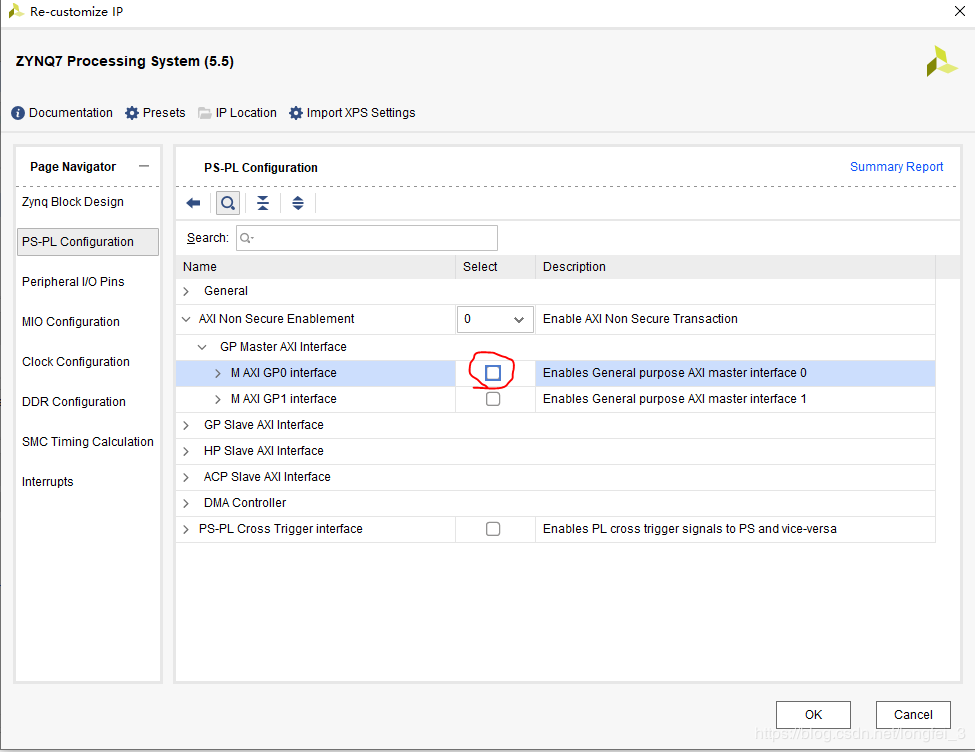

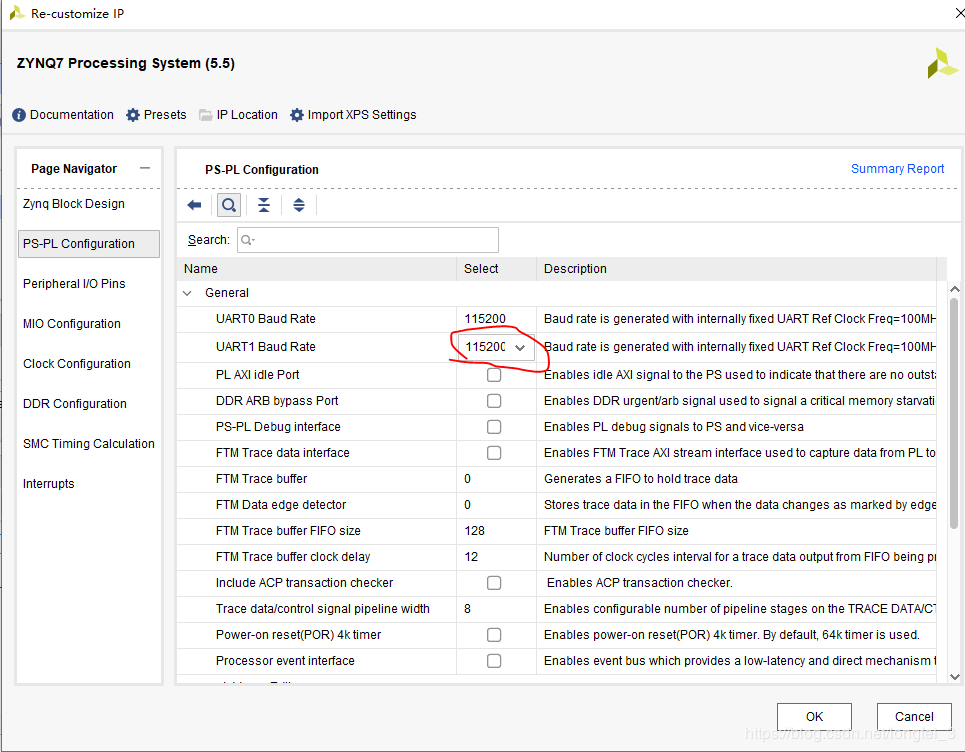

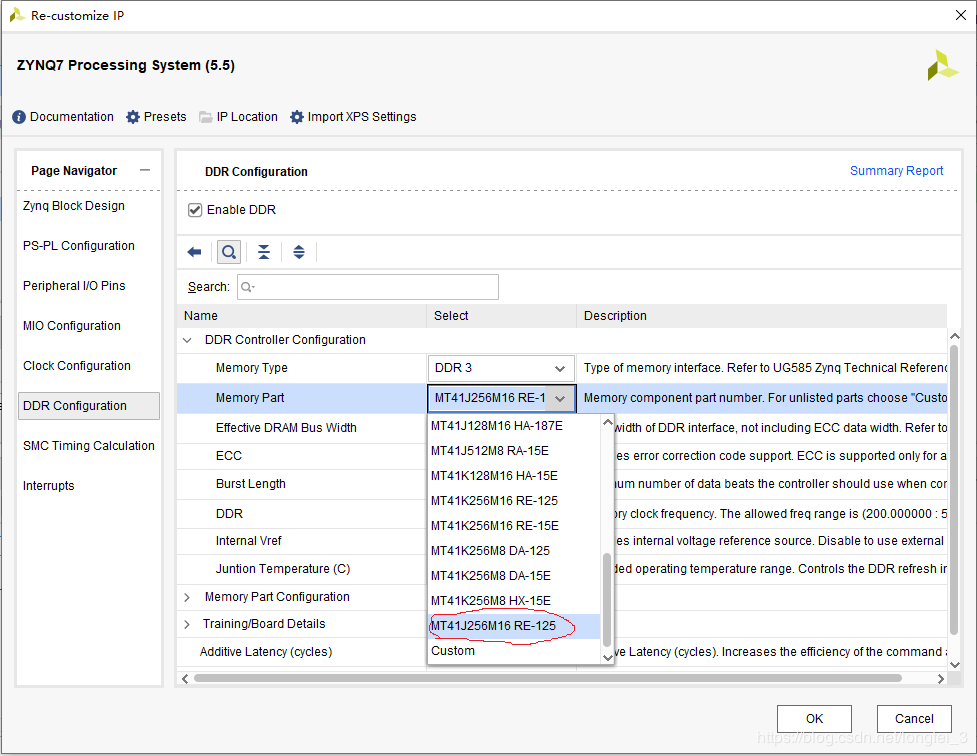

雙擊ZYNQ核設置一下,這里設置跟板子一致UART1,波特率選擇115200,沒有用到PL,AXI也沒使用。

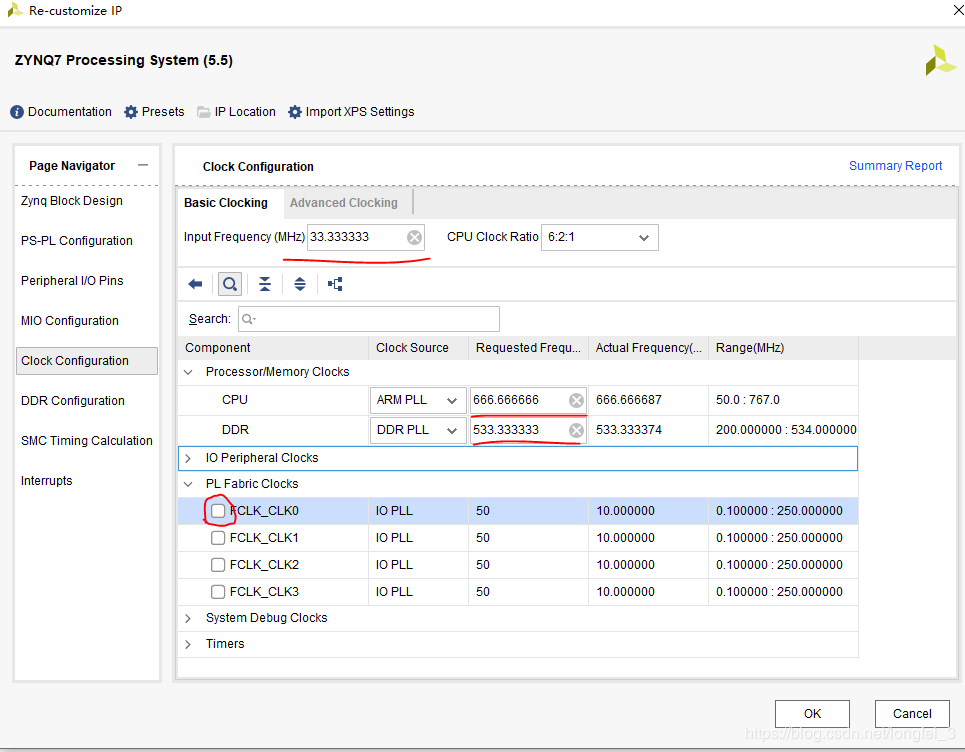

時鐘默認即可,黑金的7020最高可以跑到767Mhz。

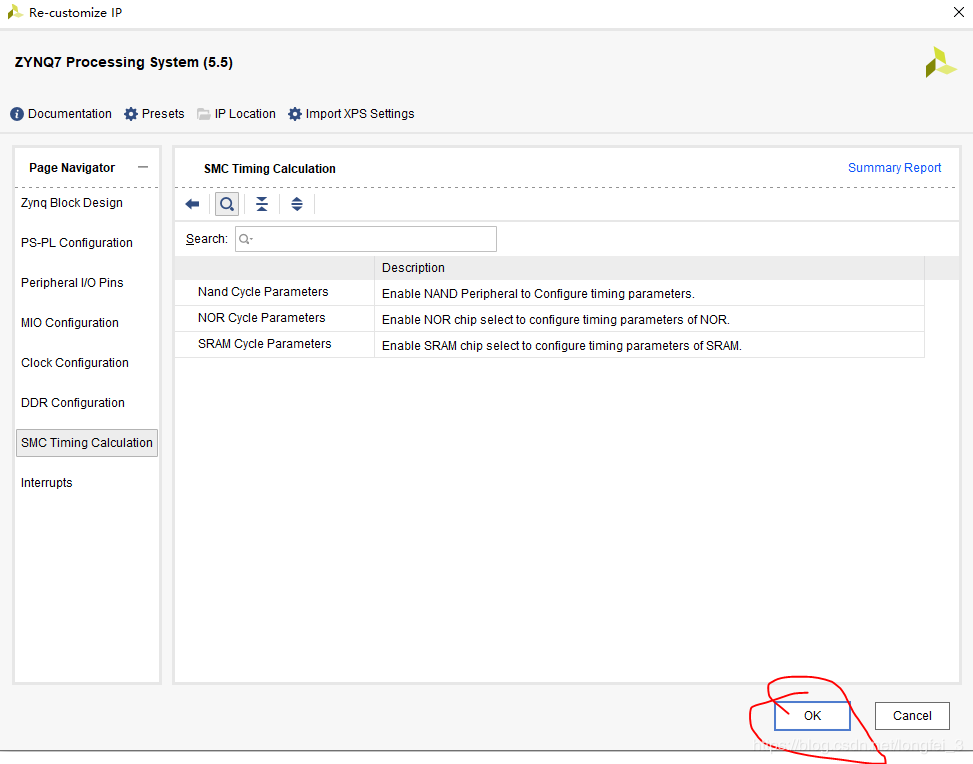

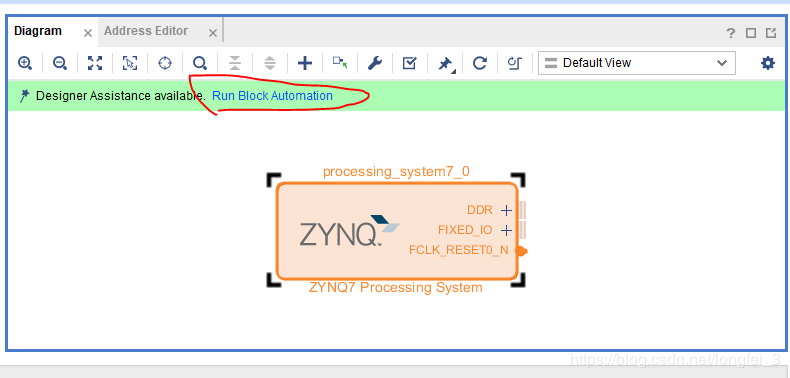

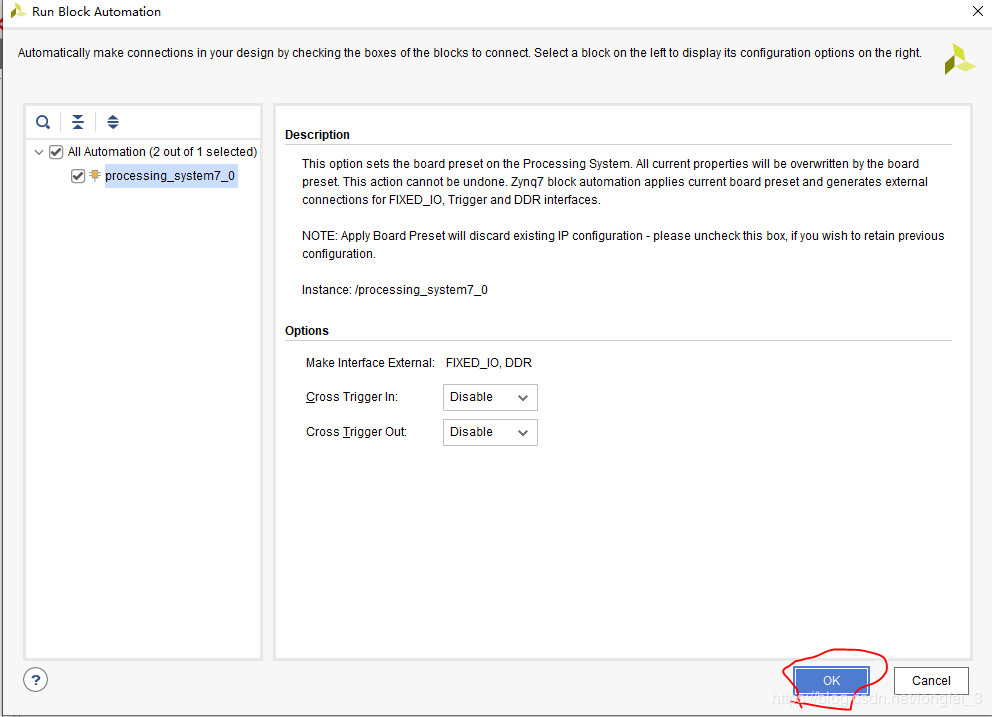

設置完成。自動連線。

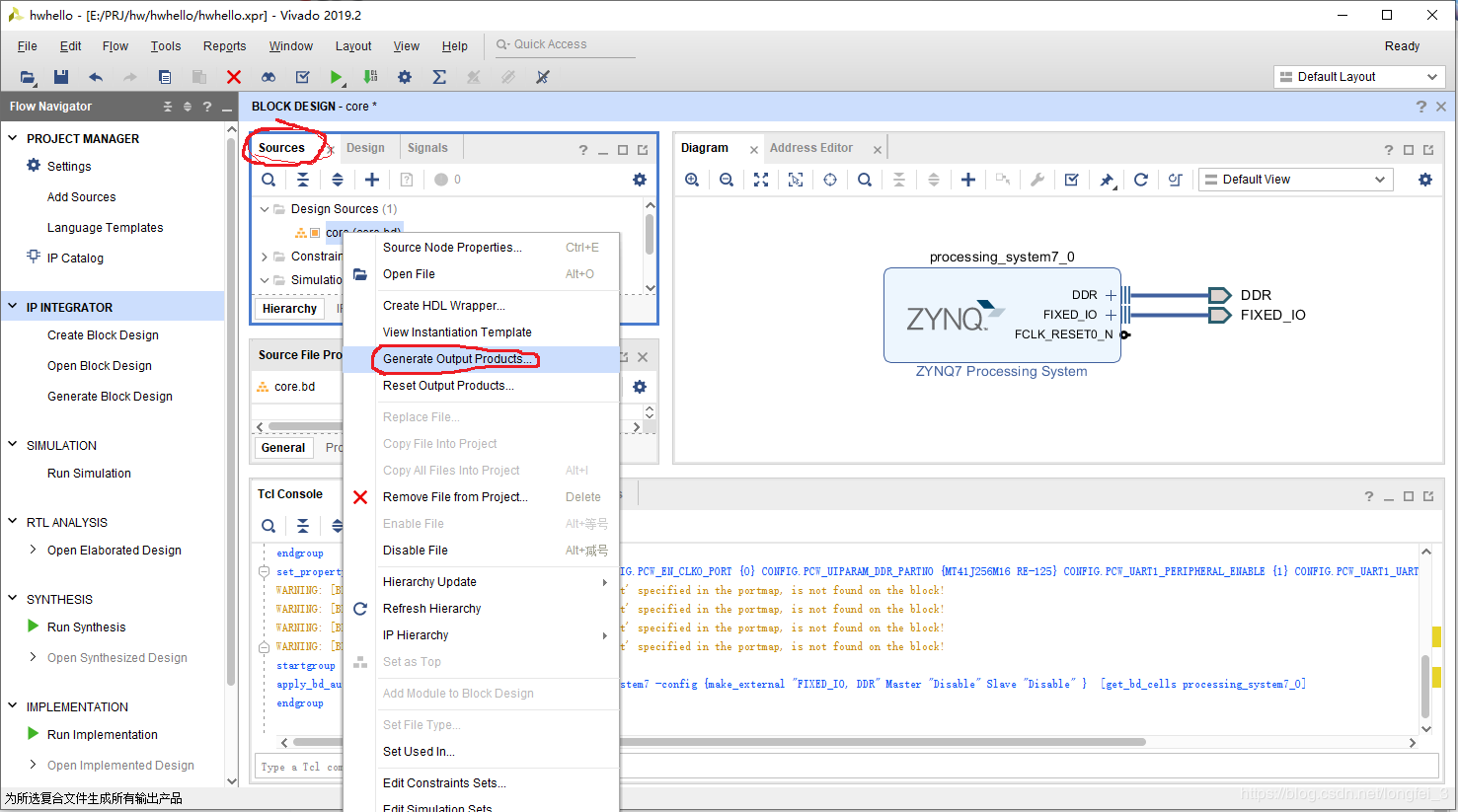

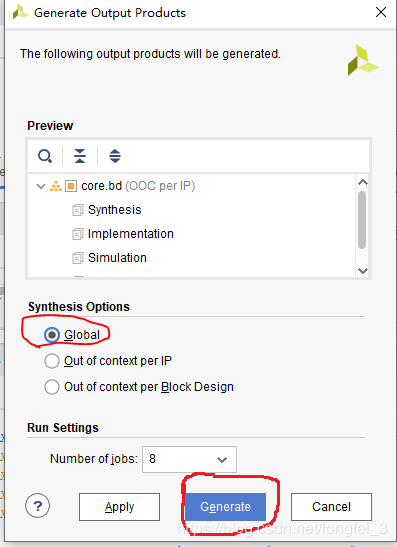

生成文件:

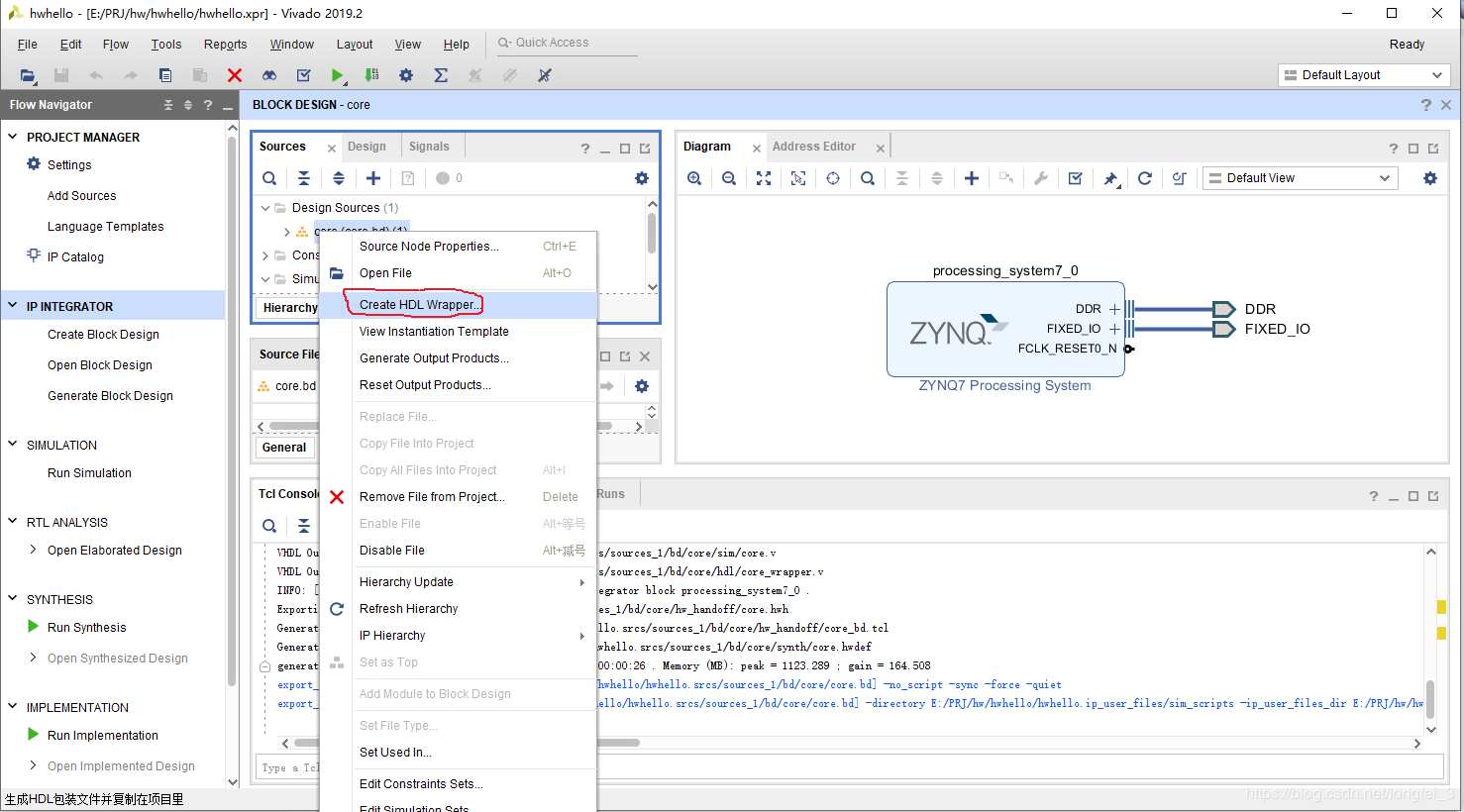

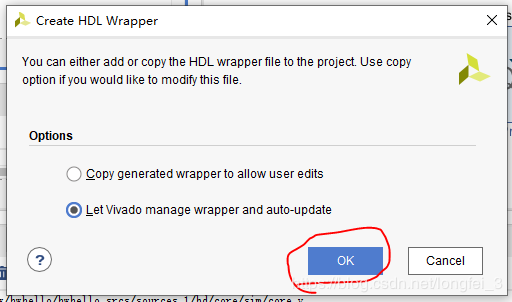

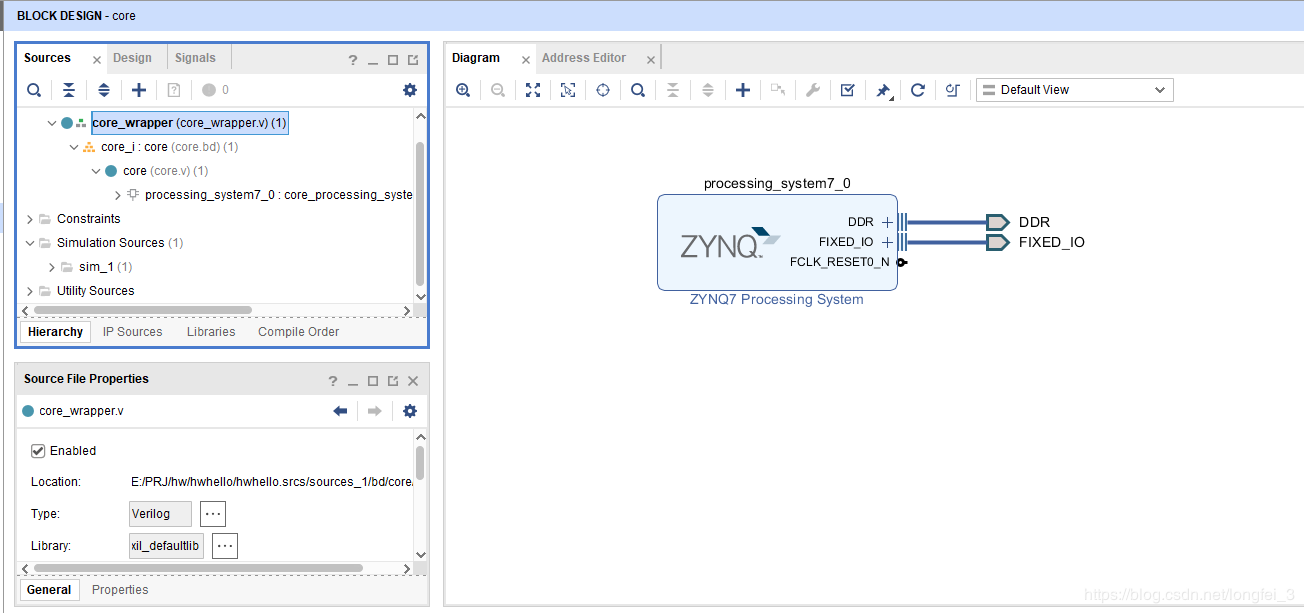

生成頂層文件:

至此PL部分完成了。

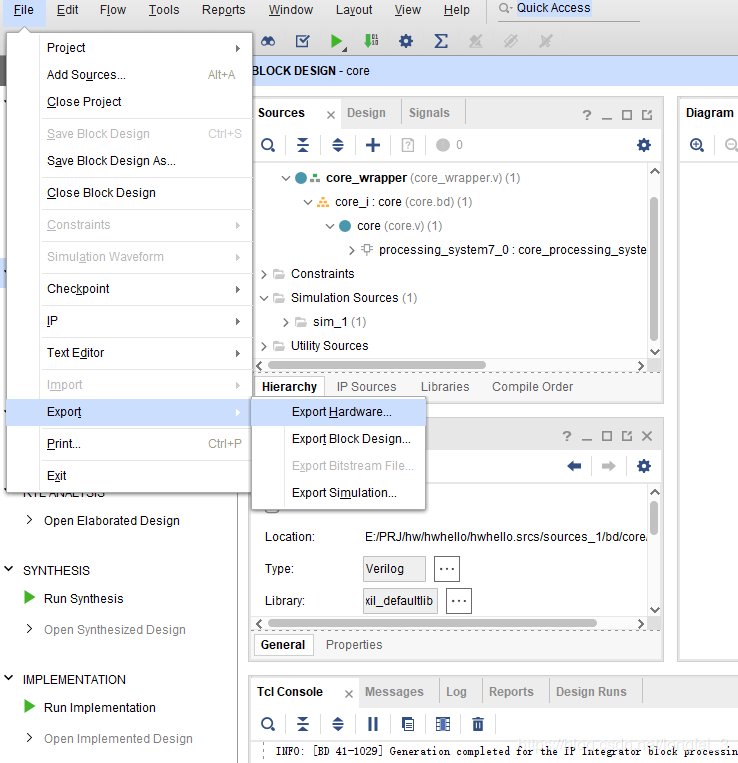

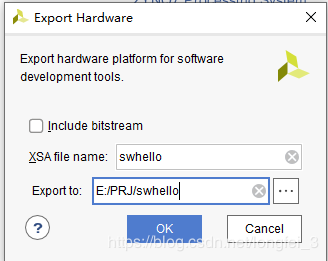

導出設計到軟件,沒有用到PL,所以不用綜合生成bit文件了,這里直接導出

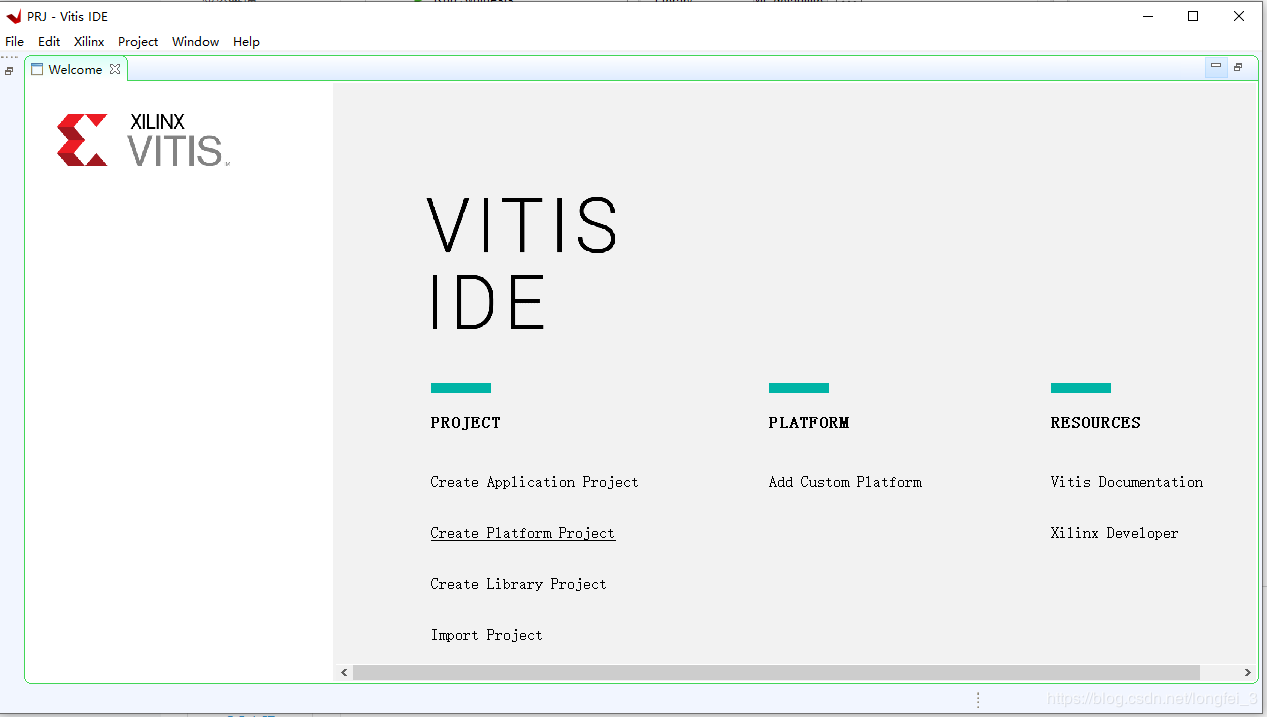

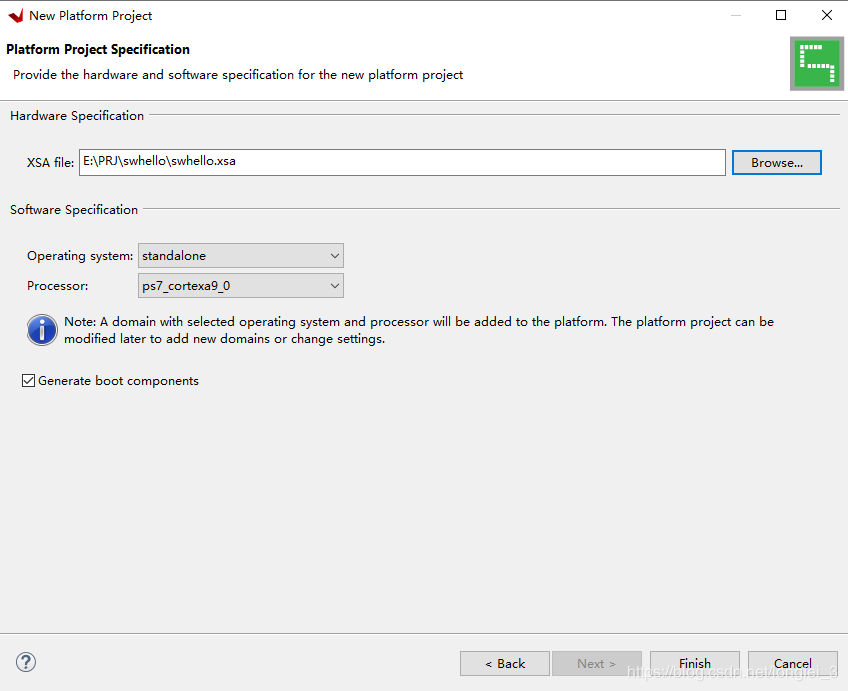

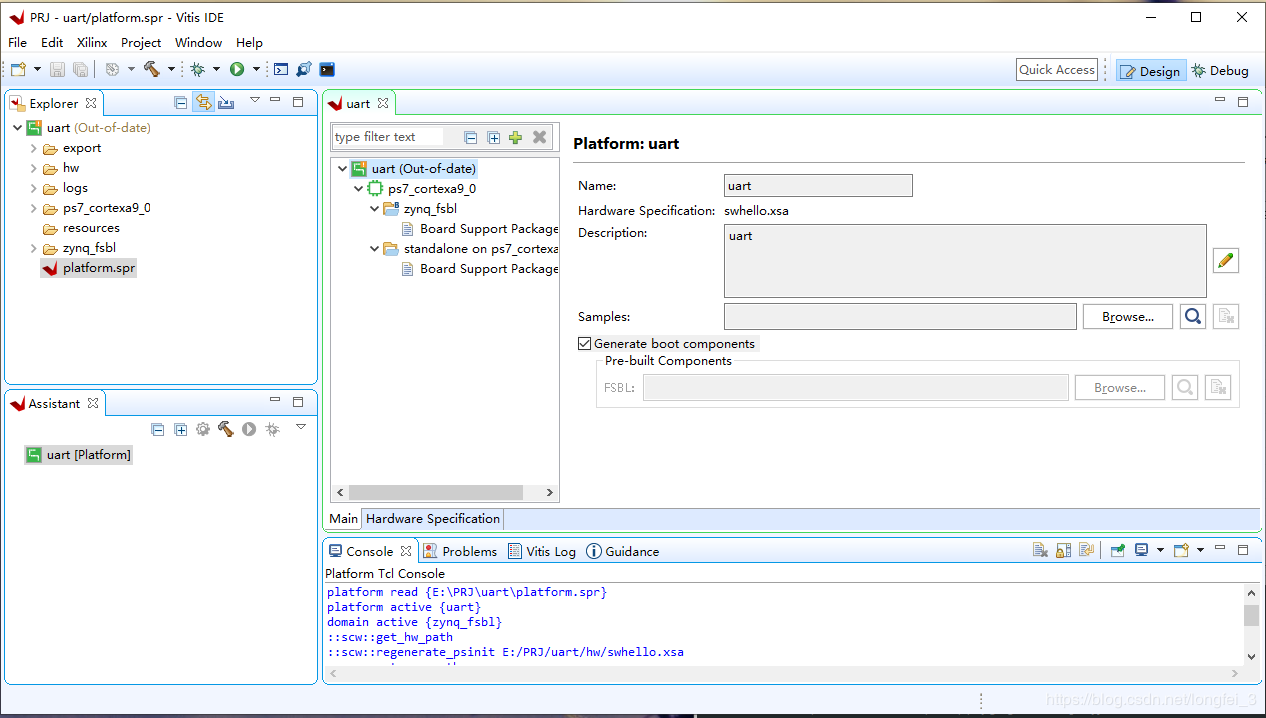

導出完成,這里開始軟件操作,打開vitis先創建一個 platform project導入剛才的設計xsa文件。

這里與SDK不同,SDK是從vivado直接Launch打開,而Vitis是獨立與vivado IDE的開發工具。

選擇Vivado導出的設計,點擊 finish完成

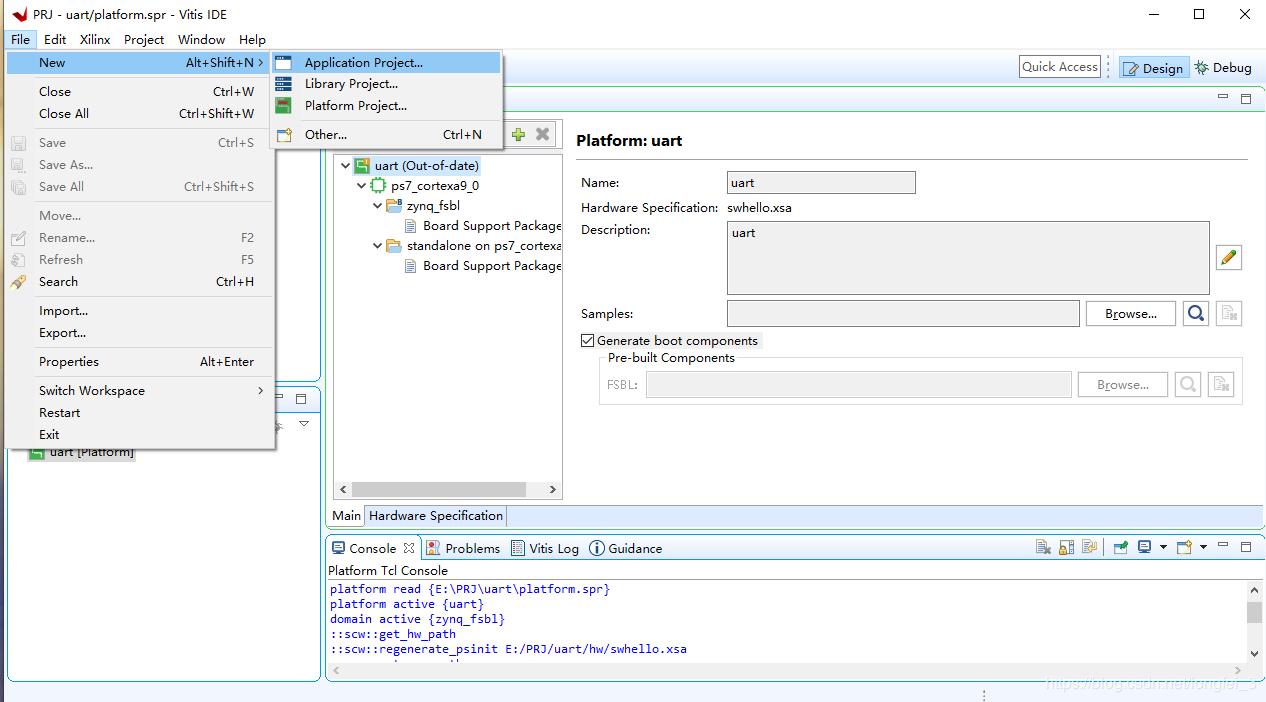

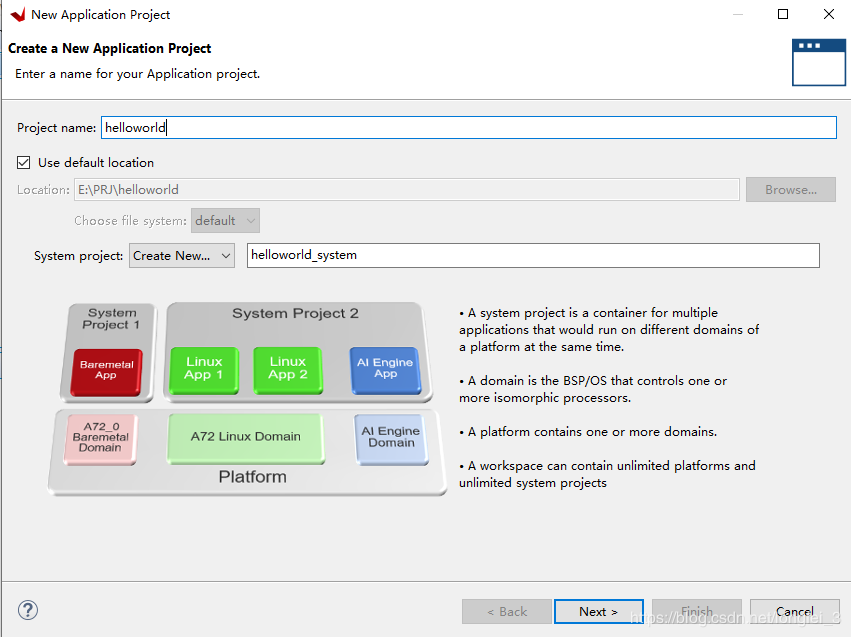

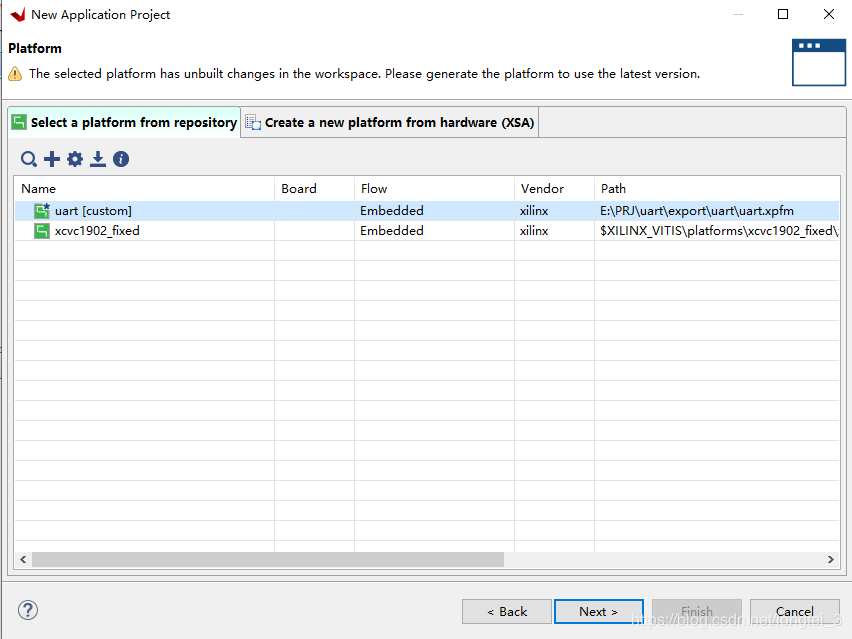

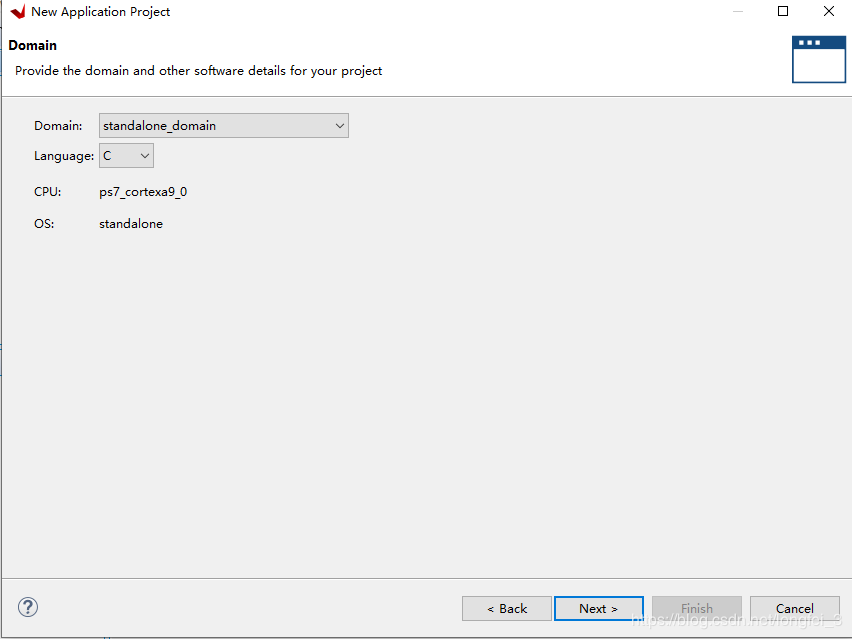

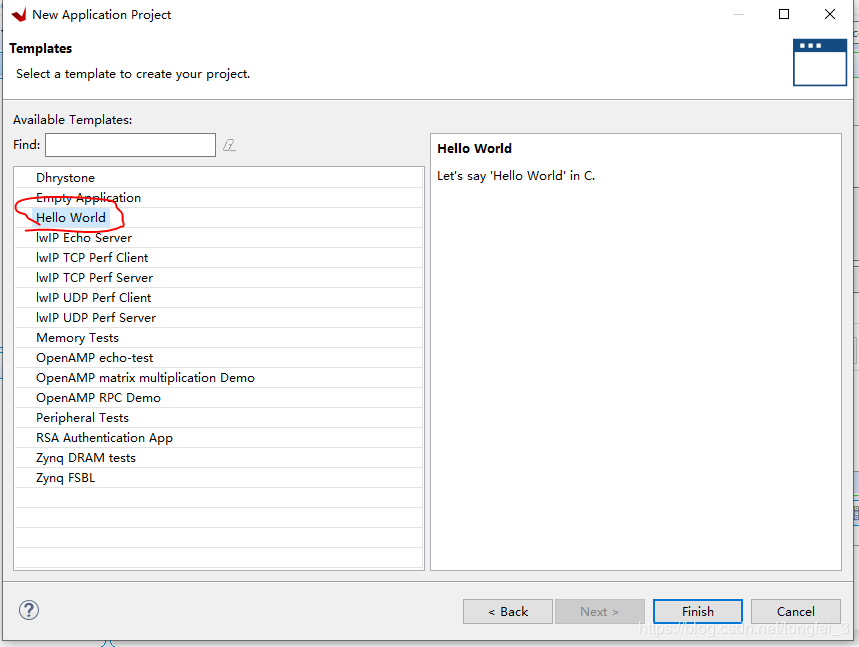

創建一個Application project:

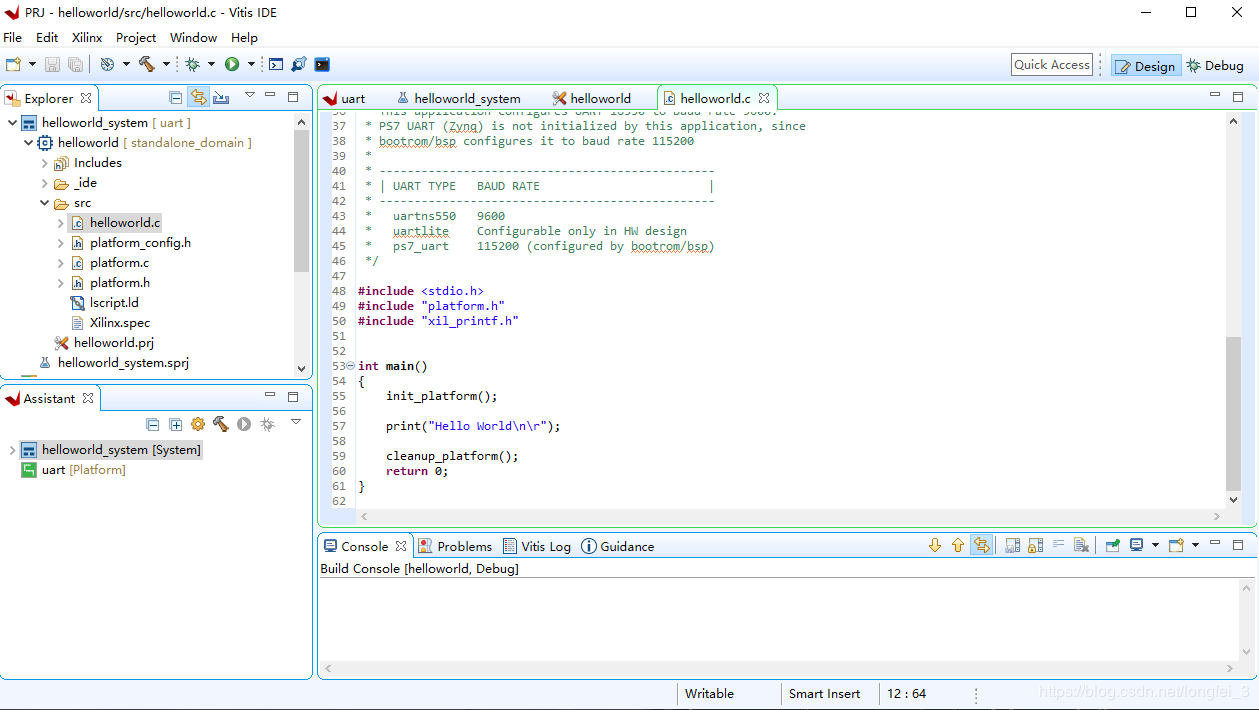

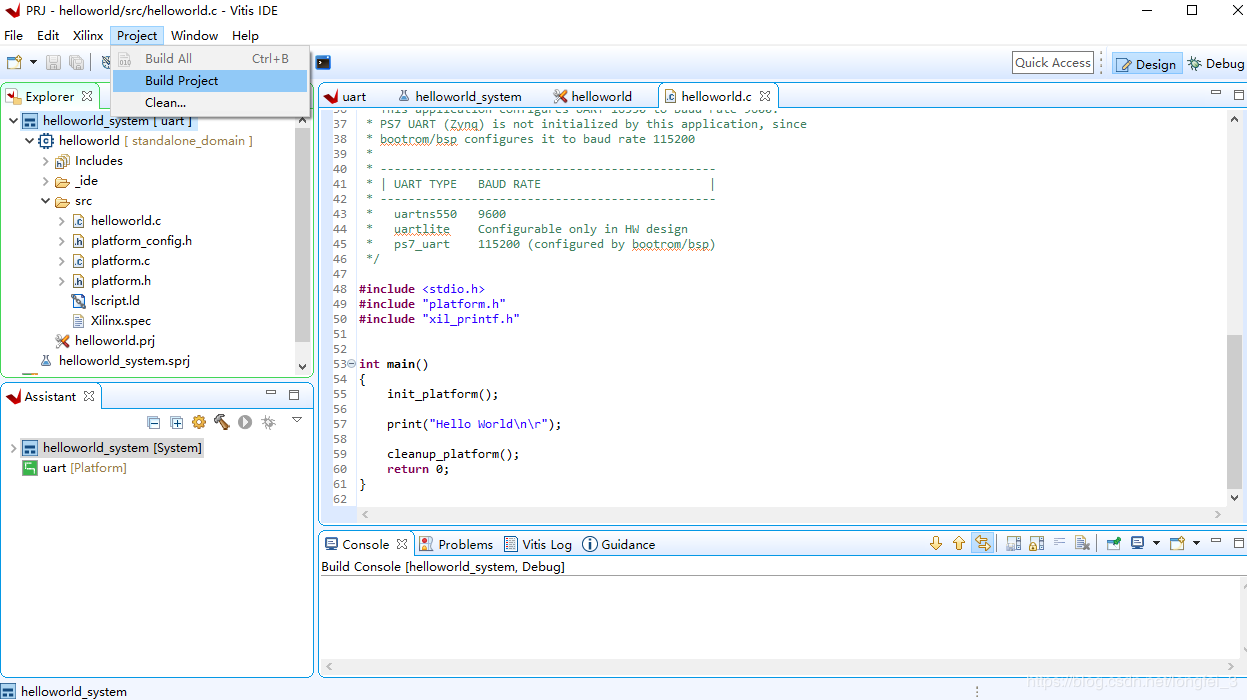

編譯helloworld工程

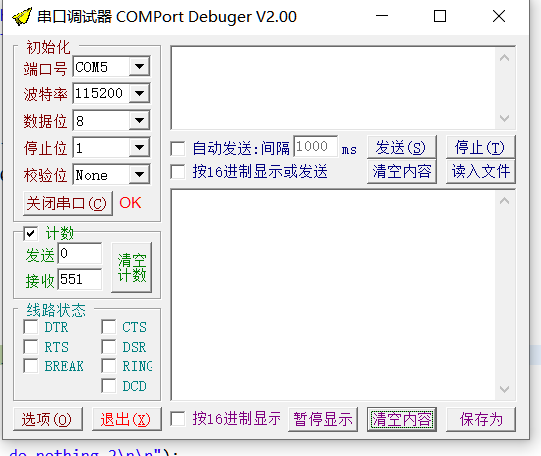

給板子接好上電,連接串口助手軟件,打開串口設置如下,com口根據實際而定。

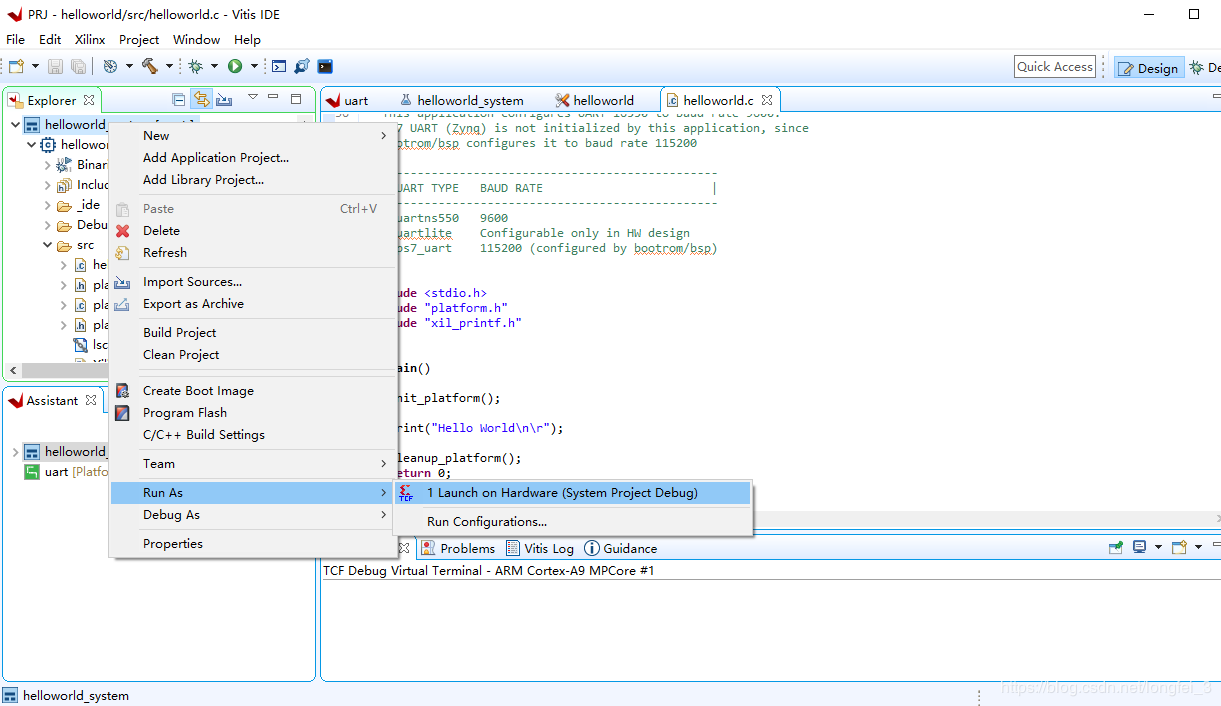

下載運行

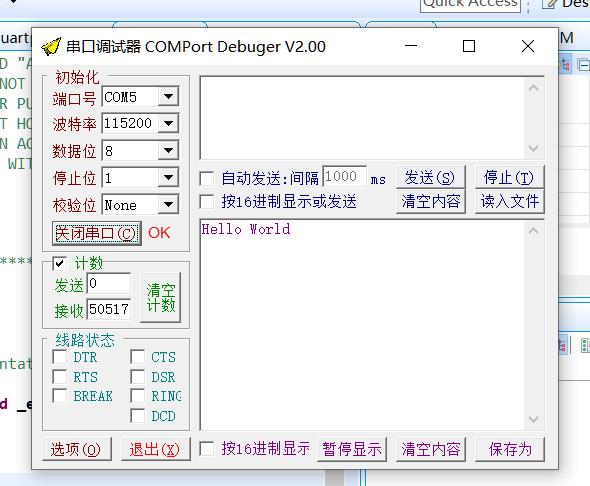

已經輸出了“hello world”

移植vivado2019.2之前版本的SOC工程:

1)Vivado部分:

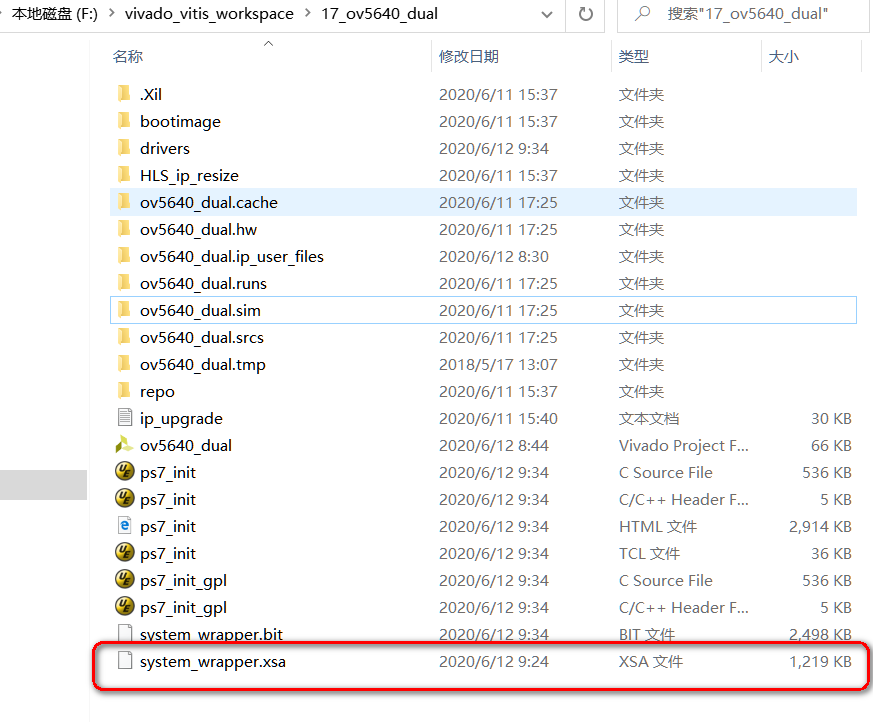

使用Vivado 2019.2打開之前版本的vivado工程項目 ,重新綜合生成bit流文件,如果工程中不設計PL部分則不需要生成bit文件。綜合通過之后導出硬件

File——Export——Export HardWare,導出成功后會發現在vivado工程路徑中會多出一個.XSA文件(個人理解與SDK導出的Hdf文件大同小異);

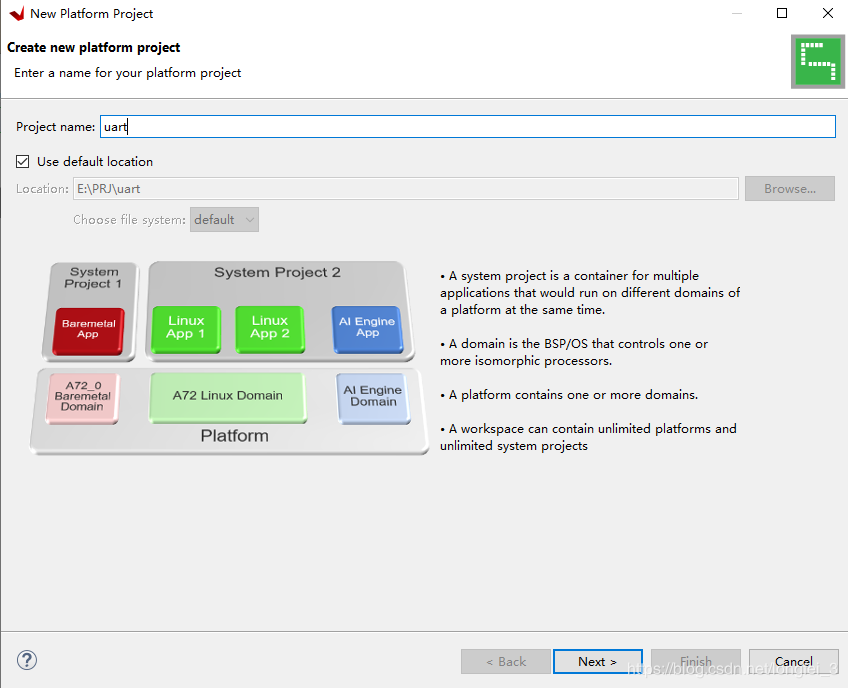

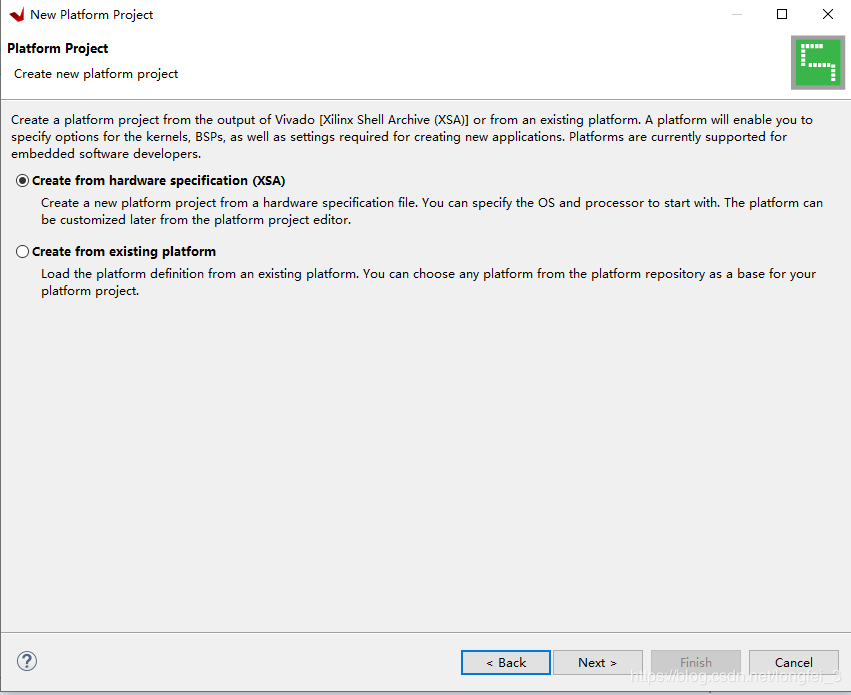

2)Vitis部分:

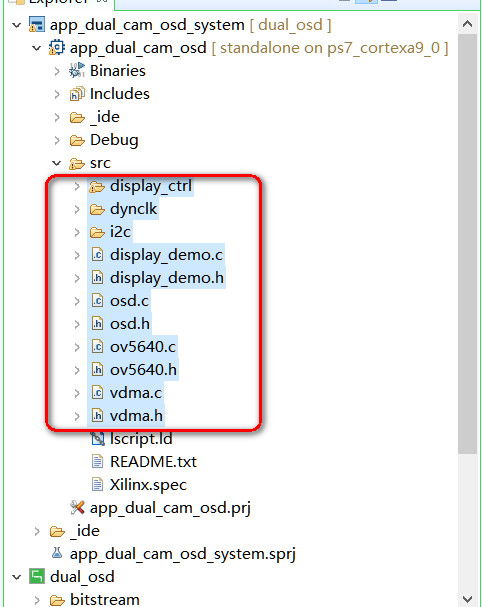

打開Vitis工具,創建一個Platform,設置項目名,添加vivado工程路徑中的.XSA文件。創建完Platform之后接下來創建一個Application項目,復制原工程SDK中的相應文件(.c和.h),粘貼到Vitis Apllication。

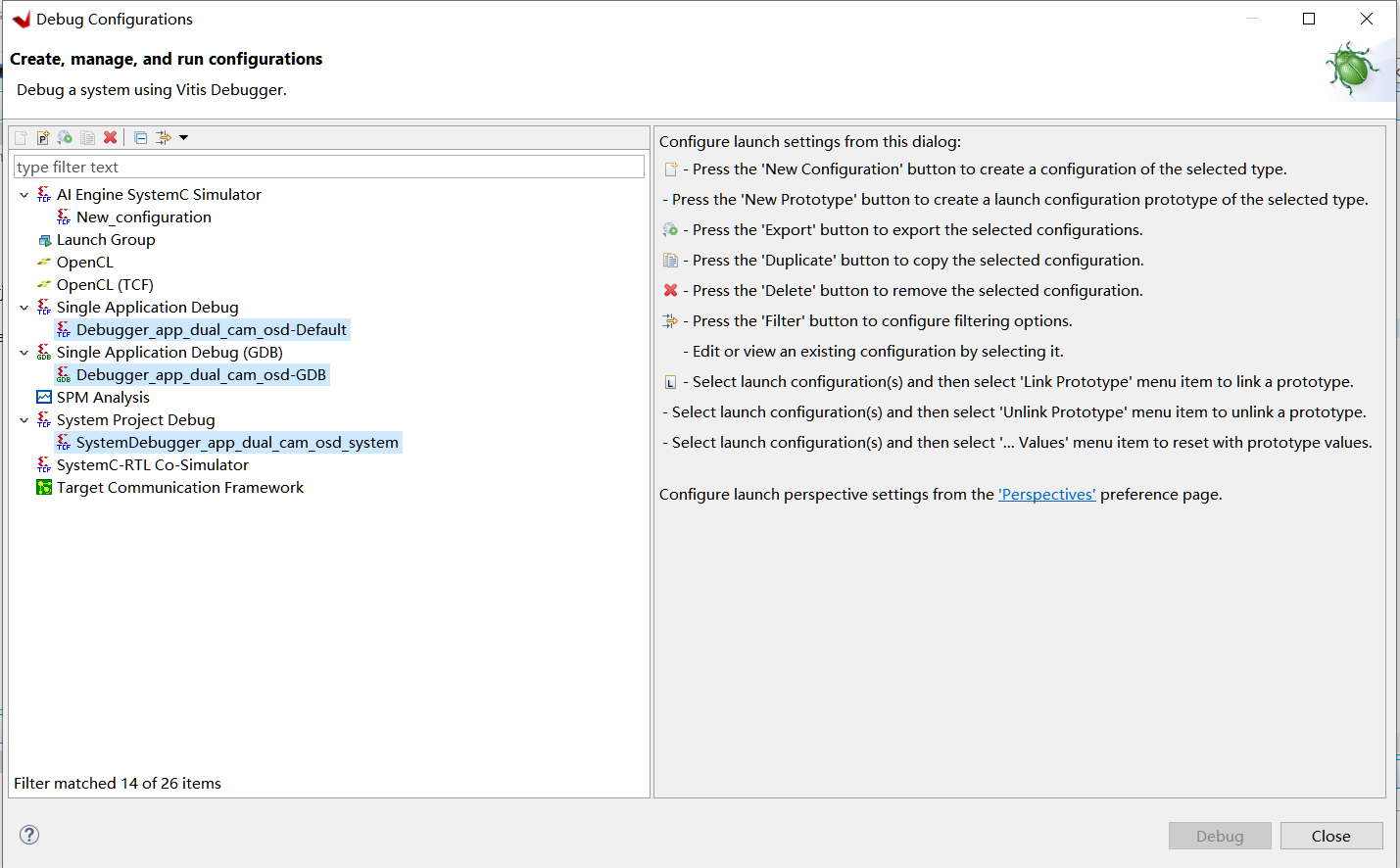

點擊編譯。右鍵app——DebugAs——DebugConfigurations

嘗試分別選擇上圖中3個Debug Configuration,運行均能正確實現原SDK工程的功能;

還不清楚這三個配置有什么區別。

總結:SDK工程的移植基本沒什么太大的變化,Vitis只是將SDK從Vivado中抽離出來單獨運行而已;

審核編輯 黃昊宇

-

SDK

+關注

關注

3文章

1067瀏覽量

47783 -

Vitis

+關注

關注

0文章

148瀏覽量

7851

發布評論請先 登錄

如何使用AMD Vitis HLS創建HLS IP

在任何平臺上使用PetaLinux的先決條件

基于HPM_SDK_ENV開發應用程序的升級處理

使用AMD Vitis進行嵌入式設計開發用戶指南

AMD Vitis Unified Software Platform 2024.2發布

U50的AMD Vivado Design Tool flow設置

在Jacinot6 SOC上集成VISION SDK和PSDK之間的虛擬DRM

Jacinto6 SoC上VISION SDK和PSDKLA之間的IVA-HD共享

評論