Image: IntelNMOS and PMOS devices usually sit side-by-side on chips. Intel has found a way to build them atop one another, compressing circuit sizes.

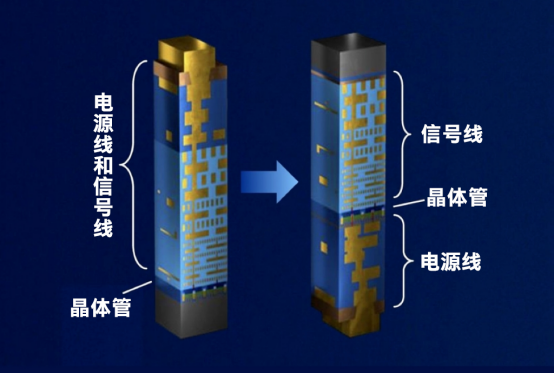

如今,幾乎每一個數字設備背后的邏輯電路都依賴于NMOS和PMOS兩種晶體管的配對。同樣的電壓信號下,其中一個開啟另一個就會關閉,把它們放在一起意味著只有其中之一發生變化時電力才會流動,這大大降低了功耗。幾十年來,這對電子對一直并排在一起。隨著對芯片能力要求的不斷提升,電路就要繼續縮小。近日,在IEEE International Electron Devices Meeting(IEDM)會議上,英特爾展示了一種不同的方法:將電子對堆疊起來,使一對電子對位于另一對電子對之上。該方案有效地將簡單CMOS電路的占地面積減少了一半,這意味著未來集成電路的晶體管密度可能翻倍。

該方案首先采用了被廣泛認可的下一代晶體管結構,根據參與人員的不同,這種結構被稱為各種各樣的納米片、納米帶、納米線或柵極全方位器件。晶體管的主要部分不再像今天那樣由垂直的硅翅片組成,納米片的溝道區域是由多個水平納米片相互疊放而成。

英特爾的工程師們用這些器件構建了最簡單的CMOS邏輯電路,即逆變器。它需要兩個晶體管、兩個電源連接、一個輸入互連和一個輸出。即使像今天這樣,晶體管并排放置,排列也非常緊湊。但通過堆疊晶體管和調整互連,逆變器的面積被削減了一半。

Photo: IntelCMOS devices have evolved from planar to FinFET. They will soon move to nanosheet. Shrinking circuits further will require stacking NMOS and PMOS devices.

英特爾制造堆疊納米片的配方被稱為自對準過程,因為它在本質上是同一步驟制造這兩個設備。這一點很重要,因為增加第二個步驟,比如,將它們構建在單獨的晶圓上,然后將晶圓連接在一起,可能會導致未對準,從而破壞任何潛在的電路。

從本質上講,這個過程的核心是對制造納米片狀晶體管步驟的修改。它從重復的硅和硅鍺層開始,將其雕刻成一個細長的鰭狀物,然后蝕刻掉硅鍺,留下一組懸浮的硅納米片。通常,所有的納米片都會形成一個晶體管。但是在這里,最上面的兩個納米片連接到摻磷硅上以形成NMOS器件,最下面的兩個納米片連接到摻硼硅鍺上以產生PMOS。

英特爾高級研究員兼組件研究總監Robert Chau表示,完整的“集成流程”當然更復雜,但英特爾研究人員努力使其盡可能簡單。集成流程不能太復雜,因為這將影響用堆疊式CMOS制造芯片的實用性。這是一個非常實際的流程。

“一旦我們掌握了竅門,下一步就是追求性能,”他說。這可能包括改進PMOS器件,而PMOS器件目前在驅動電流的能力上落后于NMOS器件。這個問題的答案很可能是晶體管通道引入“應變”,Chau說。其想法是扭曲硅晶體的晶格,使電荷載流子(本例中為空穴)更快地穿過。英特爾早在2002年就在其設備中引入了應變。在IEDM的另一項研究中,英特爾展示了一種在納米帶晶體管中同時產生壓縮應變和拉伸應變的方法。

Photo: IntelThe inverter consists of two transistors on top of one another with some parts and interconnects in common.

其他研究機構也在尋求堆疊納米片的設計,盡管它們有時被稱為互補場效應晶體管(CFETs)。比利時研究機構Imec率先提出了CFET概念,并在去年6月的IEEE VLSI研討會上報告了CFET的構建。然而,Imec元件并非完全由納米片晶體管制成。取而代之的是,底層是一個FinFET,頂層是一個納米片。臺灣的研究人員報道了一種CFET結構的生產,這種結構的PMOS和NMOS各有一個納米片。相比之下,英特爾的電路有一個兩納米片的NMO在一個三納米片的PMO上,這更接近于當堆疊成為必要時設備的樣子。

責任編輯:xj

原文標題:英特爾最新技術 堆疊納米晶體管可能成為摩爾定律的下一步

文章出處:【微信公眾號:IEEE電氣電子工程師學會】歡迎添加關注!文章轉載請注明出處。

-

英特爾

+關注

關注

61文章

9979瀏覽量

171923 -

摩爾定律

+關注

關注

4文章

634瀏覽量

79089 -

晶體管

+關注

關注

77文章

9702瀏覽量

138430

原文標題:英特爾最新技術 堆疊納米晶體管可能成為摩爾定律的下一步

文章出處:【微信號:IEEE_China,微信公眾號:IEEE電氣電子工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

英特爾展示互連微縮技術突破性進展

技術前沿:“環抱”晶體管與“三明治”布線

英特爾的最新技術:堆疊納米晶體管

英特爾的最新技術:堆疊納米晶體管

評論