上海潤欣科技股份有限公司創研社

一、什么是chipwatcher

在編程開發過程的調試階段,可以借助一些編譯環境集成的工具幫助我們更好地定位問題。當我們完成一份工程代碼但是觀測不到我們想要的結果時,我們需要進一步確認是哪部分的代碼出現了偏差導致得不到我們想要的結果。

對于MCU來說,我們可以借助JLINK仿真器來實現斷點測試,進而觀察每一步的數據變化,從而定位到問題所在;對于FPGA而言,想要觀察內部信號的變化,也有對應的工具可以使用。

這些工具,不同的芯片廠商根據自家的編譯環境集成了他們各自的工具,例如,XilinxISE的chipscope,alteraquartusII的SignalProbe等。本文中安路TD的chipwatcher也是用于觀測電路內部信號變化的工具,可以認為這是一款類似于邏輯分析儀的工具,只不過觀測的信號不是芯片引腳上面的信號,而是電路內部的信號。

當我們需要定位問題的時候,可以在工具中添加我們想要查看的信號,通過抓取波形來確認信號是否在根據我們的需求進行變化。

二、Chipwatcher使用流程

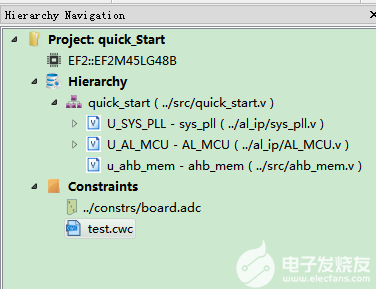

首先,一個FPGA工程常見的構成如下:

1.功能代碼文件:后綴為.v的文件,通俗地講就是我們自己寫的代碼。

2.例化的IP文件:通過編譯軟件來例化的IP的代碼,不同廠商例化后的IP文件名后綴有差異,安路的TD中直接將例化完畢后的.v文件加入工程即可。這類文件不是必須的,有用到需要的IP就加,沒有不加。

3.IO約束文件:用來定義整個工程的輸入輸出信號對應的具體芯片引腳是哪個。這類文件可以不加,不加的話編譯工具會自動分配IO口。

4.時鐘約束文件:即SDC文件。同IO約束文件,不加的話編譯器會自己約束,因此當工程較大時序較為復雜時通常需要我們自己約束。

以上四種文件通過編譯后一起生成的整個工程的bit文件燒錄進FPGA芯片后,假設代碼功能正常,則芯片開始工作。

假設功能不正常,當我們想要觀察電路內部信號的時候,我們還需要在工程中加入另一類文件,即第五類文件,然后將這五類文件統一打包成bit文件后下載進FPGA,此時才可以利用工具觀測和抓取到我們想看的信號。

這第五類文件,在TD中,即為Chipwatcher工具生成的.cwc文件。

下圖展示了一個加入.cwc文件后的工程目錄(該工程中未加入時序約束文件):

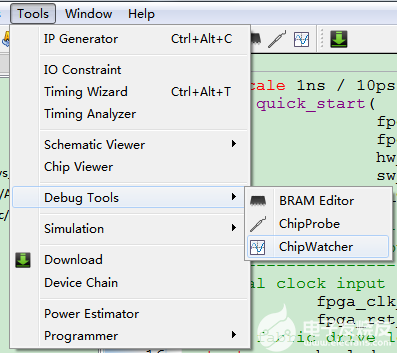

生成cwc文件的過程如下:

Tools->DebugTools->chipwatcher

進入到chipwatcher頁面:

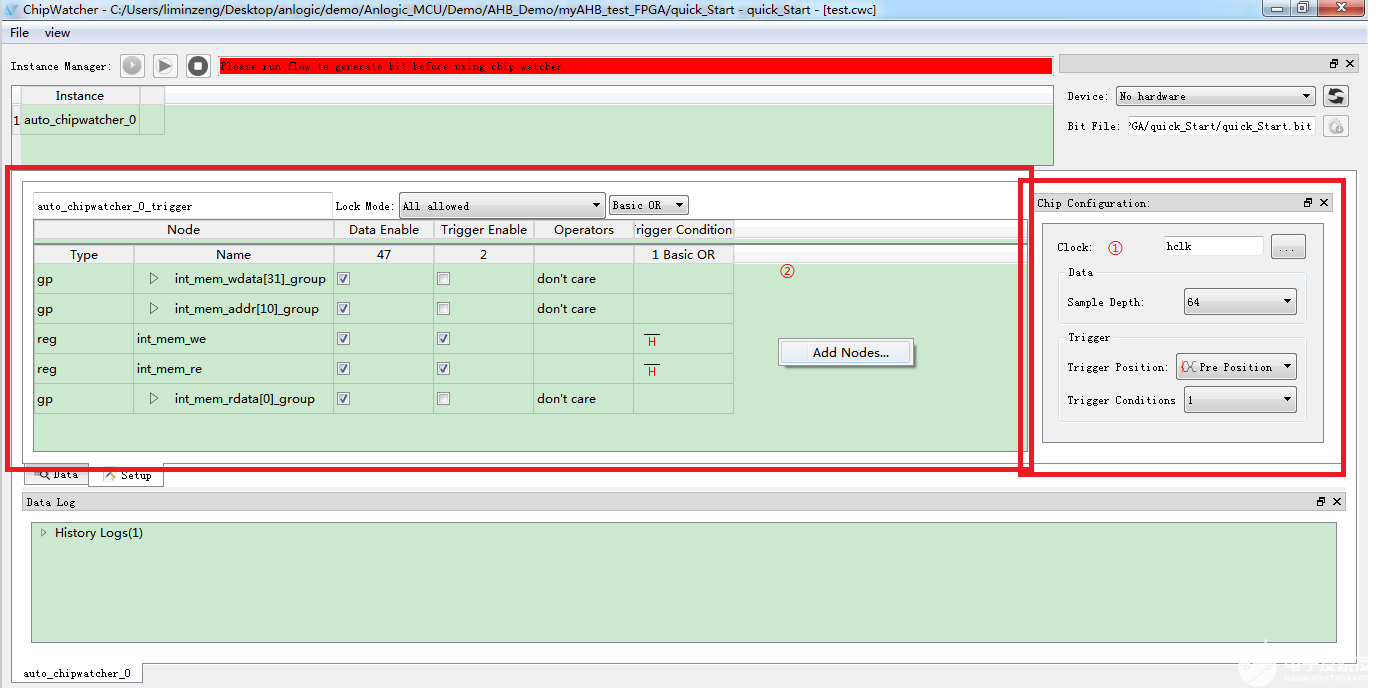

如上圖,①區是選擇采樣時鐘和采樣深度,采樣時鐘的選擇注意要選擇全局時鐘中頻率最高的時鐘,采樣深度越深(即數值越大),最終生成的bit文件所占用的芯片資源越多。

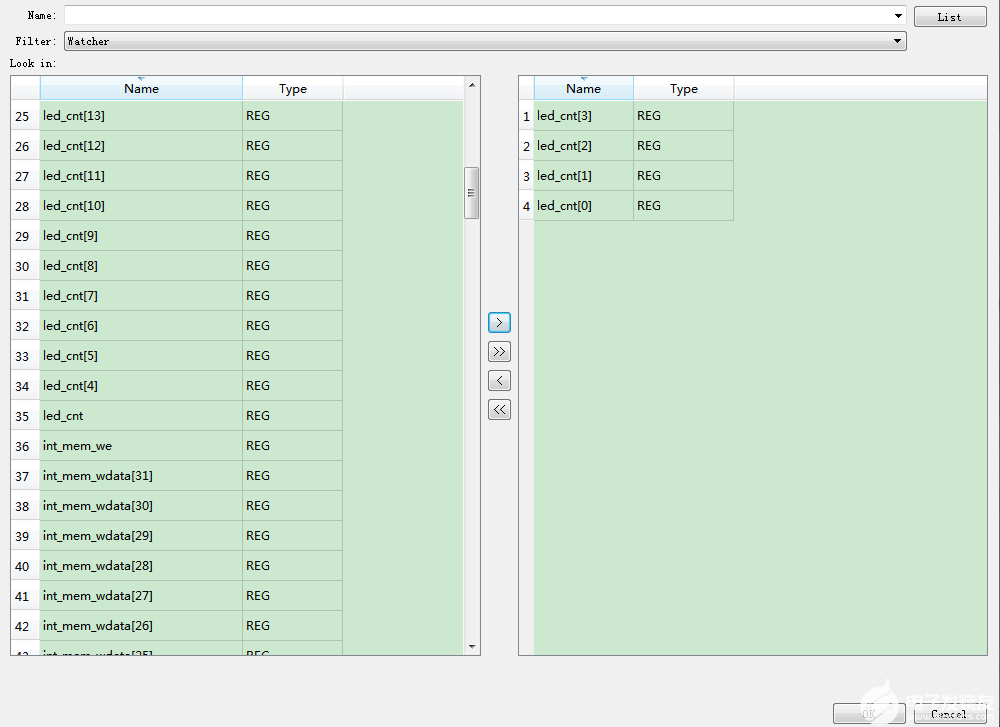

②區是添加想觀察的信號的區域,添加方法:在該區域右鍵后,選擇addnodes進入到信號選擇的頁面,如下:

如圖可以選擇想要觀察的信號至右側,全部選擇完畢后,點擊OK即可。

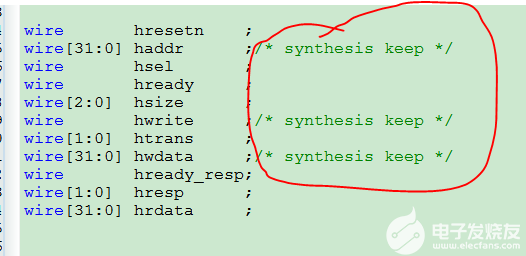

需要注意的是,有些信號會自動被編譯器優化,而在list中不被顯示,此時若是想觀測對應的信號,可以回到我們的代碼中加上如下關鍵詞即可:

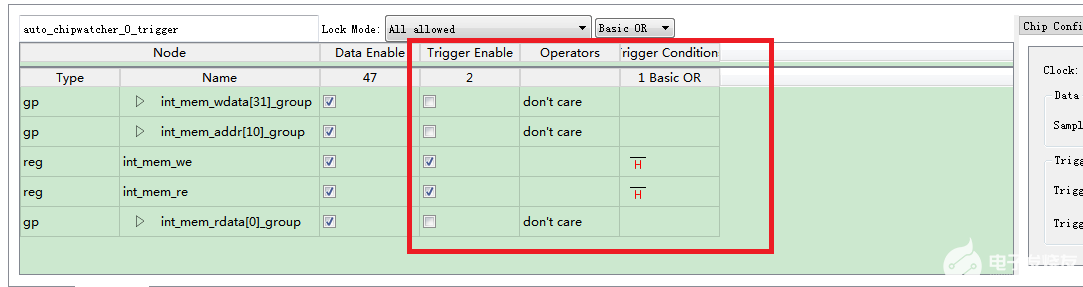

添加完想要觀察的信號后,設置觸發條件。

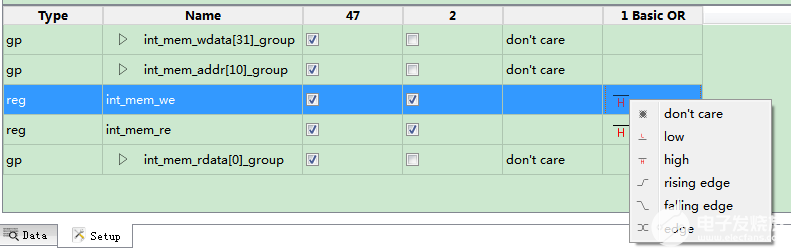

如圖,在triggerenable欄選擇觸發信號,在riggercondition欄選擇觸發條件(右鍵)

觸發條件共有以下幾種:

分別表示低電平觸發、高電平觸發、上升沿觸發、下降沿觸發和邊沿觸發。

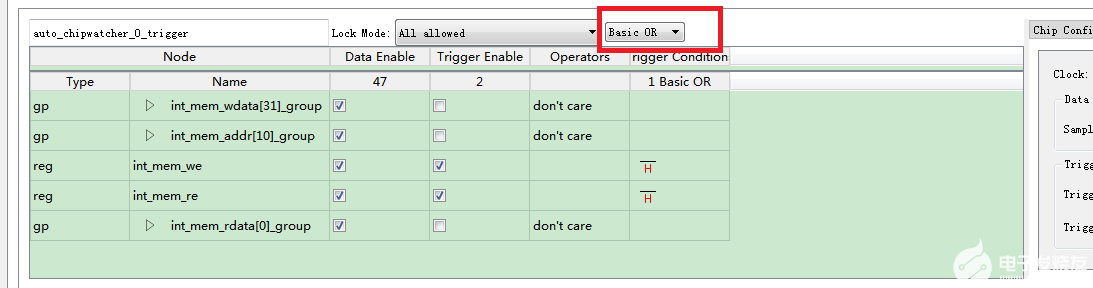

在如上圖處設置觸發信號之間的關系。圖中設置為或,即只要其中一個信號滿足條件即可。

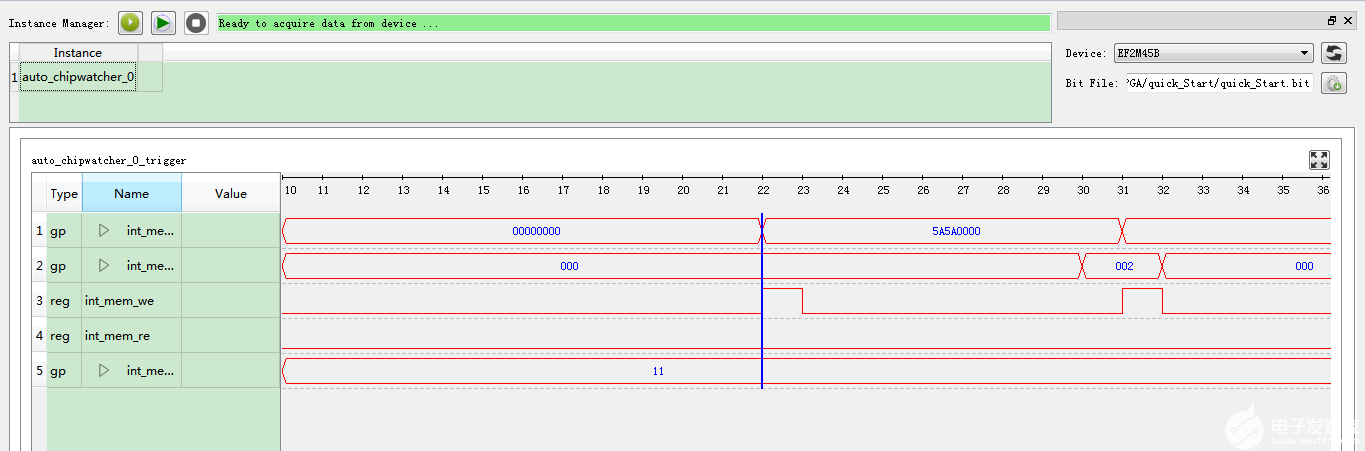

上圖中的整體觸發條件設置完畢后可敘述為:當int_mem_we信號或int_mem_re信號其中之一為高電平時,抓取當前int_mem_wdata[31:0]、int_mem_addr[10:0]、int_mem_rdata[31:0]、int_mem_we和int_mem_re的波形。

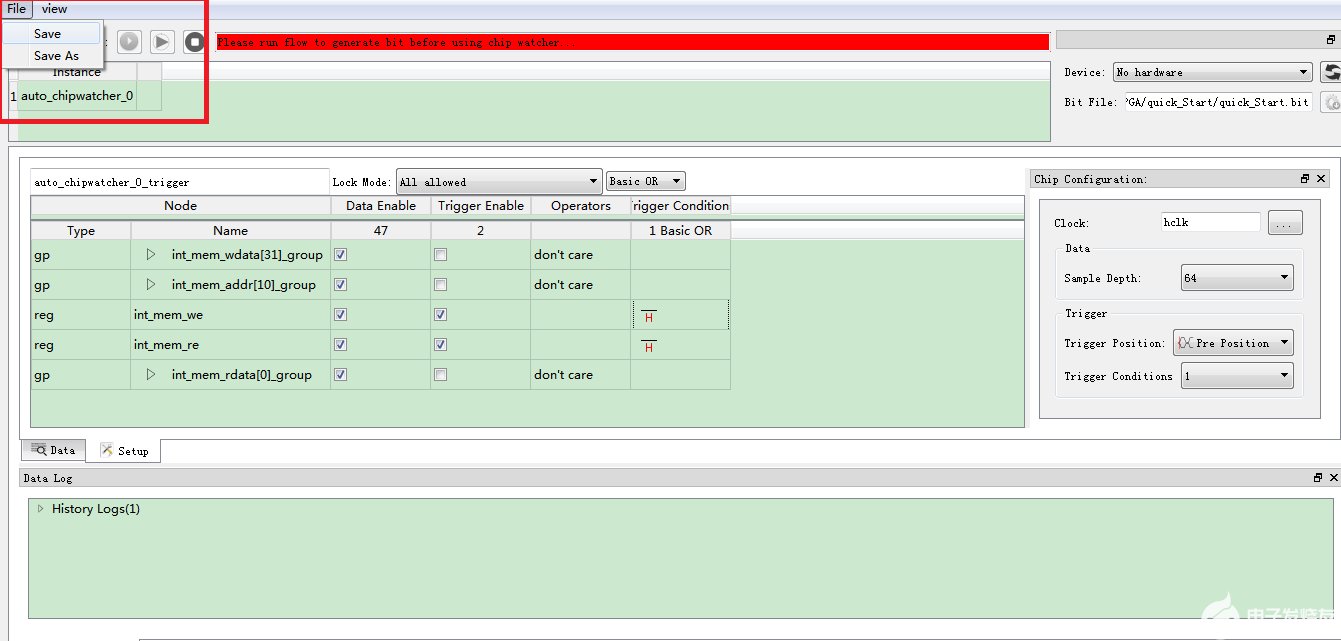

編輯完畢后即可保存文件。

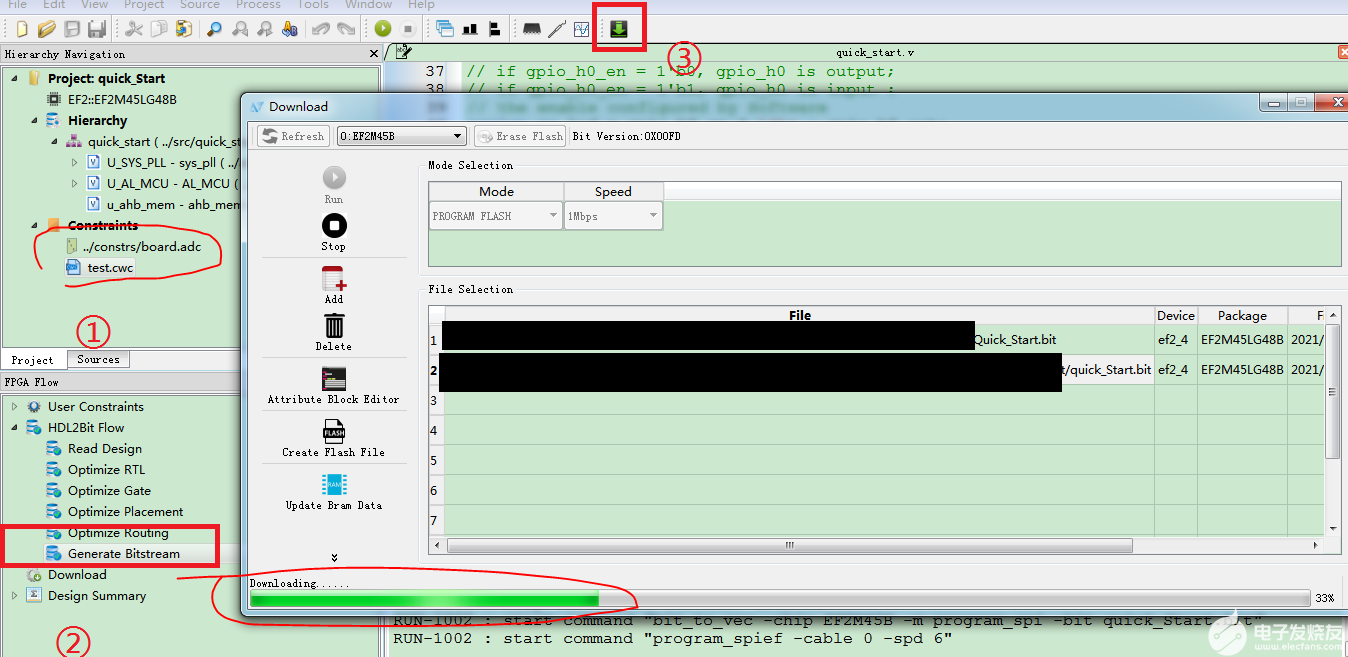

保存后生成對應的cwc文件,同時將文件加入工程,最后編譯下載至開發板。

(注釋:①為將生成的cwc文件加入工程,②為編譯工程,③為將bit文件下載至開發板)

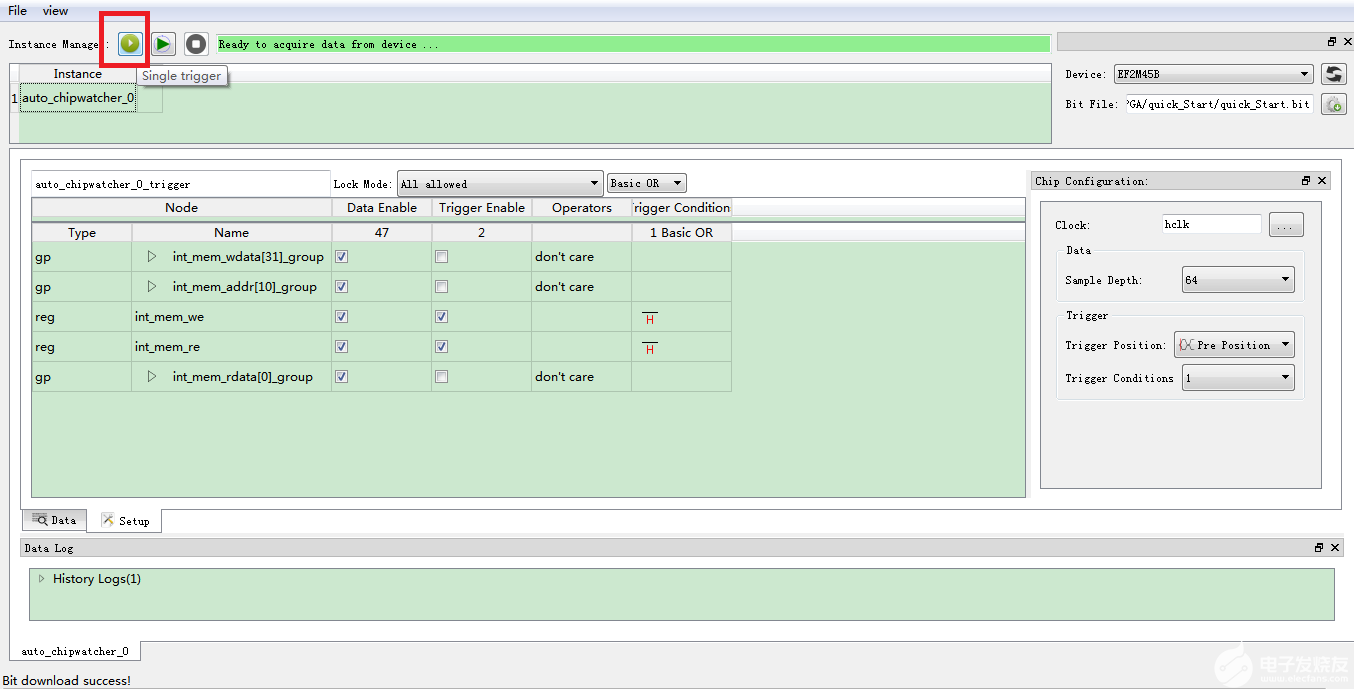

下載成功后,返回chipwatcher設置頁面,如下圖選擇singletrigger,即單次觸發。

當程序運行并滿足觸發條件時,chipwatcher會抓取到波形,如下:

三、FPGA調試與MCU調試的一些思路差異

Chipwatcher的調試過程大體如第二章中所示,但是很長一段時間,我并沒有在chipwatcher中觀察到任何波形,究其原因是沒有從MCU調試的思維轉變過來。

MCU的斷點調試,可以認為是一步一步執行的,沒有點擊下一步之前,程序會一直停留在當前位置(除非程序跑飛)。

而FPGA調試沒有這種機制,當bit文件下載至芯片后,程序是一直執行的,而點擊singletrigger后只不過是當滿足觸發條件時抓取當前波形而已。抓取完畢會顯示波形,程序卻依舊在繼續執行,不會停留在抓取完畢的那一刻。

當我使用chipwatcher觀察AHB協議傳輸時,沒有在數據線和地址線上面觀察到波形就是沒有意識到這點。在bit文件下載進芯片時傳輸就已經開始了(對比MCU的調試,通常MCU調試開始時,環境一般會在main函數起始自動設置斷點),假設傳輸在我開啟觸發按鍵前就已經完成,則傳輸線上就會一直觀察不到數據,觸發條件也會一直不成立。

因此,為了確保能夠順利抓取到傳輸的數據,需要在傳輸前設置相應的延時,保證當點擊singletrigger,chipwatcher開始根據設置的觸發條件抓取波形時,數據的傳輸還沒有開始。

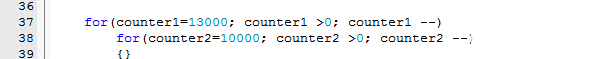

例程是MCU和FPGA根據AHB協議進行通信,因此后來我在MCU的工程中添加了一段延時:

確保留出足夠的時間來操作chipwatcher。

fqj

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614043 -

芯片

+關注

關注

459文章

52169瀏覽量

436104

發布評論請先 登錄

評論