19世紀,物理學家阿米西曾在義大利佛羅倫斯的實驗室里,把一滴液體加在標本上方,藉此改善顯微鏡的成像品質。100多年后,現在全球的半導體產業采納阿米西的創新技術,把晶片浸在淺薄的液體層中,制造出的電路線寬,可望媲美病毒大小。

20世紀40年代,約翰·巴丁和沃爾特·布拉頓在貝爾實驗室進行研發,研發晶體管的過程中將鎢絲電極移到金粒的旁邊,加上負電壓,而在金粒上加了正電壓,突然間,在輸出端出現了和輸入端變化相反的信號,他們將此器件命名為Transistor—晶體管,從此人類步入了飛速發展的電子時代。

半導體行業發展至今,離不開很多優秀的領路人,他們靠自己的智慧生產了一個個里程碑事件,他們依靠自己的力量在所熱愛的行業中發光發熱,用100%熱情與投入吸引著一代又一代的熱血青年加入半導體這個有意思的行業,今天我們一起盤點下集成電路發展史上的十大里程碑事件!

閃光時刻:1947年,美國貝爾實驗室的巴丁(J.Bardeen)、布拉頓(W. Brattain)、肖克萊(W.Shockley)三人發明了晶體管,獲得了1956年諾貝爾物理學獎。

發生背景: 1947年,約翰·巴丁和沃爾特·布拉頓在貝爾實驗室進行研發,研發晶體管的過程中將鎢絲電極移到金粒的旁邊,加上負電壓,而在金粒上加了正電壓,突然間,在輸出端出現了和輸入端變化相反的信號。初步測試的結果顯示:電壓放大倍數為2,上限頻率可達1萬Hz。此后的幾天,他們把試驗裝置進行了改進,測得的功率增益為大于18。他們將此器件命名為Transistor—晶體管。從此人類步入了飛速發展的電子時代。這是微電子技術發展歷程中第一個里程碑。

世界上第一顆鍺點接觸式晶體管誕生兩年之后,肖克利首次提出了晶體管理論。1953年,出現了鍺合金晶體管。1954年1月,貝爾實驗室的化學家MorrisTanenbaum利用摩根·斯巴克斯和戈登·蒂爾的生長界面成分變化技術,成功制造了第一個硅晶體管。

誕生意義: 晶體管徹底改變了電子領域,為更小,更便宜的收音機,計算器和計算機等鋪平了道路,第一個晶體管和MOSFET被列在電子領域的IEEE里程碑列表中,MOSFET是現代電子設備的基本組成部分,在現代電子系統中無處不在。在1960年至2018年期間,估計總共制造了13億個MOSFET(至少占所有晶體管的99.9%),使MOSFET成為歷史上制造最廣泛的器件。 大多數晶體管是由非常純的硅制成的,有些是由鍺制成的,但有時會使用某些其他半導體材料。在場效應晶體管中,晶體管可以僅具有一種電荷載流子,或者在雙極結型晶體管器件中可以具有兩種電荷載流子。與真空管相比,晶體管通常更小并且需要更少的功率來工作。某些真空管在非常高的工作頻率或高工作電壓下比晶體管具有優勢。多家制造商已將許多類型的晶體管制成標準化規格。

閃光時刻:

1958年,德州儀器的杰克·基爾比(Jack Kilby,被譽為“集成電路之父”)展示了第一款集成電路。他于2000年獲諾貝爾物理學獎。

誕生背景:

20世紀50年代,晶體管已得到了一定的發展。人們已經可以用硅做出分立的電阻、電容、二極管和三極管。彼時,在德州儀器的工程師Jack Kilby認為,既然能用單一材料硅制作這些分立器件,就能把這些器件做在一起。所以,1958年9月12日,JackKilby借助已有的幾種鍺器件,把金屬蒸鍍在鍺管的“發射極”和“基極”上,再用蝕刻技術做成接觸點,然后連接起來,制成了世界上第一塊集成電路。

盡管該裝置相當粗略,但是當Jack Kilby按下開關,示波器顯示屏上卻赫然出現了不間斷的正弦波形。試驗證明他的發明成功了,他徹底解決了此前一直懸而未決的問題。Jack Kilby在1976年發表的文章《集成電路的誕生》中寫道:“細想之后,我發現我們真正需要的其實就是半導體,具體來說,就是電阻器和電容器(無源元件)可以采用與有源元件(晶體管)相同的材料制造。我還意識到,既然所有元件都可以用同一塊材料制造,那么這些元件也可以先在同一塊材料上就地制造,再相互連接,最終形成完整的電路。

但是,Jack Kilby的發明是混合集成電路(Hybrid IC),而不是單片集成電路(monolithic IC)芯片,Kilby的IC具有外部電線連接,這使其難以批量生產。

在Jack Kilby的發明半年后,羅伯特·諾伊斯(Noyce)在仙童半導體公司發明了第一個真正的單片式IC芯片,是一種新的集成電路,比Kilby的實現更實用。諾伊斯的設計是由硅制成的,而Kilby的芯片是由鍺制成的。Noyce的單片IC將所有組件放在硅芯片上,并用銅線連接它們,Noyce的單片IC是使用平面工藝制造的,該工藝由他的同事Jean Hoerni在1959年初開發。現代IC芯片基于Noyce的單片IC,而不是Kilby的混合IC。

誕生意義:

集成電路的發明是應用需求和技術發展及創新思想共同作用的結果,開啟了以微電子技術為基礎的計算機和信息技術迅猛發展的新篇章。

閃光時刻:

平面加工工藝(光刻)的發明(1957年)和摩爾定律的提出(1965年)誕生背景:1957年,美國DOF實驗室首先將光刻技術引入到半導體技術中,為集成電路技術和產業按照摩爾定律發展奠定了基礎。仙童公司的Noyce 將光刻技術,巧妙利用起來,實現了精細晶體管和集成電路圖形結構,由此導致了平面工藝的誕生。 光刻技術是集成電路制造中利用光學-化學反應原理和化學、物理刻蝕方法,將電路圖形傳遞到單晶表面或介質層上,形成有效圖形窗口或功能圖形的工藝技術。從1960年開始,光刻法被用于在Si上制作大量的微小晶體管,當時分辨力為5μm,如今除可見光光刻之外,更出現了X射線和荷電粒子刻畫等更高分辨率方法,光刻是集成電路制造過程中的關鍵環節。目前國內自主研發芯片的困境便主要來源于高質量光刻設備的缺乏。

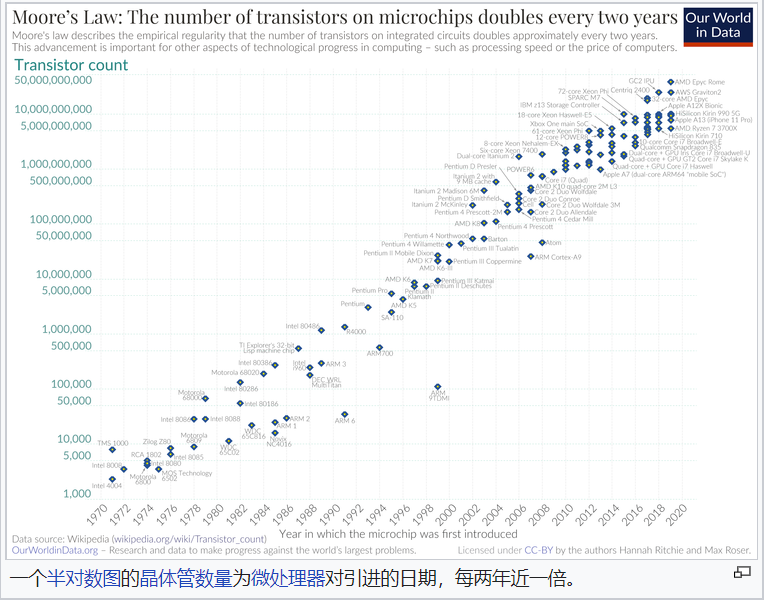

1959年7月,Noyce研究出一種二氧化硅的擴散技術和pn結的隔離技術,并創造性地在氧化膜上制作出精細的鋁膜連線,使元件和導線合成一體,從而為半導體集成電路的平面制作工藝、為工業大批量生產奠定了堅實的基礎。與Kilby在鍺晶片上研制集成電路不同,Noyce 直接盯住硅-地球上含量最豐富的元素之一,商業化價值更大,成本更低。自此大量的半導件被制造并商用,風險投資開始出現,半導體初創公司涌現,數量更多、功能更強、結構更復雜的集成電路被發明。 1965年4月19日,《電子學》雜志(Electronics Magazine)第114頁發表了摩爾(時任仙童半導體公司工程師)撰寫的文章〈讓集成電路填滿更多的組件〉,文中預言半導體芯片上集成的晶體管和電阻數量將每年增加一倍。 1975年,摩爾在IEEE國際電子組件大會上提交了一篇論文,根據當時的實際情況對摩爾定律進行了修正,把"每年增加一倍"改為"每兩年增加一倍",而普遍流行的說法是"每18個月增加一倍"。但1997年9月,摩爾在接受一次采訪時聲明,他從來沒有說過"每18個月增加一倍",而且SEMATECH路線圖跟隨24個月的周期。 大抵而言,若在相同面積的晶圓下生產同樣規格的IC,隨著制程技術的進步,每隔一年半,IC產出量就可增加一倍,換算為成本,即每隔一年半成本可降低五成,平均每年成本可降低三成多。就摩爾定律延伸,IC技術每隔一年半推進一個世代。

誕生意義:

光刻技術的發明,為集成電路技術和產業按照摩爾定律發展奠定了基礎,實現了精細晶體管和集成電路圖形結構,由此導致了平面工藝的誕生。

摩爾定律是簡單評估半導體技術進展的經驗法則,其重要的意義在于長期而言,IC制程技術是以一直線的方式向前推展,使得IC產品能持續降低成本,提升性能,增加功能。

閃光時刻:

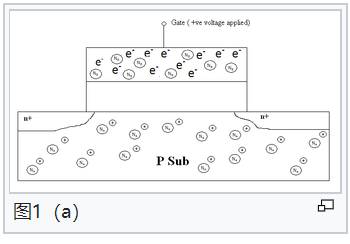

1960年,MOSFET器件發明;1963年,COMS(互補金屬氧化物半導體)技術被提出;1966年,美國RCA公司研制出CMOS集成電路。誕生背景: 1955年,Carl Froschand Lincoln Derrick偶然覆蓋的硅的表面的晶片有一層二氧化硅,氧化層阻止了某些摻雜劑進入硅晶片,同時允許其他摻雜劑,從而發現了半導體表面氧化的鈍化作用。他們的進一步工作證明了如何在氧化物層中蝕刻小開口以將摻雜劑擴散到硅晶片的選定區域中。1957年,他們發表了一篇研究論文,他們開發的技術被稱為氧化物擴散掩膜,稍后將在制造中使用MOSFET器件。

貝爾實驗室的Mohamed M. Atalla于1950年代后期處理表面狀態問題。他認為,在干凈的硅晶片上生長非常薄的高質量熱生長的SiO2,將中和表面狀態,足以制成實用的場效應晶體管。 1960年,貝爾實驗室的Kahng和Atalla制備出了第一支MOS場效應晶體管(MOSFET);1963年,任職于仙童公司白程師F.M.Wanlass和C.T.Sah首次提出CMOS技術,由低功來高效率的CMOS替代了傳統的TTL(Transistor-to-Transi Logic,晶體管-晶體管邏輯)電路。如今,95%以上的集成電芯片都是基于CMOS工藝,可以說沒有CMOS,就沒有之后整集成電路的發展。 早期的CMOS元件雖然功耗比常見的TTL電路要低,但為工作速度較慢,所以大多數應用CMOS的場合都和降低功耗、延長電池使用時間有關,例如電子表。不過經過長期的研究與良,如今的CMOS元件無論在可集成的面積、工作速度、功耗,還是在制造的成本上看,都比當時另外一種主流的半導體制程BJT (Bipolar Junction Transistor,雙極結型晶體管)有優勢,很多在BJT無法實現或是成本太高的設計,利用CMOS皆可迎刃而解。誕生意義:

MOSFET的發展引發了電子技術領域的一場革命,稱為MOS革命或MOSFET革命,為早期半導體行業的技術和經濟增長提供了動力。 從1960年代后期開始,MOSFET的影響在商業上變得很重要。這導致了電子行業的一場革命,此后幾乎以各種方式影響了日常生活。MOSFET的發明被認為是現代電子技術的誕生,并且是微型計算機革命的核心。 CMOS集成電路因為具有功耗低源電人阻抗高、噪聲容限高、電源電壓范圍寬、輸出電壓幅度與電源電壓接近、對容限遲和躍遷時間等優點所以發展極為迅速 CMOS集成電路的問世開創了微功耗電子學的先河,為如今的大規模集成電路發展奠定了堅實基礎,具有里程碑意義。

閃光時刻:

1967年,DRAM(動態隨機存取存儲器)發明;1971年,全球第一款微處理器4004由Intel公司推出。誕生背景:1966年,Dennard提除了DRAM的想法,當時他的MOS項目非常有希望,但相當復雜,因為每一比特的信息需要使用六個晶體。于是,他利用業余時間研究自己的新想法,并且最終找到了通過存取晶體管將電荷寫入電容,然后通過同一個晶體管讀出的替代方法。1967年,Dennard 和IBM公司針對他的“單晶體管動態隨機存取存儲器”(DRAM)申請了專利。在一塊芯片上集成的元件數超過10萬個,或門電路數超過萬門的集成電路,稱為超大規模集成電路。1988年,16M DRAM問世,在1c㎡大小的硅片上集成有3500萬個晶體管,標志著進入超大規模集成電路(VLSI)階段。超大規模集成電路研制成功,是微電子技術的一次飛躍,大大推動了電子技術的進步從而帶動了軍事技術和民用技術的發展。

20世紀60年代隨著集成電路的發明和應用,一場制造輕便桌面計算器的競賽揭開了帷幕。那時,半導體產業的研究者已普遍意識到,用新的MOS技術來創建一個包含多種功能的芯片在理論上是可行的。短短幾年后,Intel公司便于1971年成功地研制出實際上第一款微處理器4004,由2300個晶體管構成了一款包括運算器、控制器在內的可編程序運算芯片。使得微處理器成為繼晶體管、集成電路后的又一重大發明。可以說,中央處理單元的發明與應用改變了整個世界的科技發展,掀起了一場新的技術革命。

誕生意義:DRAM的簡單性、低成本和低功耗與第一款低成本微處理器相結合開啟了小型個人電腦的時代。Intel 4004微處理器是世界上第一款商用計算機微處理器,它是“一件劃時代的作品”。它在單片內集成了2250個晶體管,晶體管之間的距離是10μm,能夠處理4bit的數據,每秒運算6萬次,運行的頻率為108kHz,成本不到100美元。Intel公司的首席執行官戈登·摩爾將4004稱為“人類歷史上最具革新性的產品之一”。

閃光時刻:

銅互連技術的發明

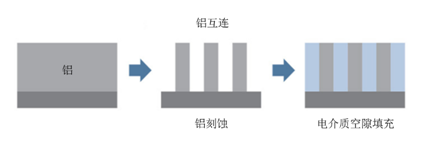

誕生背景: 集成電路最初用鋁作為導體,二氧化硅作為絕緣體(電介質),構建一個互連層,來將多個器件連接在一起。整個互連的過程由鋁沉積在晶圓表面開始,隨后通過選擇性刻蝕形成布線圖案,沉積氧化物絕緣體,并利用化學機械平坦化(CMP)工藝將粗糙的表面變得平坦。

20世紀 80 年代后期,隨著器件特征尺寸繼續縮小,越來越薄的鋁線無法實現所需的速度和電性能,因此需要一種性能更優的導電材料,以適應繼續縮小的器件尺寸,同時保持芯片制造商預期的成本效益。多年來,該行業的發展大致遵循摩爾定律,即晶體管密度每 18 個月翻一倍。然而,由于鋁互連的電性能局限性,芯片的微縮將無法繼續進行,業內人士便開始尋找可替代材料。 人們首先想到的是銅,它具有更低的電阻率,且可實現更快的器件速度。此外,銅并不像鋁那樣容易發生電遷移,所以具有更高的可靠性。電遷移中,電流推動導線中的金屬原子,會導致電阻增加,最終造成電路故障。然而,使用等離子(帶電氣體)工藝刻蝕銅的方法并不可行。由于銅不容易形成揮發性化合物,因此,通過干法刻蝕并不能輕松地將其從晶片表面除去。芯片若要實現進一步微縮,亟需一種合適的新導體,或截然不同的圖形化工藝,或兩者的組合。 業內一直在研究其它導體材料,相較之下,銅的電氣特性使其成為最佳選擇。工程師開始考慮使用鑲嵌工藝,即借鑒大馬士革的珠寶行業,先在基底金屬上刻蝕圖案,再將貴金屬嵌入圖案之中。該工藝繞過刻蝕銅的難題,先沉積和刻蝕電介質材料,形成由溝槽和孔洞組成的圖案(即鑲嵌金屬的模具)。然后,僅將金屬填充到圖案中,而不是在整個晶圓表面沉積金屬膜。

閃光時刻:

浸入式光刻技術的發明

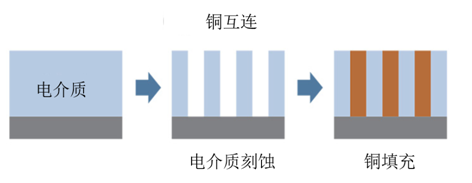

誕生背景: 在浸入式光刻技術之前,繼436nm、365nm、248nm之后,采用的是193nm干式光刻技術,但在65 納米技術節點上遇到了困難,試驗了很多技術(如157nm干式光刻技術等)但都無法很好的突破這一難題。等到2002年底浸入式技術迅速成為光刻技術中的新寵,而此前業界并沒有認為浸入式技術有如此大的功效。此技術在原來的193nm干式光刻技術平臺之上,因為此種技術的原理清晰及配合現有的光刻技術變動不大,獲得了人們的極大贊賞。 浸沒式光刻技術需要在光刻機投影物鏡最后一個透鏡的下表面與硅片上的光刻膠之間充滿高折射率的液體。圖 l 為傳統光刻和浸沒式光刻的對比示意圖。投影物鏡的數值孔徑:NA=nsinθ

圖1 傳統光刻和浸沒式光刻示意圖 其中,n為投影物鏡與硅片之間介質的折射率,θ為光線最大入射角。在最大入射角相同的情況下,浸沒式光刻系統的數值孔徑比傳統光刻系統增大了n倍。而從傅里葉光學的角度, 數值孔徑扮演著空間頻率低通濾波器閾值的角色。注人高折射率的浸沒液體可以使更高空間頻率的光波人射到光刻膠上, 因此成像分辨率得以提高。 如今,EUV技術慢慢開始替代了一部分的浸沒式光刻,EUV技術以波長為10-14納米的極紫外光作為光源的光刻技術。具體為采用波長為13.4nm 的紫外線。極紫外線就是指需要通過通電激發紫外線管的K極然后放射出紫外線。EUV光刻采用波長為10-14納米的極紫外光作為光源,可使曝光波長一下子降到13.5nm,它能夠把光刻技術擴展到32nm以下的特征尺寸。 EUV光刻所能提供的高分辨率已經被實驗所證實。光刻機供應商已經分別實現了20nm和14nm節點的SRAM的曝光,并與193i曝光的結果做了對比。顯然,即使是使用研發機臺,EUV曝光的分辨率也遠好于193i。14nm節點圖形的曝光聚焦深度能到達250nm以上。

閃光時刻:多晶硅柵/high-k基MOS管和金屬柵/high-k基MOS管發明誕生背景: 由于Si-SiO2良好的界面特性以及SiO2薄膜的優異性能,純硅基MOS器件具有優異的界面性能和熱穩定性,并且致密的SiO2薄膜能夠阻止更多的氧氣和水分子進入柵介質層。此外,多晶硅與襯底硅的功函數差值較小,有利于降低器件的閾值電壓,從而提高器件開關速度。 然而,當特征長度降至65nm節點時,就會出現短溝道效應,顯著增大器件的功耗。為了控制短溝道效應,更小尺寸器件要求進一步提高柵電極電容。這能夠通過不斷減小柵氧厚度而實現,但隨之而來的是柵電極漏電流的提升。當二氧化硅作為柵電極絕緣層且氧化層厚度低于5.0nm時,漏電流就變得無法忍受了。

解決上述問題的方法就是使用高介電常數絕緣材料取代二氧化硅,采用這種材料可以在不增加電學厚度的前提下允許增加絕緣層厚度,進而能夠降低漏電流。經過反復試驗,基于鉿(Hf)的high-k絕緣材料取代二氧化硅作為柵電極的絕緣層。high-k介質的引入能在一定程度上緩解SiO2厚度減小引起的隧穿效應,進而減小泄漏電流,降低器件功耗。然而,當特征長度降至45nm節點時,多晶硅/high-k基MOS器件出現嚴重的多晶硅耗盡效應。多晶硅的高電阻率也嚴重影響了MOS器件的高頻特性。 此外,在早期的高介電常數材料的研發中就已經發現了high-k介質與多晶硅柵電極不匹配的問題。這一問題不僅會導致在高介電材料與多晶硅材料的界面上產生大量的缺陷,還會降低器件的電子遷移率。后一問題是由于電荷散射而引起的,這也是將這兩種材料結合在一起的固有表現。因此,金屬柵替代了多晶硅柵,被用于納米晶體管和先進晶體管結構。 金屬柵極是為了和high-k柵介質材料兼容而提出的。一方面,金屬作為良導體,不會產生耗盡層,有效地消除了多晶硅耗盡效應,同時也使金屬柵極無需通過摻雜提高導電性:另一方面,與多晶硅柵極相比,金屬柵極材料自由電子濃度遠大于反型層載流子濃度,使得金屬柵極能夠有效抑制high-k介質低能光學聲子與溝道載流子耦合,從而降低聲子散射,提高載流子遷移率。

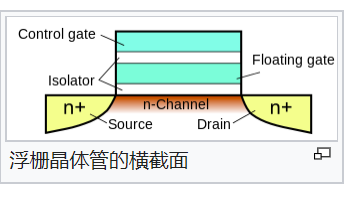

閃光時刻:浮柵(Floating Gate)存儲器件發明誕生背景: 伴隨著整個半導體微電子產業的發展,存儲器也在以驚人的速度發展。以動態存儲器(DRAM)為例,每個功能元件的尺寸不斷減小,價格不斷下降,每個存儲單元工作所需的電子數目也越來越少。DRAM中的電容如果不能提供足夠多的電子給放大器,整個存儲器將被噪聲所淹沒,將不能保證信息存儲的可靠性。 當每個存儲單元的電子數目因集成度的提高變得越來越小時,存儲器中的MOS場效應晶體管將逐漸變得不定,而使整個存儲器的可靠性難以得到保證。 單電子存儲器的出現使存儲器繼續維持高速發展成為可能,目前已經實現室溫下的對背景電荷不敏感的單電子存儲器,因此實際應用的前景非常光明。從目前設計制備出來的單電子存儲器來看,它們的工作通常只需控制幾百個、幾十個甚至幾個電子就可以實現數據的存儲,因此它們的功耗非常低。

單電子晶體管是單電子存儲器的最主要的組成部分,單電子晶體管的特性在一定程度上決定了基于它制備的存儲器的性能,所以它的發展在很大程度上制約單電子存儲器的發展。在單電子存儲器中,使用對電荷超敏感的庫侖計對存儲單元中的電荷進行探測,來確定存儲單元的狀態。這些超敏感的庫侖計是將單電子晶體管和浮柵與被測的對象集成在一起,利用單電子晶體管對柵極電荷的敏感性來實現電荷的探測。而在另一些單電子存儲器中則是利用單電子晶體管中的庫侖阻塞現象,通過控制源、漏和柵極電壓來實現對源(或漏)上電子數目的精確控制,然后利用其他的放大部分(如MOSFET等)來實現數據的存儲。其中的單電子晶體管有些具有單個量子點結構,而有些則具有納米線結構。 浮柵量子點的存儲器是依據量子點的庫侖阻塞原理設計和制備的。依據Fowler—Nordheim隧穿原理,利用柵極來控制電子進出量子點,使量子點在庫侖阻塞區域的邊界達到兩個穩定的電壓值,此時系統的兩個穩定態對應著量子點兩個不同的勢能。通過電容耦合一個單電子晶體管(庫侖計)或者利用MOS場效應管來對量子點的狀態進行探測,便可以確定出系統的狀態。為了實現單電子器件的高密度存儲,就必須精確控制量子點的形狀和位置,因此這些器件的制備通常具有一定的難度,但是利用掃描探針技術可以制備出常溫下就可以正常工作的單電子存儲器;如果使用納米硅顆粒來制備器件,它們也可以在室溫下工作,并且不受背景電荷漲落的影響。

FGMOS可以通過將標準MOSFET柵極絕緣來制造。通過絕緣使得其柵極與外界沒有電阻連接;然后在浮柵上方沉積多個次級柵極或輸入電極,并與其電隔離。由于浮柵完全被高電阻材料包圍,輸入電極和浮柵之間僅有電容耦合,因此,就其直流工作點而言,浮柵是浮動節點。 在需要修改浮柵電荷量的應用,每個FGMOS會添加一對額外的小晶體管,以實現注入和隧穿操作。每個晶體管的柵極連接在一起;隧穿晶體管的源極、漏極和體端子相互連接,形成電容隧穿結構。注入晶體管以正常方式連接,并施加特定電壓以產生熱載流子,然后通過電場將熱載流子注入浮柵。 在純電容應用中,FGMOS晶體管既可以制造成N型,也可以做成P型。對于電荷改變的應用,隧穿晶體管(以及FGMOS)需要嵌入到阱中,因此該技術決定了可以使用的FGMOS的類型。

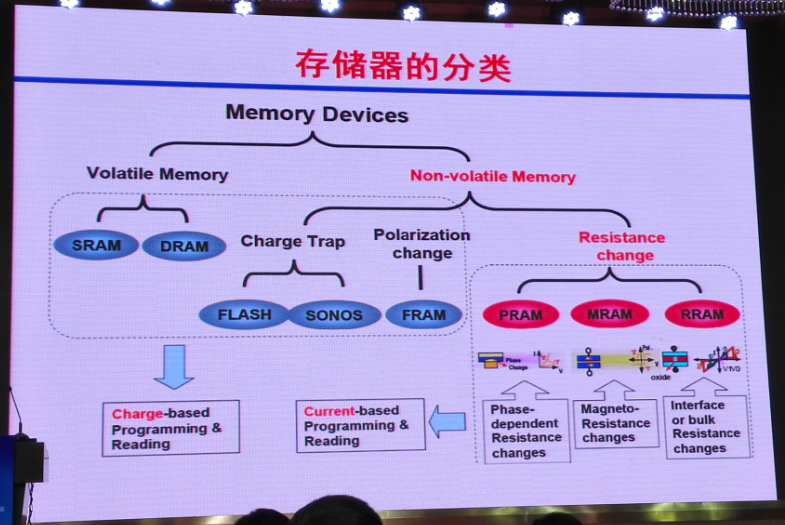

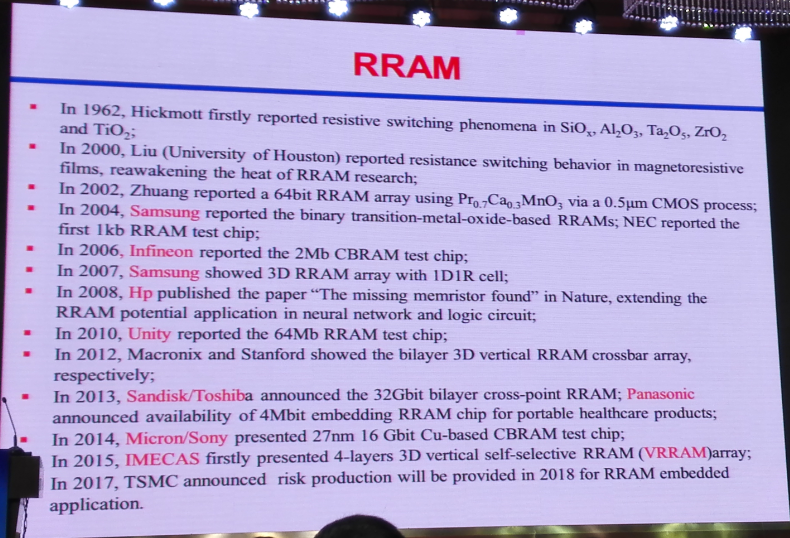

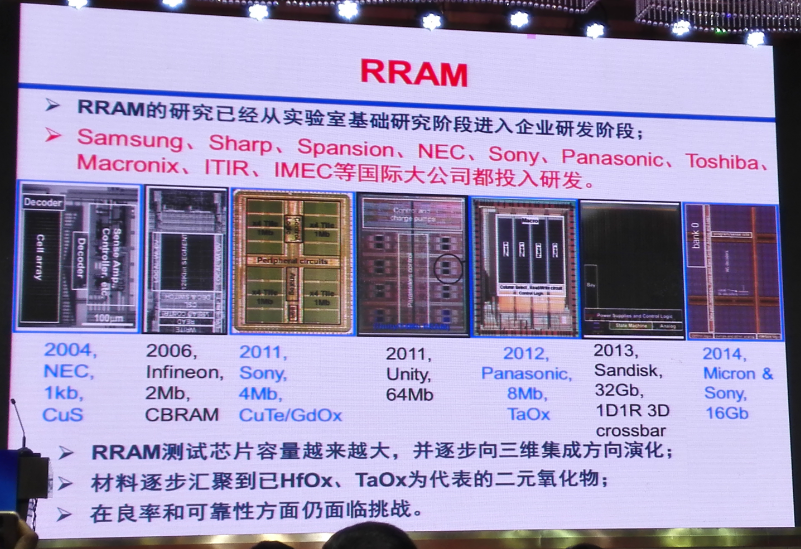

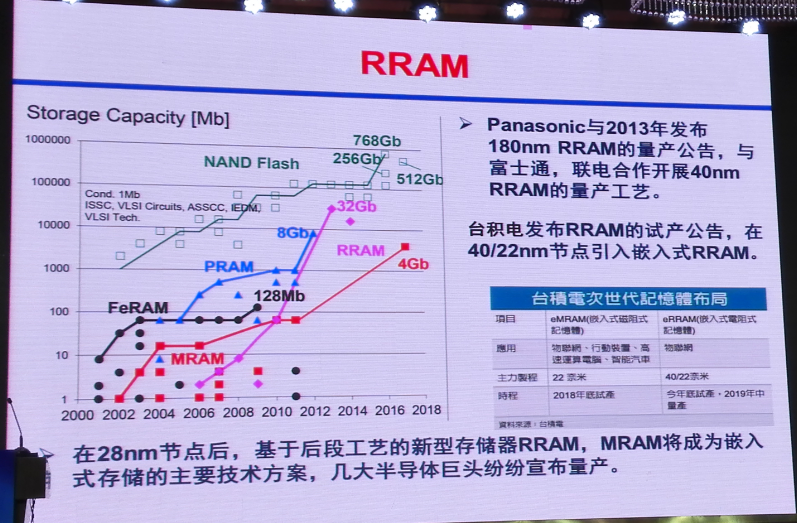

閃光時刻:新型RRAM存儲器件發明誕生背景: 存儲器分為易失性和非易失性兩大類。當今,易失性存儲器最重要的兩類是SRAM和DRAM。非易失性存儲器的種類很多,市場份額最大的是閃存(FLASH),其他的還有SONOS、鐵電存儲器(FRAM)、相變存儲器(PRAM)、磁存儲器(MRAM)和阻變存儲器(RRAM)等。此外,SRAM、DRAM、FLASH、SONOS和FRAM這五種是基于電荷的存儲器,這類存儲器本質上是通過電容的充放電來實現的。而PRAM、MRAM和RRAM則是基于電阻的轉變來實現的。

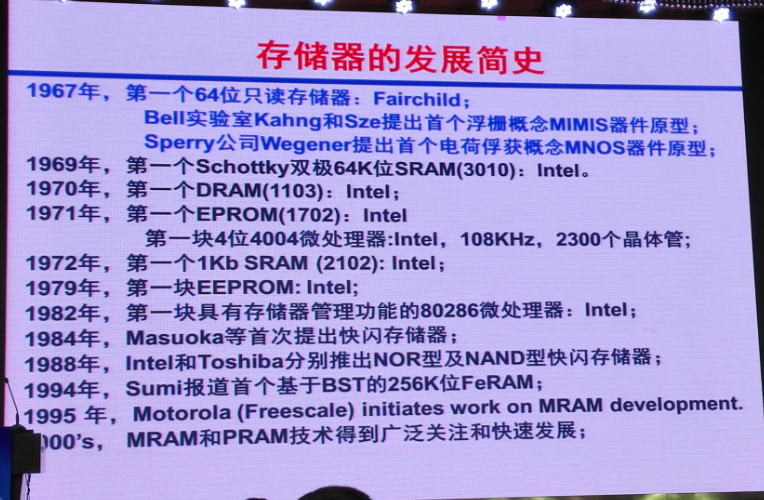

存儲器距今已發明了50周年。1967年,第一個64位只讀存儲器由仙童公司發明。閃存也是在這一年由Bell實驗室所提出。Intel在存儲器發展的早期做出了很多貢獻,比如第一個SRAM和第一個EEPROM都由該公司推出。閃存之所以是在90年代才大規模應用,是因為直到1988年,Intel和東芝才分別提出了NOR和NAND兩種類型的閃存集成架構。

RRAM相比MRAM和PRAM,研究要稍晚。雖然這個現象早在1962年就被報道了,但沒有引起學術界和工業界的關注。直到2000年,美國休斯敦大學在APL上發表了一篇關于“在龐磁阻氧化物薄膜器件中發現電脈沖觸發可逆電阻轉變效應”的文章后,夏普公司買了該專利,才對RRAM開始了業界的開發,自此以后才引起學術界和業界的研究。主流存儲器廠商也紛紛投入力量,開始對RRAM的研究。RRAM也已經由實驗室階段進入到企業的研發階段。

從容量上看,這三類新型存儲器,MRAM最高達4Gb,PRAM最高達8Gb,RRAM最高達32Gb。它們和閃存相比,容量差別還很大,但是不要忘記,這三者的讀寫速度都比閃存要快1000倍以上。

以上就是我們想要分享給大家的集成電路發展史上的十大里程碑事件,目前半導體行業圈內優秀的研發人員還有很多,他們分布在產業鏈的上中下游,分布在全世界各地,正為自己熱愛的這份事業披荊斬棘,希望在前方道路努力奔跑的大家,能夠熠熠閃光!

責任編輯:lq

-

集成電路

+關注

關注

5389文章

11572瀏覽量

362223 -

晶體管

+關注

關注

77文章

9705瀏覽量

138454 -

光刻技術

+關注

關注

1文章

146瀏覽量

15851

原文標題:集成電路發展史上的十大里程碑事件

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

破萬億!中國芯片出口迎來里程碑

比亞迪海豹榮獲日本年度風云車十大最佳車型獎

e絡盟達成BBC micro:bit計算機制造分銷里程碑

e絡盟實現重要里程碑:成功分銷 1000 萬套 micro:bit 設備

喆塔科技與國家級創新中心共建高性能集成電路數智化聯合工程中心

比亞迪達成新能源汽車下線千萬輛里程碑

“中國芯”產業的十年歷程和國內集成電路區域發展研究(下篇)

黑芝麻智能與Nullmax達成重要合作里程碑

特斯拉里程碑達成:第1億顆4680電池震撼問世

廣立微集成電路EDA產業化基地項目結頂

特斯拉迎來里程碑:全球第1000萬個電驅系統下線

重磅!兩項集成電路國家標準正式發布,產業即將迎來新變革

它人機器人與俄羅斯的AVIALIFT正式攜手,達成里程碑式合作

集成電路發展史上的十大里程碑事件!

集成電路發展史上的十大里程碑事件!

評論