1 引 言

電壓基準源足集成電路中一個重要的單元模塊,是D/A,A/D轉換器及脈沖寬度調制電路中的基本單元。他的溫度穩定性及抗噪能力不僅是影響A/D,D/A轉換精度的關鍵因素,甚至影響到整個系統的精度和性能。基準電壓的精度決定了所有IC系統所能達到的最佳性能。因此基準電壓電路對于溫漂,以及于精度有關的指標要求比較高。由于帶隙基準源能夠實現高電源抑制比和低溫度系數,是目前各種基準電壓源電路中性能最佳的基準源電路。

為了實現高精度,通常都用硅半導體材料本身固有的特征電壓作為基準電壓,但由于硅半導體材料具有一定的溫度系數,所以為解決溫漂問題,通常選擇一種與基準電壓的溫度系數極性相反但絕對值相近的器件或電路(如△VBE電路),使兩者結合起來,相互溫度補償,使總體溫度系數近似為零。

2 能隙基準電壓的基本原理

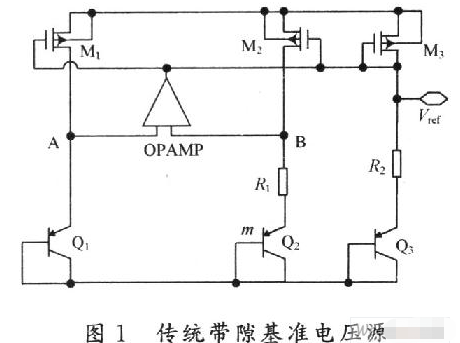

能隙基準電壓的基本原理如圖1所示。

雙極晶體管的基極-發射極電壓VBE(PN結二極管的正向電壓),具有負溫度系數,其溫度系數在室溫下-2.2 mV/K。而熱電壓VT具有正溫度系數,其溫度系數在室溫下為+O.085 mV/K。將VT乘以常數K并和VBE相加可得到輸出電壓VREF:

VREF=VBE+KVT (1)

將式(1)對溫度T微分并代人VBE和VT的溫度系數可求得K,他使VREF的溫度系數在理論上為0。VBE受電源電壓變化的影響很小,因而帶隙基準電壓的輸出電壓受電源的影響也很小。由于在這種情況下得到的基準電壓的值接近于材料的帶隙電壓,所以稱為帶隙基準源。

3 電路設計與實現

3.1 經過曲率補償后改進的基準核心電路

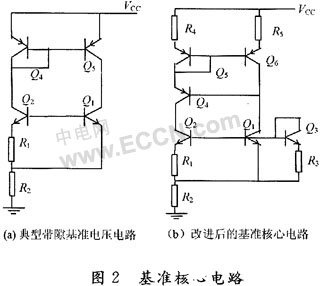

圖2(a)為典型的帶隙基準電壓產生電路,對其進行改進,如圖2(b)所示,其核心部分由Q1~Q6,R1~R5組成。A1,A2和A3是Q1,Q2和Q3的發射極面積,且A2是A1的N倍,A3是A1的M倍。橫向PNP管Q4,Q5,Q6構成恒流源。

將這個壓差加在R1上,則流過的電流Ie2等于Q1發射極的電流Ie1為:

![]()

設流過R3上的電流可以近似為Q3的發射極電流Ie3,則有:

![]()

所以:

其中N是Q2,Q1的發射級面積的比值,M為Q3,Q1的發射級面積的比值。

經過R2的電流設為IR2,則:

式(3)右邊前兩項是IR2的PTAT部分設為IPTAT,而第三項為非線性部分設為,INL,于是IR2可以表示為:

![]()

可見,圖2的電路結構可以對VBE中隨溫度變化的非線性部分進行補償,以達到較好的溫度特性。

由文獻[5]可知:

其中,r,a,E,G為與溫度無關的常數。

令:

![]()

![]()

把IPTAT與JNL的值代入,并聯立式(7),(8)得一不定方程,經過不斷迭代和仿真,總是可以找到一個工作點實現較好的溫度補償。

從圖(2),可以得出:

![]()

把式(4)代入式(9)中,得最終的基準電壓為:

3.2 啟動電路

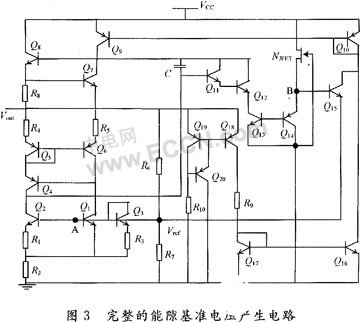

如圖3所示,NJFET,Q15構成啟動電路。當加電源后,NJFET處于常通狀態,溝道較長,相當與一個大電阻,Q15導通,于是給Q1,Q2提供基極電流,同時,Q10的集電極有電流通過,由于Q9與Q10的鏡像作用,Q9的集電極電流使得Q8管打開,給基準電路提供一個工作電壓,電路開始工作,通過改變R6與R7的比值,可以調整VOUT的輸出電壓。作為啟動電路,為了不影響電路正常工作,在基準建立以起來以后,要能自動關掉。Q11~Q14是用來關斷啟動電路,當基準建立起來之后,B點的電位被鉗至到兩個BE節壓降,Q15截止,此時Q10的集電極電流由Q16,Q17組成的電流鏡提供,從而保證基準電路正常工作。電容C用來是濾波,可以提高了電路的電源抑制比。

由于電路中沒有采用運算放大器,可避免引入失調對基準電壓精度產生影響。

4 電路仿真結果

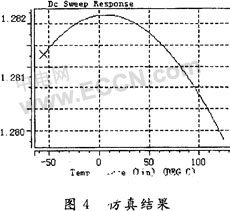

在SUN工作站上用CADAENCE的HSPICE仿真工具對電路進行了對基準電壓源分別進行溫度分析及電源變化分析仿真,如圖4所示,當溫度從-55~125℃溫度范圍變化時,Vref從1.277~1.282 V變化,最大變化為5 mV,在25℃時達到最大1.282 V。Vout從5.022~

5.043 V變化,溫度系數達到20 ppm/℃。25℃時,VCC從7~40 V變化時,Vref在1.281 69~1.282 12 V之間變化,變化量為0.43 mV,如圖4所示。他能滿足PWM電路對基準源要求,溫漂較小和電源電壓抑制比高。經流片測試,其完全滿足PWM對基準源各種參數的要求。

由于是模擬電路,版圖設計需要很高的精度,器件應該匹配,布局布線要合理。為了得到精確基準電壓,Q1與Q2發射極面積的比值要做到很精確,版圖設計中,采用了相同面積的發射極版圖的組合結構。此外為了提高電阻的相對精度,把要求成比例的電阻用完全相同的條形電阻間隔放置,再通過串聯或并聯而成,并盡量遠離發熱量大的器件。用該基準實現的脈寬調制電路的版圖。如圖6所示。

5 結 語

本文在分析典型帶隙基準結構的基礎上,采用曲率補償,設計了一種具有高電源抑制比,低溫度系數的電壓基準電路,7 V電源供電時,功耗大約有9 mw。將其用于PWM電路中,并流片實現,能夠滿足PWM對基準的要求。

責任編輯:gt

-

電源

+關注

關注

184文章

17835瀏覽量

251358 -

轉換器

+關注

關注

27文章

8742瀏覽量

147770 -

晶體管

+關注

關注

77文章

9744瀏覽量

138724

發布評論請先 登錄

相關推薦

高電源抑制比的CMOS亞閾值多輸出電壓基準

新型電流模式曲率補償帶隙基準源設計

CMOS帶隙基準電壓源曲率校正方法

一種高電源抑制比全工藝角低溫漂CMOS基準電壓源

采用曲率補償技術實現高抑制比的電壓基準電路的設計

采用曲率補償技術實現高抑制比的電壓基準電路的設計

評論