Intel將在本季度末發(fā)布代號Ice Lake-SP的新一代至強處理器,面向單路、雙路領(lǐng)域,首次在服務(wù)器上引入10nm工藝,和此前推出的四路/八路型14nm Cooper Lake共同組成第三代可擴展至強。

接下來就是Sapphire Rapids(藍(lán)寶石激流),按順序為第四代可擴展至強,與今年底推出,全面換新,接口也要變。

根據(jù)目前的情報,Sapphire Rapids將會采用10nm Enhanced SuperFin制造工藝,可以視為10nm+++,比目前Tiger Lake移動版上的更強一些,但因為核心規(guī)模急劇增加,功耗最高將達400W。

CPU架構(gòu)升級為Golden Cove,Alder Lake 12代酷睿同款,恢復(fù)支持BF16機器學(xué)習(xí)指令,最多56核心112線程(不排除有隱藏的4個核心),而且是MCM多芯片封裝,并集成HBM高帶寬內(nèi)存,最大64GB。

Sapphire Rapids將在服務(wù)器端首次引入PCIe 5.0總線(最多80條)、DDR5內(nèi)存(八通道4800MHz),還會有第三代傲騰持久內(nèi)存。

由于變化太大,封裝接口將從現(xiàn)在的LGA4189,變成新的LGA4677,增加488個觸點。

今天,有網(wǎng)友曝光了Sapphire Rapids的最新實物照片,即便沒有明顯參照物也能看出其碩大的面積。

正面可見代表工程樣品的Intel Confidential字樣,以及1.3GHz的基準(zhǔn)頻率,背面則是密恐一般的觸點,可見分成了對等的兩大部分,電容等元器件也分成了四組。

據(jù)曝料網(wǎng)友,這是一顆早期的ES0版本工程樣品,所以頻率非常低,后續(xù)還會有ES1版本。

可以確認(rèn)內(nèi)部是釬焊散熱,多芯封裝,內(nèi)部集成四顆小芯片、四顆HBM,支持DDR5、PCIe 5.0,但未透露這顆擁有多少核心。

另外,該網(wǎng)友還放出了LGA4667-X接口的結(jié)構(gòu)尺寸圖。

Sapphire Rapids有望今年底發(fā)布,未來還會搭配Intel針對高性能計算設(shè)計的獨立GPU Ponte Vecchio,組成超算平臺,每個計算節(jié)點兩顆CPU、六顆GPU。

美國設(shè)計中的百億億次超級計算機Aurora,就是與Intel合作打造,基于這種計算平臺。

責(zé)任編輯:PSY

-

intel

+關(guān)注

關(guān)注

19文章

3493瀏覽量

187797 -

PCIe

+關(guān)注

關(guān)注

16文章

1308瀏覽量

84566 -

DDR5

+關(guān)注

關(guān)注

1文章

441瀏覽量

24663

發(fā)布評論請先 登錄

PCIe 5.0市場加速滲透,PCIe 6.0研發(fā)到來

DDR4漲價20%,DDR5上調(diào)5%!

大型文件秒開、多開任務(wù)流暢——DDR5的優(yōu)勢遠(yuǎn)不止頻率

DDR3、DDR4、DDR5的性能對比

DDR5內(nèi)存與DDR4內(nèi)存性能差異

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

揭秘DDR5的讀寫分離技術(shù)奧秘

SK海力士開發(fā)出第六代10納米級DDR5 DRAM

SK海力士DDR5芯片價格或?qū)⒋蠓蠞q

Introspect DDR5/LPDDR5總線協(xié)議分析儀

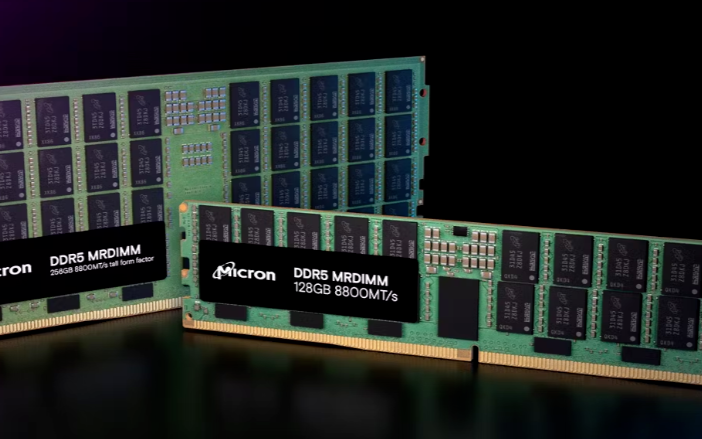

DDR5 MRDIMM內(nèi)存標(biāo)準(zhǔn)將發(fā),存儲廠商方案先行

DDR5內(nèi)存條上的時鐘走線

0706線下活動 I DDR4/DDR5內(nèi)存技術(shù)高速信號專題設(shè)計技術(shù)交流活動

南亞科技明年初試產(chǎn)DDR5內(nèi)存顆粒,四款1Bnm制程DRAM產(chǎn)品已投產(chǎn)

全球第一款配備DDR5 CAMM2內(nèi)存的桌面主板誕生!

評論