原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處(http://www.alinx.com)。

適用于板卡型號:

PGL22G/PGL12G

1. 實驗簡介

本實驗的錄音和播放實驗因為開發板上沒有音頻部分的電路,需要外接一個芯驛電子的AUDIO音頻模塊AN831。

AN831

音頻模塊上有三個音頻連接器,其中粉色的接口為麥克風輸入;綠色的接口為耳機輸出;藍色的接口為音頻輸入, 用于連接DVD等音頻輸出口。本實驗將實現音頻模塊和FPGA之間的數據通信, 通過音頻模塊把麥克風輸入的語音數據存儲到SDRAM存儲器里, 再把音頻數據發送給音頻模塊,從耳機接口進行語音的播放,從而實現錄音和播放的功能。

2. 實驗原理

2.1 硬件介紹

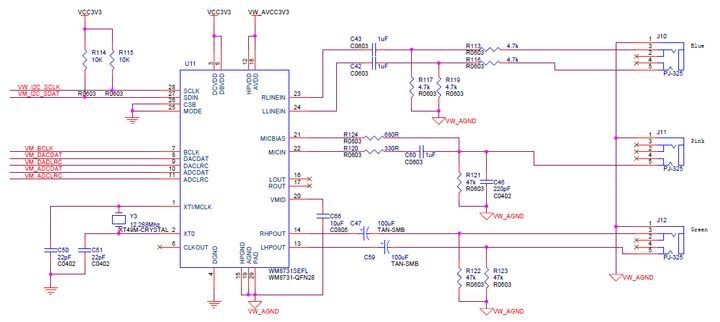

開發板通過40PIN的擴展口和AN831音頻模塊連接,AN831音頻模塊使用WOLFSON公司的WM8731芯片實現聲音信號的A/D和D/A轉換功能。以下為AN831音頻模塊的硬件電路:

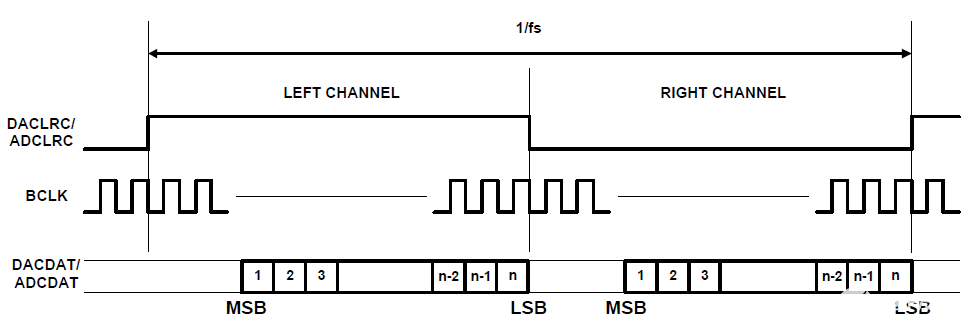

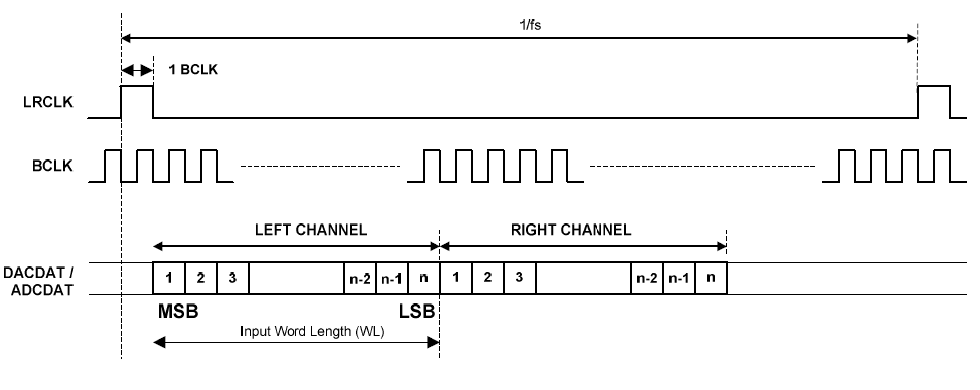

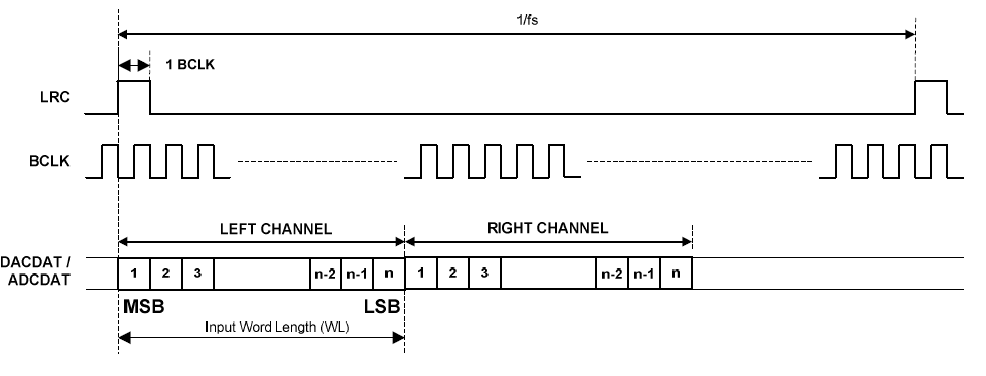

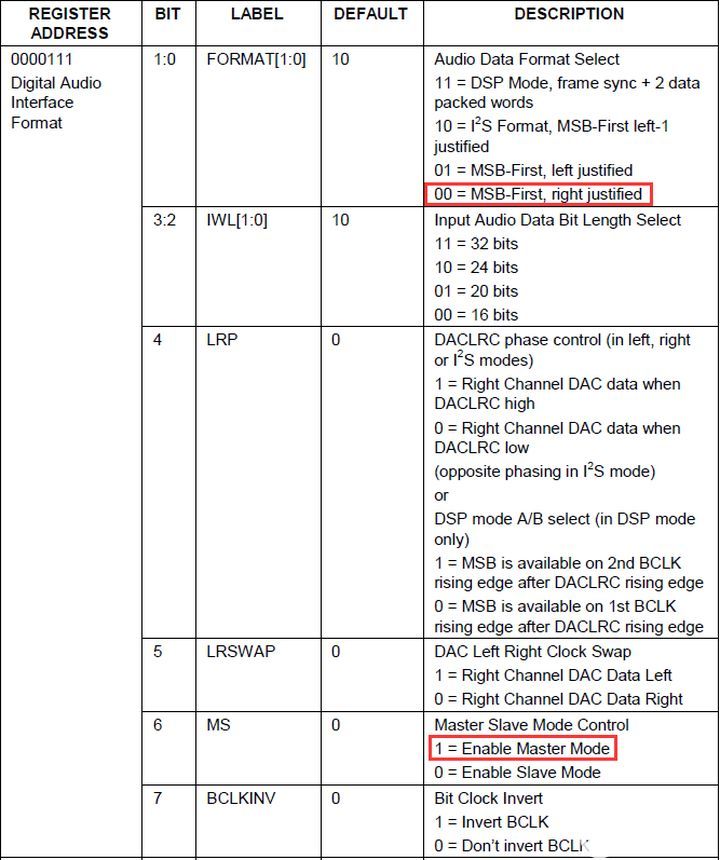

2.2 WM8731配置和時序

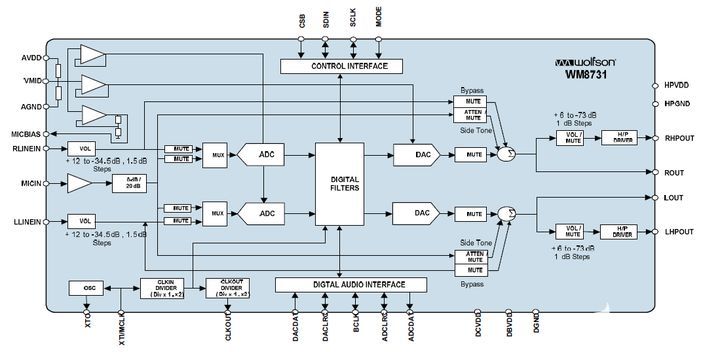

這里簡單介紹一下音頻模塊AN831用到的音頻編/解碼芯片WM8731。該芯片在本設計中主要完成聲音信號在采集和回放過程中的A/D和D/A轉換功能。該芯片的ADC和DAC的采樣頻率為8KHz到96KHz可調,可轉換的數據長度為16-32位可調。WM8731的內部有11個寄存器。該芯片的初始化以及工作時的工作狀態和功能都是通過以I2C總線方式對其內部的這11個寄存器進行相應的配置來實現的。本設計中WM8731工作于主模式,采樣頻率設為48KHZ,轉換的數據位長度為16位。WM8731的數字音頻接口有5根引腳,分別為:BCLK(數字音頻位時鐘)、DACDAT(DAC數字音頻數據輸入)、DACLRC(DAC采樣左/右聲道信號)、ADCDAT(ADC數字音頻信號輸出)、ADCLRC(ADC采樣左/右聲道信號)。在本設計中FPGA為從設備,WM8731為主設備。ADCDAT、DACDAT、ADCLRC和DACLRC與位時鐘BCLK同步,在每個BCLK的下降沿進行一次數據傳輸。BCLK、DACDAT、DACLRC、ADCLRC為WM8731的輸入信號。ADCDAT為WM8731的輸出信號。

在本系統中FPAG和WM8731的控制和數據通信將用到I2C和數字音頻總線接口。FPGA通過I2C接口配置WM8731的寄存器,通過I2S總線接口來進行音頻數據的通信。關于I2C接口,其他實驗中已經有講解,下面我們主要來了解數字音頻接口。

數字音頻接口可提供4種模式:

Left justified模式

Left justified模式 I2S模式

I2S模式 Right justified模式

Right justified模式 DSP/PCM 模式(MODE A)

DSP/PCM 模式(MODE A) DSP/PCM 模式(MODE B)

DSP/PCM 模式(MODE B)

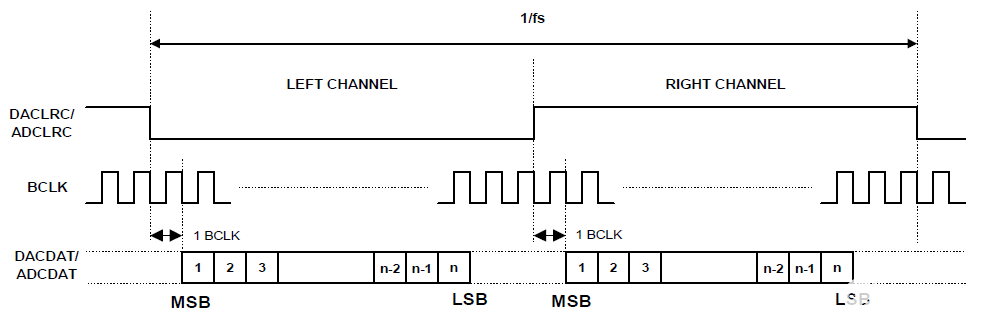

本實驗選擇Right justified模式。

3. 程序設計

本實驗的功能是程序檢測按鍵KEY2是否按下,如果檢測到KEY2按下了,開始錄音,錄音的最長時間為20秒;錄音結束后,開始播放剛才錄下的音頻。本程序設計包含四大部分:SDRAM的讀寫控制程序,音頻錄音和播放,按鍵檢測和系統控制。

lut_wm8731模塊將寄存器配置地址和配置信息通過查找表的形式通過I2C總線寫入音頻模塊中,具體的請參考例程代碼和wm9731的芯片數據手冊。

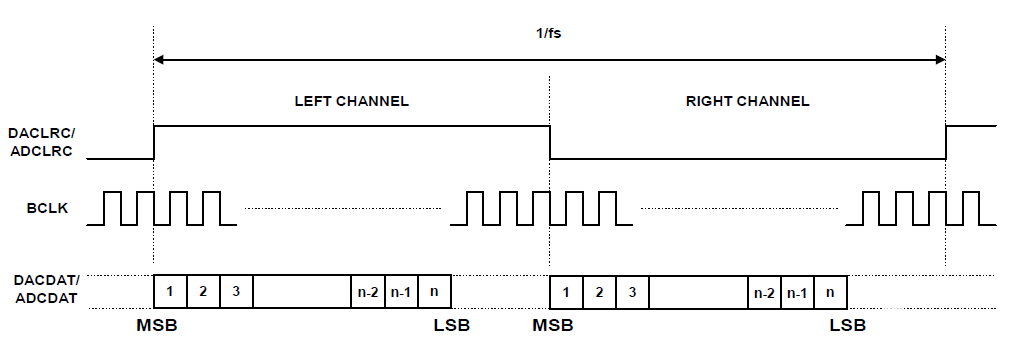

audio_rx接收模塊,接收從麥克風輸入的語音信號,完成左右聲道的音頻接收,將串行數據轉換成并行數據。通過“Right justified”模式的時序圖可以看到接收語音信號時在LRC信號為高電平,且BCLK信號的上升沿時左聲道接收數據并完成串行信號轉換成并行信號的過程。在LRC信號為低電平,且BCLK 信號的上升沿時右聲道接收數據并完成串行信號轉換成并行信號的過程。

| 信號名稱 | 方向 | 說明 |

| clk | in | 時鐘輸入 |

| rst | in | 異步復位輸入,高復位 |

| sck_bclk | in | 數字音頻接口bit時鐘 |

| ws_lrc | in | ADC采樣時鐘 |

| sdata | in | 音頻數字接口串行數據輸入 |

| left_data | out | 左聲道數據 |

| right_data | out | 右聲道數據 |

| data_valid | out | 音頻數據有效 |

audio_rx音頻接收模塊端口

audio_tx是音頻發送模塊,完成左右聲道音頻數據的串行化。同樣通過時序圖可以看到,語音信號完成模數,數模轉換從SDRAM輸出后進入發送模塊,在LRC信號上升沿,且即將跳變為高電平時接收左聲道數據,BCLK信號下降沿時完成緩存將并行信號轉換為串行信號的過程;在LRC信號上升沿且即將跳變為低電平時接收右聲道數據,在BCLK信號下降沿時完成緩存將并行信號轉換為串行信號的過程。

| 信號名稱 | 方向 | 說明 |

| clk | in | 時鐘輸入 |

| rst | in | 異步復位輸入,高復位 |

| sck_bclk | in | 數字音頻接口bit時鐘 |

| ws_lrc | in | ADC采樣時鐘 |

| sdata | out | 音頻數字接口串行數據輸入 |

| left_data | in | 左聲道數據 |

| right_data | in | 右聲道數據 |

| read_data_en | out | 音頻數據讀取,提前一個采樣周期讀取 |

audio_tx音頻發送模塊端口

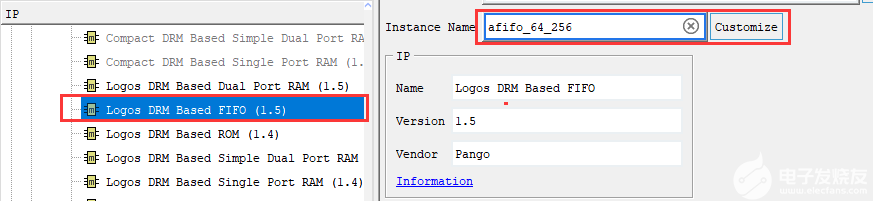

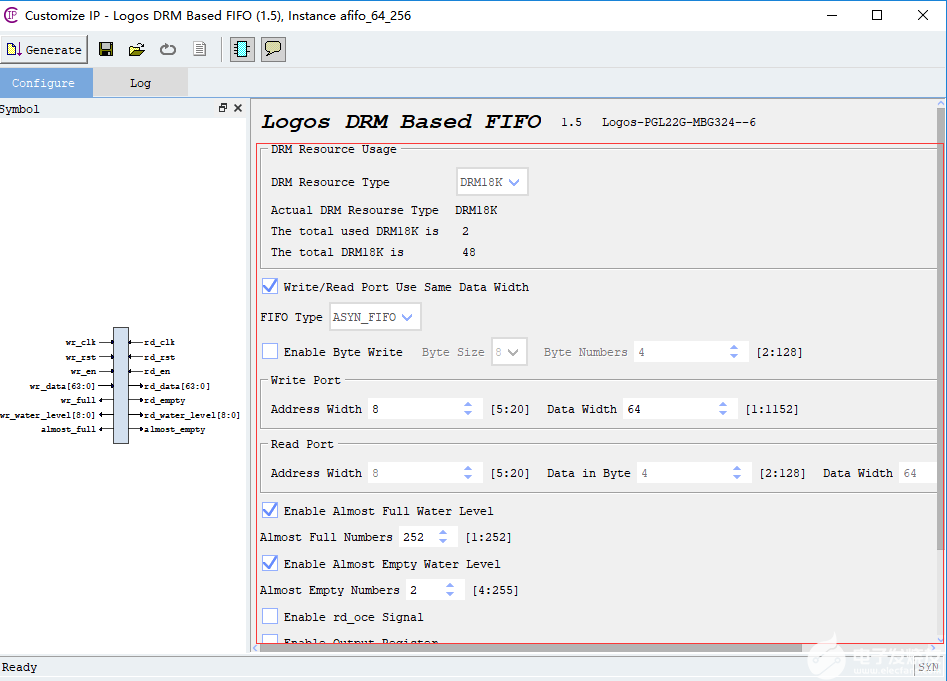

在模塊‘frame_read_write’中使用到了FIFO 的IP core,通過兩個FIFO分別作為DDR3控制器的讀寫接口,避免復雜的DDR3時序。因為時鐘速率的不同,所使用的是異步FIFO。以write_buf寫入模塊的FIFO為例在vivado中FIFO IP core設置如下:

-

打開Tools菜單下的“IP Compiler”, 在彈出的界面下進行如下設置,設置完成后點擊”Customize”:

-

在彈出的界面下進行如下設置,設置完成后點擊保存后Generate即可生成IP:

-

接著在模塊中直接例化FIFO 的端口名就可以使用FIFO了,在read_buf中也是同樣的操作步驟。具體的參數設置和端口例化的信號連接參考例程。

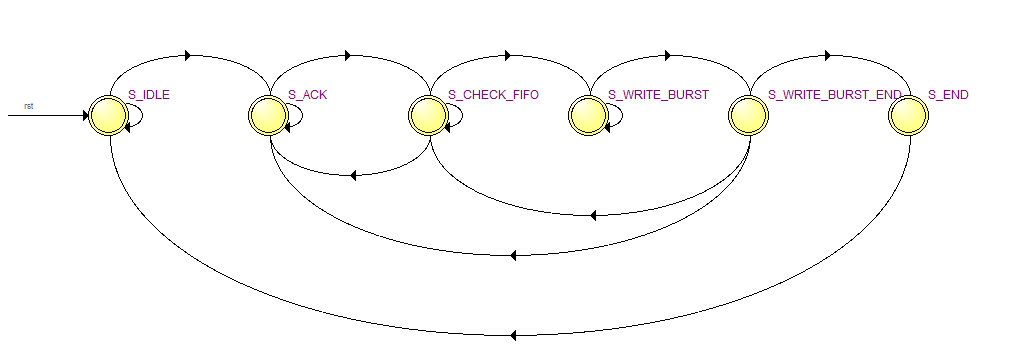

frame_fifo_write模塊完成FIFO數據到外部存儲器的寫入,如果FIFO接口是異步FIFO,可以完成寫數據的跨時鐘域轉換。狀態機轉換圖如下,收到寫數據請求后進入應答狀態“S_ACK”,如果寫請求撤銷,則進入檢測FIFO空間大小狀態“S_CHECK_FIFO”,檢查FIFO內數據是否夠一次突發寫,如果有足夠多的數據,進入突發寫存儲器狀態“S_WRITE_BURST”,突發寫完成后進入“S_WRITE_BURST_END”狀態。

frame_fifo_write模塊狀態機

frame_fifo_write模塊狀態機

| 信號名稱 | 方向 | 說明 |

| mem_clk | in | 外部存儲器用戶時鐘輸入 |

| rst | in | 異步復位輸入,高復位 |

| wr_burst_req | out | 對接存儲器控制器,寫請求 |

| wr_burst_len | out | 對接存儲器控制器,寫請求長度 |

| wr_burst_addr | out | 對接存儲器控制器,寫請求基地址 |

| wr_burst_data_req | in | 對接存儲器控制器,寫請求數據索取,提前一個時鐘周期發出,用于連接FIFO的讀數據 |

| wr_burst_finish | in | 對接存儲器控制器,寫請求完整 |

| write_req | in | 一幀(大量數據)寫開始,收到應答后必須撤銷請求,新的請求會中斷正在進行的請求 |

| write_req_ack | out | 一幀(大量數據)寫應答 |

| write_finish | out | 一幀(大量數據)完成 |

| write_addr_0 | in | 一幀(大量數據)寫基地址0 |

| write_addr_1 | in | 一幀(大量數據)寫基地址1 |

| write_addr_2 | in | 一幀(大量數據)寫基地址2 |

| write_addr_3 | in | 一幀(大量數據)寫基地址3 |

| write_addr_index | in | 一幀(大量數據)寫基地址選擇,0:write_addr_01:write_addr_12:write_addr_23:write_addr_3 |

| write_len | in | 一幀(大量數據)寫長度 |

| fifo_aclr | out | 在收到寫請求后,模塊會清空FIFO |

| rdusedw | in | FIFO讀端的數據使用量 |

frame_fifo_write模塊端口

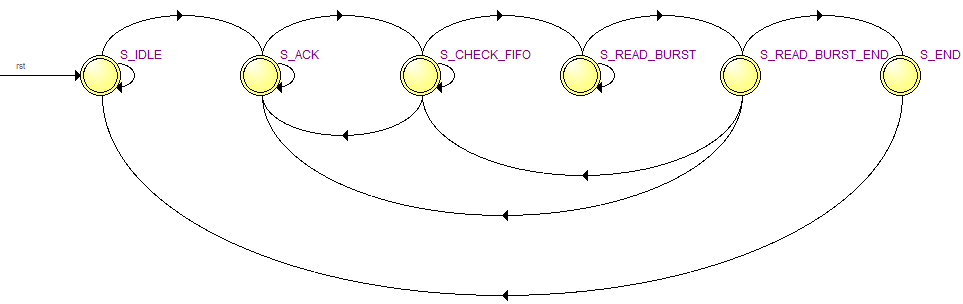

frame_fifo_read讀模塊完成從外部存儲器讀取數據,然后寫到FIFO,如果使用異步FIFO可以完成數據從存儲器時鐘域到其他時鐘域的轉換。狀態機轉換圖如下圖所示,收到讀請求以后進入應答狀態“S_ACK”,等待讀請求撤銷后應答,進入FIFO深度檢測狀態“S_CHECK_FIFO”,如果FIFO空間足夠一次突發讀,進入突發讀狀態“S_READ_BURST”,突發讀結束后進入“S_READ_BURST_END”。

frame_fifo_read模塊狀態機

frame_fifo_read模塊狀態機

| 信號名稱 | 方向 | 說明 |

| mem_clk | in | 外部存儲器用戶時鐘輸入 |

| rst | in | 異步復位輸入,高復位 |

| rd_burst_req | out | 對接存儲器控制器,讀請求 |

| rd_burst_len | out | 對接存儲器控制器,讀請求長度 |

| rd_burst_addr | out | 對接存儲器控制器,讀請求基地址 |

| rd_burst_data_valid | in | 對接存儲器控制器,讀請求數據有效 |

| rd_burst_finish | in | 對接存儲器控制器,讀請求完全 |

| read_req | in | 一幀數據讀開始 |

| read_req_ack | out | 一幀數據讀應答 |

| read_finish | out | 一幀數據讀完成 |

| read_addr_0 | in | 一幀數據讀基地址0 |

| read_addr_1 | in | 一幀數據讀基地址1 |

| read_addr_2 | in | 一幀數據讀基地址2 |

| read_addr_3 | in | 一幀數據讀基地址3 |

| read_addr_index | in | 一幀數據讀基地址選擇0:read_addr_01:read_addr_12:read_addr_23:read_addr_3 |

| read_len | in | 幀數據讀長度 |

| fifo_aclr | out | 外部FIFO異步復位 |

| wrusedw | in | FIFO寫端使用空間大小 |

frame_fifo_read模塊端口

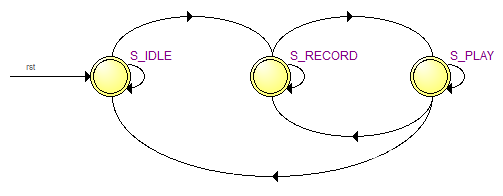

audio_key模塊主要完成錄音播放的按鍵控制,狀態轉換如下,當按鍵按下后進入錄音狀態,當按鍵松開時進入播放狀態。

audio_key模塊狀態轉換圖

audio_key模塊狀態轉換圖

| 信號名稱 | 方向 | 說明 |

| clk | in | 時鐘輸入 |

| rst | in | 異步復位輸入,高復位 |

| key | in | 按鍵輸入 |

| record | out | 錄音狀態指示 |

| play | out | 播放狀態指示 |

| write_req | out | 寫數據開始 |

| write_req_ack | in | 寫數據應答 |

| read_req | out | 讀數據開始 |

| read_req_ack | in | 讀數據應答 |

frame_read_write模塊完成音頻幀數據讀寫的封裝,這里使用了異步FIFO來解決跨時鐘問題,例如FIFO 輸入寬度和輸出寬度的不同來完成數據位寬的轉換。

4. 實驗現象

開發板首先將音頻模塊插入擴展口,同時插入麥克風和耳機,然后下載實驗程序,按下KEY2不放,進行錄音,松開按鍵后可通過耳機回放錄音。

-

FPGA

+關注

關注

1635文章

21837瀏覽量

608348 -

電路

+關注

關注

173文章

5991瀏覽量

173487 -

音頻

+關注

關注

29文章

2925瀏覽量

82380 -

開發板

+關注

關注

25文章

5210瀏覽量

99126 -

紫光同創

+關注

關注

5文章

89瀏覽量

27671

發布評論請先 登錄

相關推薦

【國產FPGA入學必備】刀劍在鞘,兵器先藏 | 盤古676系列國產FPGA開發板

【國產FPGA入學必備】國產FPGA權威設計指南+配套FPGA圖像視頻教程

【國產FPGA必備教程】——紫光同創FPGA圖像視頻教程,適用于小眼睛FPGA盤古全系列開發板

【米爾-紫光MYB-J7A100T國產FPGA開發板試用】米爾-紫光PG2L100H國產FPGA開發板開箱評測

紫光同創聯合舉辦全國高校國產FPGA產學研融合研討會

大連理工和南信大-紫光同創FPGA創新實踐基地揭牌

紫光同創助力國產FPGA高校生態建設

ALINX亮相2024紫光同創FPGA技術研討會

【紫光同創盤古PGX-Nano教程】——(盤古PGX-Nano開發板/PG2L50H_MBG324第十一章)模擬波形實驗例程說明

盤古200K開發板,紫光同創PG2L200H,Logos2系列,資源豐富,功能強大

國產FPGA核心板!米爾紫光同創Logos-2和Xilinx Artix-7核心板

FPGA核心板上市!紫光同創Logos-2和Xilinx Artix-7系列

【紫光同創國產FPGA教程】【第十一章】錄音與播放例程

【紫光同創國產FPGA教程】【第十一章】錄音與播放例程

評論