今天查閱了一下晶圓良率的控制,晶圓的成本和能否量產最終還是要看良率。晶圓的良率十分關鍵,研發期間,我們關注芯片的性能,但是量產階段就必須看良率,有時候為了良率也要減掉性能。

那么什么是晶圓的良率呢?

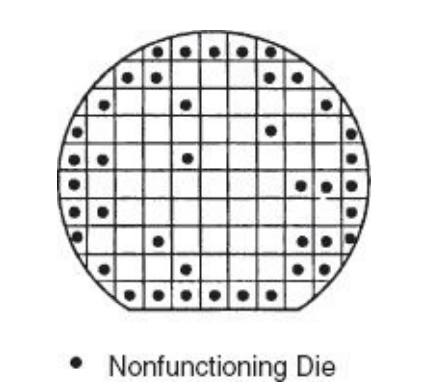

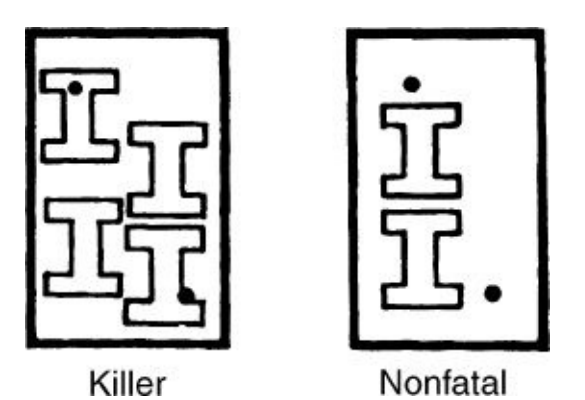

比如上圖,一個晶圓,通過芯片最好測試,合格的芯片/總芯片數===就是該晶圓的良率。普通IC晶圓一般都可以完成在晶圓級的測試和分布mapping出來。

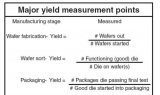

良率還需要細分為wafer良率、Die良率和封測良率,而總量率則是這三種良率的總乘積,總量率將決定一家晶圓廠到底是賠錢還是賺錢。

舉個例子,如果某個晶圓廠的一條產線上每一道制程良率都高達99%,那么經過600道工序后整體良率是多少呢?答案是0.24%,幾乎為0。

所以,晶圓代工企業都會視總良率為最高機密,對外公布的數據往往都不會是企業的真正總良率。

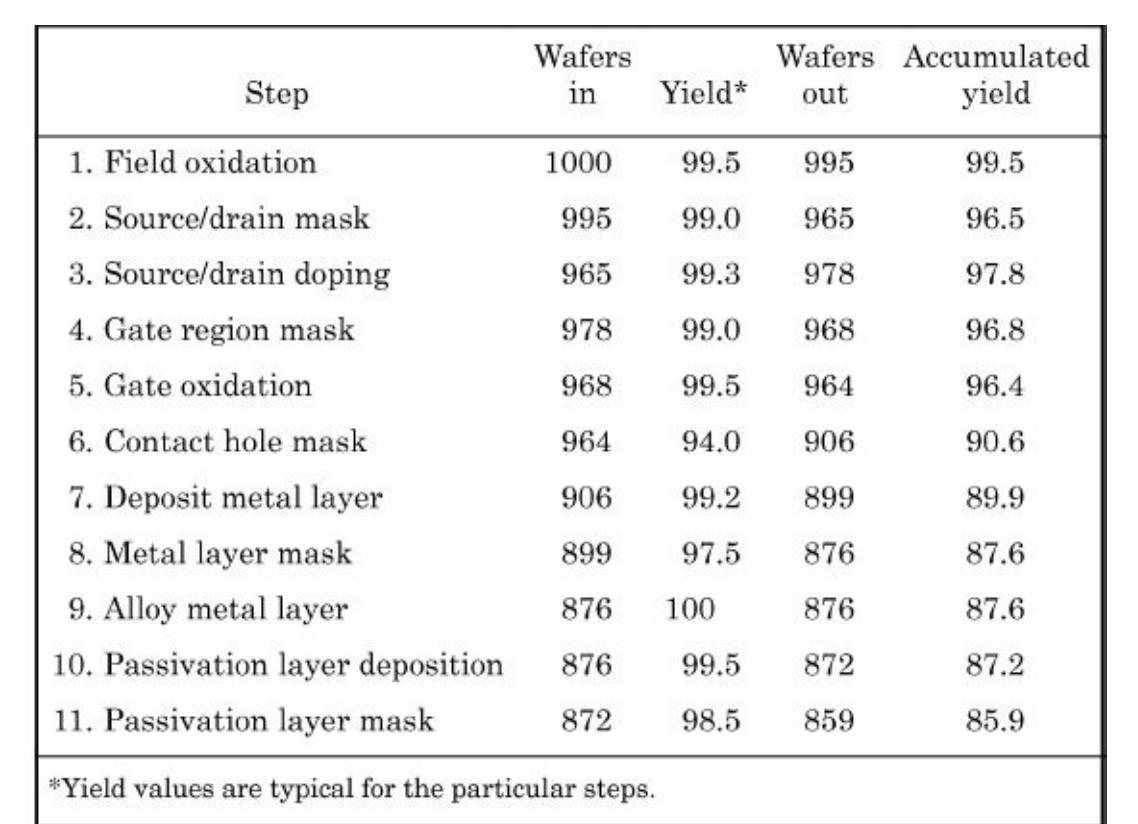

而晶圓的最終良率主要由每一步工藝的良率的積組成,從晶圓制造,中測,封裝到成測,每一步都會對良率產生影響,其中晶圓制造因為工藝復雜,工藝步驟多步(300步左右)成為影響良率的主要因素。由此可見,晶圓良率越高,同一片晶圓上產出的好芯片數量就越多,如果晶圓價格是固定的,那好芯片數量就越多就意味著每片晶圓的產量越高,每顆芯片的成本越低,那么理所當然,利潤也就越高。

晶圓的良率受工藝設備、原材料等影響很大,要想達到較高的晶圓良率,首先要穩定工藝設備,定期做工藝能力恢復等。另外環境因素對wafer良率、Die良率和封測良率這三種良率都會產生一定影響。常見的環境因素包括塵埃、濕度、溫度和光照亮度,所以芯片制造和封測的過程中都需要在超凈的工作環境中進行。最后,是技術成熟度問題。一般情況下,新工藝剛出來的時候良率會很低,隨著生產的進行和導致低良率的因素被發現和改進,則良率就會不斷地被提升。如今,新工藝或是工具,每個幾個月或甚至幾周就會被引進,因此提升良率就成了半導體公司的一個永不停息的過程。

如何把控晶圓良率

很多半導體公司都有工程師專門從事良率提高的工作,在晶圓廠(foundary)有專門的良率提高(YE)部門的良率工程師負責提高晶圓的良率,在無晶圓公司(Fabless)的運營部門有產品工程師(PE)要負責提高良率。由于領域有所不同,這些工程師所專注的重點也會有所區別。晶圓廠內的良率工程師對制造工藝十分精通,主要通過公司的良率管理系統(YMS)對工藝相關的一些數據進行良率分析,一般有以下幾種方法:

1)產線中缺陷掃描數據(Inline Defect Scan)

2)工藝監控測試數據(WAT)

3)產線量測數據(Metrology)

4)設備共同性(Tool Commonality)

5)工藝規范性(Process Specifications)

6)失效分析(Failure Analysis)

無晶圓公司的產品工程師則對自己的產品非常熟悉,掌握一些設計數據和很多測試數據,所以產品工程師對良率分析會從一些幾個方面開展[1]:

1)設計數據包括版圖和電路圖等(GDS,Schematic,etc)

2)電性測試數據(Wafer Probling,Final Test data)

3)Schmoo圖

4)比特圖(Bitmap)

5)系統級測試(System Level Test)

6)失效分析(Failure Analysis)

對于有實際生產線的晶圓制造,對每臺制造設備的穩定性監控很重要,如上圖,可以通過記錄設備的關鍵工藝產生,積累出一個隨生產時間改變的波段的曲線,形成工藝精度把控的參數點。

最后,晶圓被測試完畢之后,通過自動分揀機,可以剔除不良芯片,而且對性能良莠不齊的芯片也可以分檢,比如Intel的CPU晶圓,性能較好的芯片檢出來做i7處理器芯片,差點的做i5芯片,其實都是一個娘生的,只不過一個長的好看點,一個長得難看點的區別。

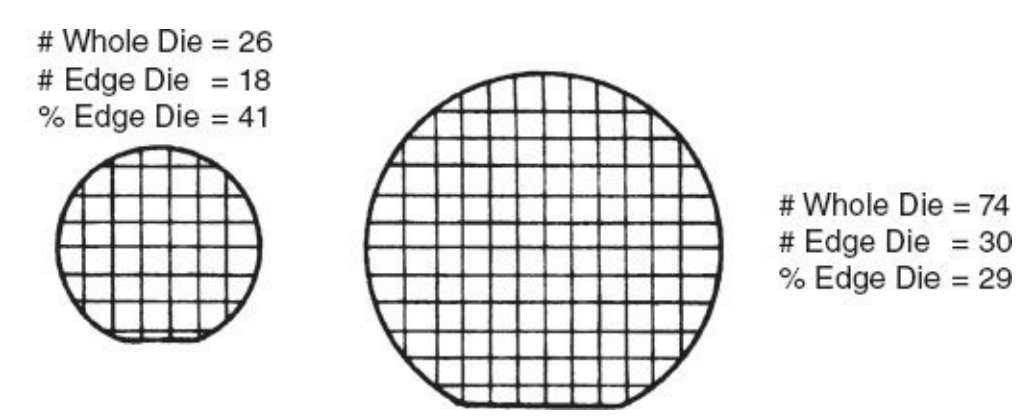

還有就是不同尺寸的晶圓,同一條產線做出來良率也會不同,倒不一定小片的良率一定高于大片。這也和設備工藝的匹配度有關,一個晶圓一般邊緣區域的不良die最多,因此很多產線追求大尺寸晶圓,這樣相對而言邊緣的不良die占比就低。

但是大尺寸的晶圓就面臨許多應力、膜層生長等先天性問題。比如前幾年半導體熱衷上10寸,12寸的產線,導致8寸、6寸產線被遺棄,連半導體設備商都不做小尺寸晶圓的設備了,20年這兩年8寸二手設備這個緊俏,一朋友公司閑置1年的6寸晶圓廠現在都接單接不過來,風水輪流轉啊!可能是中美貿易戰像一些汽車芯片、通信芯片很多公司都在找國產的替代品。

原文標題:晶圓芯片的良率

文章出處:【微信公眾號:芯片工藝技術】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

455文章

50714瀏覽量

423141 -

晶圓

+關注

關注

52文章

4890瀏覽量

127931

原文標題:晶圓芯片的良率

文章出處:【微信號:dingg6602,微信公眾號:芯片工藝技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

晶圓劃片為什么用UV膠帶

晶圓/晶粒/芯片之間的區別和聯系

碳化硅晶圓和硅晶圓的區別是什么

半導體工藝之生產力和工藝良率

晶圓制造和封裝之影響良率的主要工藝和材料因素(一)

如何把控晶圓芯片的良率?

如何把控晶圓芯片的良率?

評論