ZYNQ架構(gòu)

雙核ARM Cortex-A9 處理器:ARM Cortex-A9 是一個(gè)應(yīng)用級(jí)的處理器,能運(yùn)行完整的像Linux 這樣的操作系統(tǒng)

傳統(tǒng)的現(xiàn)場(chǎng)可編程門陣列(Field Programmable Gate Array,FPGA)邏輯部件:基于Xilinx 7 系列的FPGA 架構(gòu)

這個(gè)架構(gòu)實(shí)現(xiàn)了工業(yè)標(biāo)準(zhǔn)的AXI 接口,在芯片的兩個(gè)部分之間實(shí)現(xiàn)了高帶寬、低延遲的連接。

這意味著處理器和邏輯部分各自都可以發(fā)揮最佳的用途,而不會(huì)有在兩個(gè)分立的芯片之間的那種接口開銷。

外設(shè)是處理器之外的功能部件,一般從事三種功能之一:(一)協(xié)處理器—— 輔助主處理器的單元,往往是被優(yōu)化用于特定任務(wù);(二)與外部接口交互的核心,如連接到LED 和開關(guān)、編解碼器等等;(三)額外的存儲(chǔ)器單元。

PS具有固定的架構(gòu),承載了處理器和系統(tǒng)存儲(chǔ)區(qū)

而PL完全是靈活的,給了設(shè)計(jì)者一面“ 空白畫布” 來創(chuàng)建定制的外設(shè),或重用標(biāo)準(zhǔn)外設(shè)。

ZYNQ的SoC設(shè)計(jì)流基本模型

ZYNQ芯片

處理器系統(tǒng)(PS)

ARM是一顆“硬”處理器,硬件處理器以外的另一種方案,就像Xilinx 的MicroBlaze這樣的“軟”處理器,這是由可編程邏輯部分的單元組合而成的。也就是說,一個(gè)軟處理器的實(shí)現(xiàn)和部署在FPGA 的邏輯結(jié)構(gòu)里的任何其他IP 包是等價(jià)的。要求不高的任務(wù)可以從主的ARM Cortex-A9 處理器上脫離出來,分配給軟處理器,軟處理器與ARM協(xié)同工作,提升整體性能

PS里并非只有ARM 處理器,還有一組相關(guān)的處理資源,形成了一個(gè)應(yīng)用處理器單元(Application Processing Unit,APU),另外還有擴(kuò)展外設(shè)接口、cache 存儲(chǔ)器、存儲(chǔ)器接口、互聯(lián)接口和時(shí)鐘發(fā)生電路

處理器系統(tǒng)外部接口——PS 和外部接口之間的通信主要是通過復(fù)用的輸入/ 輸出(Multiplexed Input/Output,MIO)實(shí)現(xiàn)的。這樣的連接也可以通過擴(kuò)展EMIO (ExtendedMIO,EMIO)來實(shí)現(xiàn),EMIO 并不是PS 和外部連接之間的直接通路,而是通過共用了PL 的I/O 資源來實(shí)現(xiàn)的。

可用的I/O 包括標(biāo)準(zhǔn)通信接口(SPI,I2C,USB,SD,CAN,UART,GigE)和通用輸入/ 輸出(General Purpose Input/Output,GPIO)

可編程邏輯(PS)

LUT-查找表(https://www.cnblogs.com/lbf-19940424/p/6564885.html)

FF-觸發(fā)器,一個(gè)實(shí)現(xiàn)1 位寄存的時(shí)序電路,帶有復(fù)位功能。FF 的一種用處是實(shí)現(xiàn)鎖存。

CLB-可配置編程邏輯塊

IOB-輸入/ 輸出塊(Input/Output Blocks,IOB)-實(shí)現(xiàn)了PL 邏輯資源之間的對(duì)接,并且提供物理設(shè)備“ 焊盤” 來連接外部電路。每個(gè)IOB 可以處理一位的輸入或輸出信號(hào)。IOB 通常位于芯片的周邊。

除了通用的部分,還有兩個(gè)特殊用途的部件:滿足密集存儲(chǔ)需要的塊RAM和用于高速算術(shù)的DSP48E1片

通用輸入輸出IOB

通信接口--包括PCIExpress、串行RapidIO、SCSI 和SATA

其他可編程邏輯擴(kuò)展接口--XADC,時(shí)鐘,編程與調(diào)試

處理器系統(tǒng)與可編程邏輯的接口

1、AXI標(biāo)準(zhǔn)--Advanced eXtensible Interface

有三類AXI4總線協(xié)議

? AXI4 [2] — 用于存儲(chǔ)映射鏈接,它支持最高的性能:通過一簇高達(dá)256 個(gè)數(shù)據(jù)字(或“ 數(shù)據(jù)拍(data beats)”)的數(shù)據(jù)傳輸來給定一個(gè)地址。

? AXI4-Lite [2] — 一種簡(jiǎn)化了的鏈接,只支持每次連接傳輸一個(gè)數(shù)據(jù)(非批量)。AXI4-Lite也是存儲(chǔ)映射的:這種協(xié)議下每次傳輸一個(gè)地址和單個(gè)數(shù)據(jù)。

? AXI4-Stream [1] — 用于高速流數(shù)據(jù),支持批量傳輸無限大小的數(shù)據(jù)。沒有地址機(jī)制,這種總線類型最適合源和目的地之間的直接數(shù)據(jù)流(非存儲(chǔ)器映射)

互聯(lián)(Interconnect)— 互聯(lián)實(shí)際上是一個(gè)開關(guān),管理并直接傳遞所連接的AXI 接口之間的通信。在PS 內(nèi)有幾個(gè)互聯(lián),其中有些還直接連接到PL (如圖2.9),而另一些是只用于內(nèi)部連接的。這些互聯(lián)之間的連接也是用AXI 接口所構(gòu)成的。

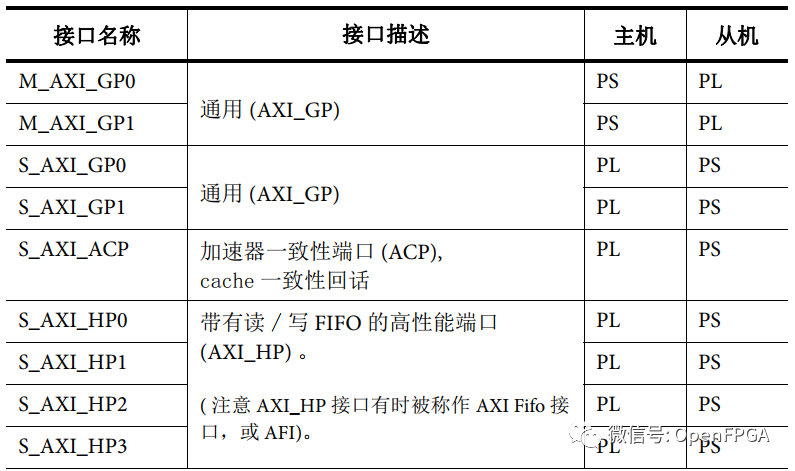

接口(Interface)— 用于在系統(tǒng)內(nèi)的主機(jī)和從機(jī)之間傳遞數(shù)據(jù)、地址和握手信號(hào)的點(diǎn)對(duì)點(diǎn)連接。(M-主機(jī),S-從機(jī))

? 通用AXI(General Purpose AXI) — 一條32 位數(shù)據(jù)總線,適合PL 和PS 之間的中低速通信。接口是透?jìng)鞯牟粠Ь彌_。總共有四個(gè)通用接口:兩個(gè)PS 做主機(jī),另兩個(gè)PL 做主機(jī)。

? 加速器一致性端口(Accelerator Coherency Port) — 在PL 和APU 內(nèi)的SCU之間的單個(gè)異步連接,總線寬度為64 位。這個(gè)端口用來實(shí)現(xiàn)APU cache 和PL的單元之間的一致性。PL 是做主機(jī)的。

? 高性能端口(High Performance Ports) — 四個(gè)高性能AXI 接口,帶有FIFO緩沖來提供“ 批量” 讀寫操作,并支持PL 和PS 中的存儲(chǔ)器單元的高速率通信。數(shù)據(jù)寬度是32 或64 位,在所有四個(gè)接口中PL 都是做主機(jī)的。

表 2.2 給出給出了每個(gè)接口的簡(jiǎn)述,標(biāo)出了主機(jī)和從機(jī) (按照慣例,主機(jī)是控制總線并發(fā)起會(huì)話的,而從機(jī)是做響應(yīng)的)。注意接口命名的規(guī)范(在表 2.2 的第一列)是表示了 PS 的角色的,也就是說,第一個(gè)字母 “M” 表示 PS 是主機(jī),而第一個(gè)字母 “S” 表示 PS 是從機(jī)。

2、EMIO接口

3、其他PL-PS信號(hào)

跨越PS-PL 邊界的其他信號(hào)包括看門狗定時(shí)器、重啟信號(hào)、中斷和DMA 接口信號(hào)。

安全

總結(jié)

附議:

本人覺得除了整體架構(gòu)的創(chuàng)新,靈活的IO也是ZYNQ成為受歡迎的一部分:

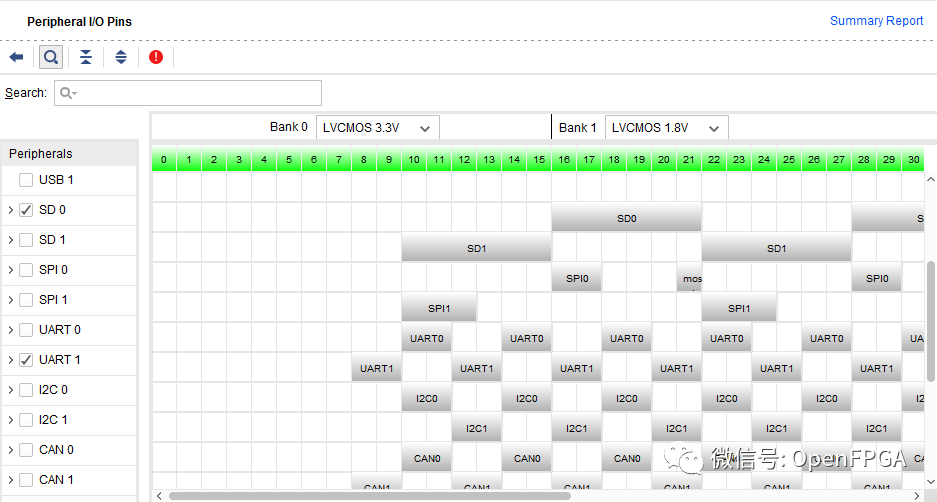

Multiplexed I/O (MIO):PS端外設(shè)IO復(fù)用,這是什么概念呢?前面介紹了ZYNQ主要分PS/PL兩大組成模塊,PS端前面介紹的外設(shè)如USB/CAN/GPIO/UART等都必要需要引腳與外界打交道,這里所謂的復(fù)用與常見的單片機(jī)、處理器里引腳復(fù)用的概念一樣。但是(這里劃重點(diǎn)),ZYNQ具有高達(dá)54個(gè)PS引腳支持MIO,MIO具有非常高的靈活度以達(dá)到靈活配置,這給硬件設(shè)計(jì)、PCB布板帶來了極大的便利!,MIO的配置利用vivado軟件可以實(shí)現(xiàn)靈活配置,如下圖所示。

硬件工程師往往發(fā)現(xiàn)對(duì)一個(gè)復(fù)雜的系統(tǒng)的布局布線,常常會(huì)很困難,也常因?yàn)椴缓侠淼牟季植季€而陷入EMC深坑。ZYNQ的IO引腳高度靈活性,無疑在電路設(shè)計(jì)方面提供極大的方便,可實(shí)現(xiàn)非常靈活的PCB布局布線。從而在EMC性能改善方面帶來了很大便利。

靈活的PS-PL互連接口

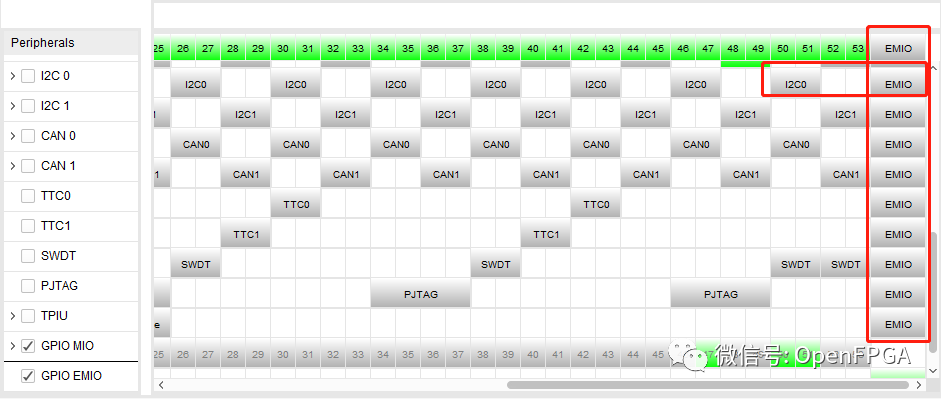

Extended Multiplexed I/O (EMIO):擴(kuò)展MIO,如果想通過PS來訪問PL又不想浪費(fèi)AXI總線時(shí),就可以通過EMIO接口來訪問PL。54個(gè)I/O中,其中一部分只能用于MIO,大部分可以用于MIO或EMIO,少量引腳只能通過EMIO訪問。

如上圖,比如I2C0則可以通過EMIO映射到PL端的引腳輸出,這無疑又增加了更多的靈活性!

PS-PL接口HP0-HP3:如上架構(gòu)圖中AXI high-performance slave ports (HP0-HP3) 實(shí)現(xiàn)了PS-PL的接口

可配置的32位或64位數(shù)據(jù)寬度

只能訪問片上存儲(chǔ)器OCM(On chip memory)和DDR

AXI FIFO接口(AFI)利用1KB FIFOs來緩沖大數(shù)據(jù)傳輸

PS-PL接口GP0-GP1:如上架構(gòu)圖中AXI general-purpose ports

兩個(gè)PS主接口連接到PL的兩個(gè)從設(shè)備

32位數(shù)據(jù)寬度

一個(gè)連接到CPU內(nèi)存的64位加速器一致端口(ACP)AXI從接口,ACP 是 SCU (一致性控制單元)上的一個(gè) 64 位從機(jī)接口,實(shí)現(xiàn)從 PL 到 PS 的異步 cache 一致性接入點(diǎn)。ACP 是可以被很多 PL 主機(jī)所訪問的,用以實(shí)現(xiàn)和 APU 處理器相同的方式訪問存儲(chǔ)子系統(tǒng)。這能達(dá)到提升整體性能、改善功耗和簡(jiǎn)化軟件的效果。ACP 接口的表現(xiàn)和標(biāo)準(zhǔn)的 AXI 從機(jī)接口是一樣的,支持大多數(shù)標(biāo)準(zhǔn)讀和寫的操作而不需要在 PL 部件中加入額外的一致性操作。

DMA, 中斷, 事件信號(hào):

處理器事件總線信號(hào)事件信息到CPU

PL外設(shè)IP中斷到PS通用中斷控制器(GIC)

四個(gè)DMA通道RDY/ACK信號(hào)

擴(kuò)展多路復(fù)用I/O (EMIO)允許PS外設(shè)端口訪問PL邏輯和設(shè)備I/O引腳。

時(shí)鐘以及復(fù)位信號(hào):

四個(gè)PS時(shí)鐘帶使能控制連接到PL

四個(gè)PS復(fù)位信號(hào)連接到PL

責(zé)任編輯:lq

-

處理器

+關(guān)注

關(guān)注

68文章

19265瀏覽量

229682 -

控制器

+關(guān)注

關(guān)注

112文章

16339瀏覽量

177859 -

Zynq

+關(guān)注

關(guān)注

10文章

609瀏覽量

47176

原文標(biāo)題:ZYNQ架構(gòu)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)據(jù)科學(xué)工作流原理

傳理想汽車智能駕駛SoC芯片年底前完成流片

快速部署Tensorflow和TFLITE模型在Jacinto7 Soc

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富!

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

FX3 UVC不穩(wěn)定數(shù)據(jù)流是什么原因?qū)е碌模?/a>

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

Xilinx ZYNQ 動(dòng)手實(shí)操演練

沒用過zynq今天在看解析是發(fā)現(xiàn)汽車的CID上有用這個(gè),不知道zynq有什么優(yōu)勢(shì)?

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

DP9503芯片的multisim模型

基于IMX214+ZYNQ XC7Z100的1080P雙目視覺智能平臺(tái)

ZYNQ的SoC設(shè)計(jì)流基本模型

ZYNQ的SoC設(shè)計(jì)流基本模型

評(píng)論