9、關(guān)于任務和函數(shù)的小結(jié),挑幾點重要的說一下吧

(1)任務具有多個輸入、輸入/輸出和輸出變量,在任務重可以使用延遲、事件和時序控制結(jié)構(gòu),在任務重可以調(diào)用其它任務和函數(shù)。與任務不同,函數(shù)具有返回值,而且至少要有一個輸入變量,而且在函數(shù)中不能使用延遲、事件和時序控制結(jié)構(gòu),函數(shù)可以條用函數(shù),但是不能調(diào)用任務。

(2)在聲明函數(shù)時,系統(tǒng)會自動的生成一個寄存器變量,函數(shù)的返回值通過這個寄存器返回到調(diào)用處。

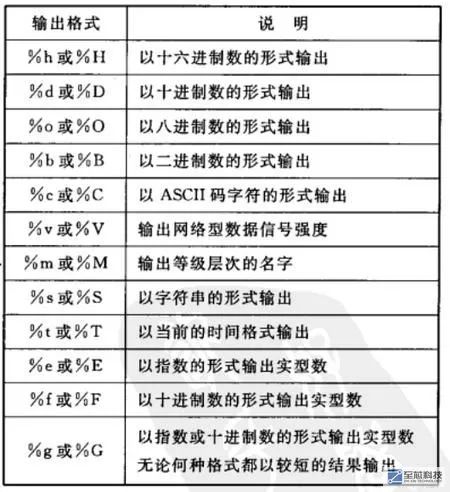

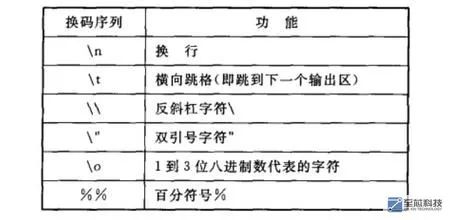

(3)函數(shù)和任務都包含在設計層次中,可以通過層次名對他們實行調(diào)用。這句話什么意思啊? 10、系統(tǒng)任務 (1)$diplay和$write任務 $display任務相當于C語言里的printf,用于輸出信息,他的基本格式$display (p0,p1,p2);意思就是把p1、p2以p1的格式輸出,至于具體格式,C語言里面講的很清楚,下面用一張圖幫大家回憶一下

此外,在display中,輸出列表中的數(shù)據(jù)的現(xiàn)實寬度總是按照自動輸出格式進行調(diào)整的。因此,我們通常在%和表示進制的符號之間加一個0來確保總是用最少的位數(shù)來表示表達式的當前值。 例如 begin r1=10; $display(“size=%d=%h”,r1,r1); $display(“size=%0d=%0h”,r1,r1); 輸出結(jié)果分別為 10,00a和10,a 所以在以后寫程序時,為了養(yǎng)成良好習慣,應該注意加上0來保證代碼的可讀性。

如果輸出的列表中含有不定值或者高阻態(tài)時,要遵循下列情況

(1)如果按10進制輸出 如果輸出列表全部為不定值,則輸出為小寫x;

如果輸出列表部分為不定值,則輸出為大寫X;

如果輸出列表全部為高阻態(tài),則輸出為小寫的z;

如果輸出列表部分為高阻態(tài),則輸出為大寫的Z;

(2)如果按十六進制或者8進制輸出

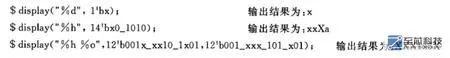

那么十六進制對應的四位或者8進制對應的3位中,如果部分是高阻態(tài)或者是不定值,那么輸出結(jié)果為大寫的Z或者X否則就輸出小寫的z或者x; 例如

(2)$monitor

系統(tǒng)任務$monitor提供了監(jiān)控和輸出參數(shù)列表中的表達式或變量值的功能,其參數(shù)列表中輸出控制格式字符串和輸出列表的規(guī)則和$display一樣,當啟動一個帶有一個或者多個的$monitor任務時,仿真器則創(chuàng)立一個仿真機制,使得每當參數(shù)列表中的表達式或值發(fā)生變化時,整個參數(shù)列表中的變量或者表達式的值都將輸出顯示,如果在同一時刻,兩個或者多個參數(shù)的值發(fā)生變化,則在這時刻只輸出顯示一次,但在$monitor任務中,參數(shù)可以是$time系統(tǒng)函數(shù),這樣參數(shù)列表中變量或者表達式的值同時發(fā)生變化的時刻可以通過標明同一時刻的多行輸出來顯示。例如

$monitoron和$monitoroff的功能就是通過打開或者關(guān)閉監(jiān)控標志來控制監(jiān)控任務$monitor的啟動和停止。這樣可以使得程序員很容易的控制$monitor什么時候執(zhí)行了。

(3)時間度量系統(tǒng)函數(shù)$time 在verilog hdl語法中有兩種時間度量系統(tǒng)函數(shù),分別是$time和$realtime,用這兩個系統(tǒng)函數(shù)可以得到當前的仿真時刻。$time可以返回一個64位的值來記錄當前的仿真時刻。 (4)$finish 系統(tǒng)任務$finish的作用是退出仿真器,返回主操作系統(tǒng),也就是結(jié)束仿真過程。格式是 $finish或者$finish(1);如果不帶參數(shù),則默認參數(shù)為1,下面是具體參數(shù)下系統(tǒng)輸出的特征信息。

0 不輸出任何信息

1 輸出當前仿真時刻和位置

2 輸出當前仿真時刻、位置和在仿真過程中所用memory及CPU時間的統(tǒng)計。

(4)系統(tǒng)任務$stop $stop任務作用是把EDA工具置成暫停模式,在仿真環(huán)境下給出一個交互式的命令操作符,將控制權(quán)交給用戶。這個任務可以帶有參數(shù)表達式,根據(jù)參數(shù)值(0、1、2)的不同,輸出不同的信息,參數(shù)值越大,輸出信息越多。

(5)系統(tǒng)任務$random

這個系統(tǒng)函數(shù)提供了一個產(chǎn)生隨機數(shù)的手段,當函數(shù)被占用時返回一個32位的隨機數(shù),它是一個帶符號的整形數(shù)。

下面是一個產(chǎn)生隨機數(shù)的例子

reg[23:0] rand;

rand=$random %60;

上面的例子產(chǎn)生一個-59到59之間的隨機數(shù),所以$random的用法是產(chǎn)生一個(-b+1)到(b-1)之間的隨機數(shù)。

下面的例子通過并位產(chǎn)生一個值在0—59之間的隨機數(shù)

reg[23:0 rand];

rand = {$random} %60; 利用這個系統(tǒng)函數(shù)可以產(chǎn)生隨機脈沖序列或?qū)挾入S機的脈沖序列,用于電路的測試。

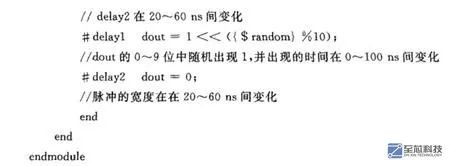

下面是個產(chǎn)生隨機脈沖序列的例子

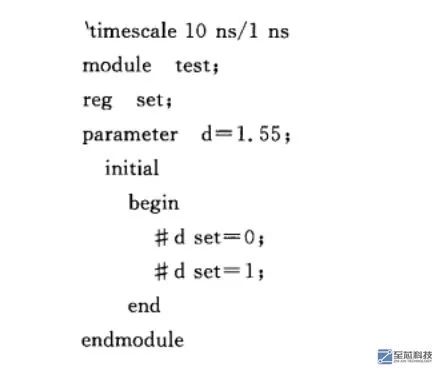

(6)關(guān)于編譯預處理 編譯預處理這部分和C語言差不多,主要用到的是`define、`include、和時間尺度`timescale `define 就是宏定義,在C語言了用的也比較多,在verilog中靈活的使用宏定義可以增加程序的可讀性,又方便修改。例如在聲明一個8位寄存器時用宏定義 `define WINDOWS 8 module reg [1:`WINDOWS] date; …… 習慣上一般宏定義的內(nèi)容用大寫字母表示,這里的WINDOWS就代表數(shù)字8,在下面的程序中調(diào)用WINDOWS時加個 `,表示調(diào)用,這樣宏定義的好處就是,在大的程序中如果想改變寄存器的大小,可以直接改數(shù)字8為16,這樣,所有的WINDOWS都變成了16,這樣改一個就可以改變所有的,給程序員帶來了方便。 對于`include,C語言里用的比較多這里就不在多提,主要是模塊化編程思想的應用,這個很重要,練好模塊化編程,可以大大提高程序的可讀性和可移植性,也使修改程序變得更加方便。 對于`timescale,就是一個時間尺度,C語言里面沒有,這里說一下。 `timescale 包括兩部分,一部分是時間單位,一部分是時間精度,下面舉個例子

在這個例子中,時間單位是10ns,時間精度是1ns,這里d=1.55,也就是說d等于1.55乘10納秒,也就是15.5納秒,再看時間精度是一納秒,四舍五入就是16納秒,所以在16納秒時,set置零,32納秒時set置一。

小結(jié) (1)、在多模塊調(diào)試的情況下,$monitor需配合$monitoron和$monitoroff來使用。

(2)、$monitor和$diplay的區(qū)別在于$monitor是連續(xù)監(jiān)視數(shù)據(jù)的變化,因而往往只要在測試模塊的initial塊中調(diào)用一次就可以監(jiān)控被測模塊中所有感興趣的信號不需要,也不能在always塊中調(diào)用$monitor.

(3)、$time常在$monitor中作時間標記

(4)、$stop 和 $finish 常用在測試模塊的initial塊中,配合時間延遲用來控制仿真的持續(xù)時間。

(5)、$random在編寫程序是非常有用的,可以用來產(chǎn)生邊沿不穩(wěn)定的波形和隨機出現(xiàn)的脈沖。正確的使用它能有效的發(fā)現(xiàn)設計中出現(xiàn)的問題。

(6)、$readman在編寫測試程序時很有用,可以用來生成給定的復雜數(shù)據(jù)流。復雜數(shù)據(jù)可以用C語言產(chǎn)生,存在文件中。用$readman取出存入存儲器,再按節(jié)拍輸出這在驗證算法邏輯電路中特別有用。

(7)、在用`timescale時要注意當多個帶不同`timescale定義的模塊包含在一起時,只有最后一個才起作用,所以屬于一個項目,但`timescale定義不同的多個模塊最好分開編譯,以免把時間單位搞混。

(8)、宏定義字符串和include引用時,不要忘記用“`”這個標號。

責任編輯:lq6

-

FPGA

+關(guān)注

關(guān)注

1646文章

22059瀏覽量

619059 -

寄存器

+關(guān)注

關(guān)注

31文章

5437瀏覽量

124685 -

仿真器

+關(guān)注

關(guān)注

14文章

1040瀏覽量

85464

原文標題:零基礎學FPGA-Verilog語法下

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

電商API集成入門:從零開始搭建高效接口

以太網(wǎng)入門:從零開始,掌握以太網(wǎng)基礎知識!

從零開始學電源

FPGA Verilog HDL語法之編譯預處理

從零開始學電路仿真Multisim與電路設計Protel技術(shù)——完整版

Verilog 測試平臺設計方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

從零開始訓練一個大語言模型需要投資多少錢?

評論