隨著系統內電源數量的增多,為了確保其安全、經濟、持續和正常的工作,對電源軌進行監測和控制變得非常重要,特別是在使用微處理器時。確定電壓軌是否處于工作范圍內,以及該電壓相對于其它電壓軌是否按照正確的時序上電或斷電,這些對于系統執行的可靠性和安全性來說都是至關重要的。例如FPGA,在向組件提供5V I/O(輸入/輸出)電壓之前,必須先施加3.3V的核心電壓,并持續至少20ms,以避免組件上電時受到損壞。對于系統的可靠性來說,滿足這樣的時序要求就像要保證組件在規定的電源電壓和溫度范圍內工作一樣至關重要。

同時,電源軌數量也在顯著增加。一些復雜的系統,如LAN(局域網絡)交換機和移動電話基站,線路卡通常會包含10路或更多電壓軌;即使是對成本敏感的消費性系統,如等離子電視,也可能具有多達15路的獨立電壓軌,其中許多電壓軌都需要進行監控和時序控制。在高階系統中,每個DSP組件會需要多達四個獨立的電源。而在更多情況下,單一系統中可能存在著大量的多電源組件,包括FPGA、ASIC、DSP、微處理器和微控制器(以及模擬組件)。

電壓監控和時序控制有時會變得極為復雜,特別是當一個系統必須設計為能夠支持上電時序控制和斷電時序控制,并能夠在工作期間的不同時間點上對不同電源軌上的所有可能故障狀況均產生多種響應時。中心電源管理控制器是解決這個難題的最佳方案。

設計風險與電源數量、組件數量和系統復雜程度成正比,外部因素也會增加風險。例如,如果在初始設計階段沒有完整地定義出主ASIC的特性,那么電源設計工程師必須用硬聯機實現電壓監控閾值和時序控制,但這些都可能會隨著ASIC技術指標的改變而產生變化。故對于任何一個中心電源系統管理器來說,易于調整電源的方法將會是非常有用的。

基本監控

圖1所示的是監控多任務電壓軌的簡單方法。其中,每路電壓軌都使用獨立的電路。電阻分壓器將電壓軌按比例降低,并為每一路電源設置一個欠壓跳變點。所有的輸出被連接在一起,產生通用電源良好訊號。更小的制程尺寸正推動核心電壓向更低的方向發展。低壓時余量的不足可能會引起預想不到的組件行為。隨著核心電壓的下降,對高精密度電壓監控器的要求將更加苛刻,如圖2所示。

圖1:基于比較器的欠壓檢測,提供通用電源良好輸出,適用于3路電源系統。

圖2:現代電子系統中需要高精密度監控器。

基本時序控制

圖3所示的是如何利用分離組件實現基本的時序控制,此處采用邏輯閾值而不是比較器。12V和5V電源軌是由其它電路產生的。為了確保系統能夠正確工作,必須導入一段時間延遲。這里是透過使用RC電路來緩慢升高與5V電源串聯的N信道FET的閘極電壓而實現的。所選用的RC值可確保FET在達到閾值電壓并導通之前能獲得足夠的延遲時間。這些電壓的上電時間也是利用RC來進行時序控制的。由于RC能驅動每個LDO的EN(使能)接腳,因此無需串聯FET。選定的RC值要確保在EN接腳上的電壓爬升到其閾值之前有足夠的延遲時間(t2,t3)。

圖3:四路電源系統的基本分離式時序控制。

這種簡單、低成本的電源時序控制方法只占用很少的電路板面積,因此適用于多種應用。這種方法適合于成本是主要考慮因素、時序要求很簡單,且時序控制電路的精確性不是十分重要的系統。

但許多情況下需要比RC延遲電路更高的精確性。此外,這種簡單的解決方案也不允許以結構化的方法處理故障(例如,一個5V電源失效最終將影響到其它電源軌)。

利用IC進行時序控制

市場上有各種各樣的電源時序控制器。有些組件能夠直接實現電源模塊的輸出,并提供多種輸出配置。有些組件內建電荷泵電壓產生器,對于需要對更高電壓軌進行時序控制、卻又缺少高壓源(如12V電源軌)的低壓系統來說,這一點特別有用,能夠驅動N信道FET的閘極。許多這類組件具有使能接腳,可以接受來自于按鈕開關或控制器的外部訊號,以便在需要時重新啟動時序控制或切斷所控制的電壓軌。

圖4所示的是如何使用電源時序控制器ADM6820和ADM1086精確且可靠地對系統中的電源軌進行時序控制。內部比較器檢測電壓軌何時會超過精密的設定電平,經過可程序的上電延遲之后,按正確時序產生輸出。閾值透過電阻比值來設定,延遲透過電容來設定。

圖4:使用監控IC對四路電源系統進行時序控制。

整合的電源系統管理

有些系統具有許多電源軌,采用這種使用大量IC,并利用電阻和電容來設置時序和閾值電平的分離解決方案會變得過于復雜、成本過高,且不能提供適當的性能。

具有八路電壓軌的系統會需要復雜的上電時序控制。每路電壓軌都要監控,以免出現欠壓或過壓故障。產生故障時,根據故障機制,需要切斷所有電源電壓,或初始化電源切斷時序。此外,必須根據控制訊號的狀態采取相應措施,并根據電源的狀態產生標志位。在具有四路或更多電源的系統中,使用集中式組件來管理電源比較可取。圖5所示的是采用這種方法的一個例子。

圖5:打印機應用中的上電與斷電時序。

集中式監測和時序控制

通常,系統中包含的電源數量越多,系統就越復雜,因此精密度限制也越嚴格。另外,在低壓狀態下,例如1.0V和0.9V,利用電阻來設定精確的閾值也變得很有挑戰性。ADM1066在最壞情況下允許輸入檢測器比較器的閾值被設定在1%范圍內,而與電壓(低至0.6V)無關,并可工作在該組件允許的整個溫度范圍內。這可以增加每個比較器的內部突波濾波和遲滯。其邏輯輸入適用于啟動上電時序控制、關閉所有電源軌,或執行其它功能。

比較器的信息被送入功能強大和靈活的狀態機核心,這些信息具有以下幾種用途。

時序控制:當最近的使能電源的輸出電壓進入到窗口中時,時間延遲被觸發,以按照上電時序接通下一個電源軌。可能需要具有多重上電與斷電時序,或具有差別較大的上電與斷電時序的復雜時序控制。

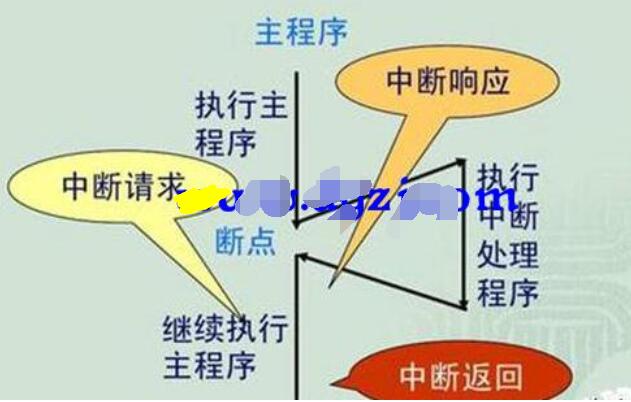

超時:如果已經使能的電源軌沒有按照預期上電,可以執行一套適當的應對措施(例如產生一個中斷訊號或關閉系統)。相較之下,純模擬的解決方案只會讓系統簡單地掛在時序中的那一點上。

監控:如果任一電源軌上的電壓超出了預設的窗口,可以根據產生故障的電源軌、故障類型和目前的工作模式,采取適當的應對措施。含有五路以上電源的系統通常都相當昂貴,因此全面的故障保護是極為重要的。

即使系統中的最高電壓只有3V,仍然可以透過內建電荷泵產生大約12V的閘極驅動電壓,允許輸出能夠直接驅動串聯的N信道FET。其它額外的輸出能夠使能或切斷DC/DC轉換器或穩壓器,使輸出內部上拉至其中一個輸入電壓或內建的穩壓電壓。輸出也可以被指定為開漏輸出。輸出可以作為狀態訊號,如電源良好或上電重置。如果需要的話,狀態LED可以直接由輸出來驅動。

電源調整

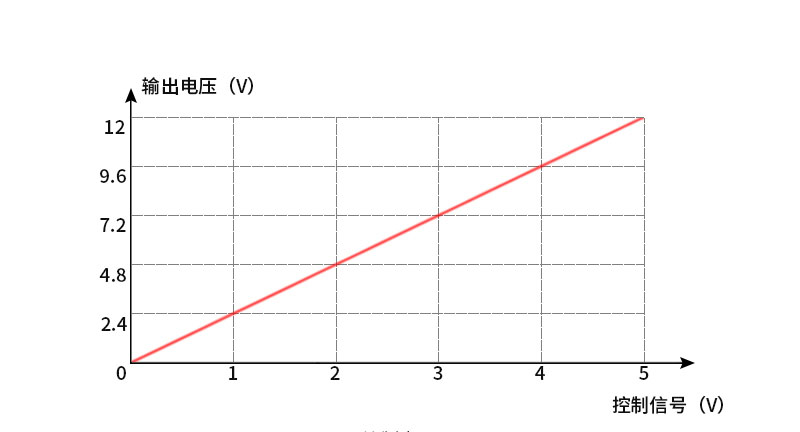

除了能夠監控多任務電壓軌并提供復雜的時序控制解決方案之外,整合電源管理組件還可以用于暫時或永久調整某些電壓軌電壓。透過調節組件上調整節點或反饋節點上的電壓,可以改變DC/DC轉換器或穩壓器的電壓輸出。組件中的DAC,可以直接控制調整/反饋節點。為了實現最大的效率,這些DAC不會在地與最大電壓間工作,而是會以標稱的調整/反饋電平為中心點,在一個相當窄的窗口中工作。如ADI的ADM1066包含一個用來測量電源電壓的12位ADC,以實現死循環電源電壓調節方案。它可以調整DAC來校準電壓輸出,使其盡可能接近目標電壓。這個死循環方案提供了一個非常精確的電源調節方法,如圖6所示。

圖6:ADI公司用于八路電源系統的集中式時序控制與監控解決方案。

這種電源調節方案有兩個主要應用。首先是電源容限的概念,也就是說,當電源處于規定的設備電源電壓范圍邊界時,測試系統對電源做出的反應。數據通訊、電信、移動電話基礎設備、服務器和儲存局域網絡設備等制造商在將其系統提供給終端客戶之前,必須進行嚴格的容限測試。

電源調節方案的第二個應用是補償系統電源波動,包括溫度改變引起的短期波動以及組件老化引起的長期波動。ADC及DAC回路可被周期性地啟動(例如每10s、30s或60s),再加上軟件校準回路,就可以使電壓保持在其應有的范圍內。

責任編輯:gt

-

電源

+關注

關注

184文章

17749瀏覽量

250581 -

電壓

+關注

關注

45文章

5611瀏覽量

115899 -

監控器

+關注

關注

1文章

269瀏覽量

26578

發布評論請先 登錄

相關推薦

調節低電壓隔離電源的方法

基于UCD3138的高整合度新一代數字電源方案

整合電源管理與轉換,簡化電源系統設計

利用可編程邏輯器件實現靈活的電源管理

調節低電壓隔離電源的方法

調節低電壓隔離式電源的方法

整合電源管理與轉換,簡化電源系統設計

通過可編程邏輯器件來實現靈活的電源管理

單片機的死循環有什么作用

基于整合電源管理組件實現死循環電源電壓調節方案

基于整合電源管理組件實現死循環電源電壓調節方案

評論