作者: Muriel Nina和Laurent Gonthier

從上個世紀70年代開始,雙向可控硅(又稱三端雙向晶閘管)一直用于控制交流負載,幾乎在所有電器上都能看到雙向可控硅。當終端設備上的電壓上升速率過快時,雙向可控硅將會自動觸發,從那時起,設計人員就必須面對雙向可控硅的這個特性。當設計對電壓快速瞬變有要求的電器時,必須考慮這個問題。

半導體易受到dV/dt變化速率的影響

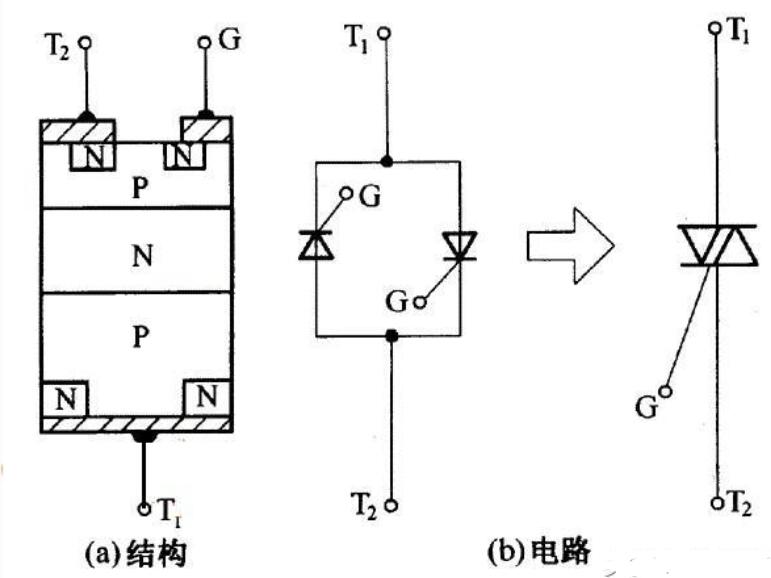

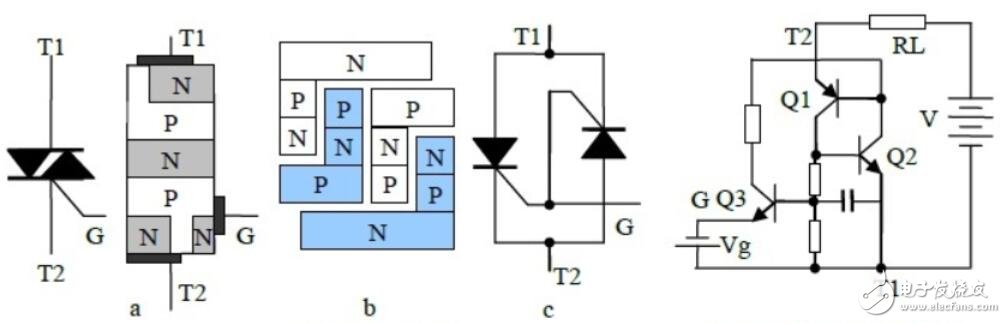

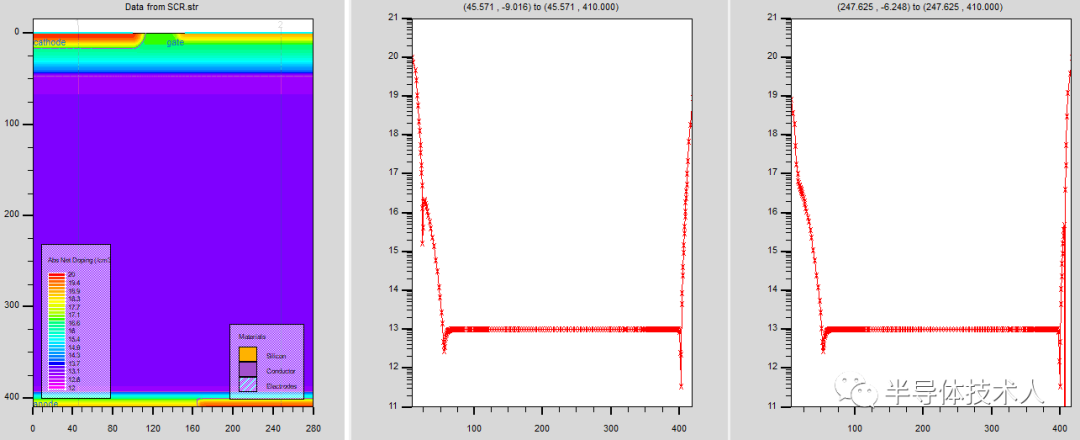

功率半導體器件由多個半導體層組成。例如,雙向可控硅是四層結構交流開關元件,每層是半個祼片,每層通過交替摻雜方法控制空穴濃度(P區)或自由電子濃度(N區),形成兩個單向可控硅。因此,雙向可控硅相當于兩個反極性并聯的單向可控硅(圖 1)。

每個PN結都會產生寄生電容,當施加斜坡電壓時,就會產生電容電流(ICAP)。電容電流可能會向IGBT或功率MOSFET等電壓控制型半導體的柵極電容充電。如果電容電壓持續升高,超過閾壓(VGS(th)或VGE(th)),器件可能會導通。即使不足以觸發器件,器件也可能進入飽和模式(如果是MOSFET)或線性模式(如果是IGBT),導致功率損耗過大和器件失效。為避免這個問題,柵極必須通過低阻抗以源極或發射極為參考點。

圖1:a)雙向可控硅結構易受dV/dt上升率影響 b) dV/dt上升率引起導通示例圖

如果dV/dt(以A1端為參考點)為正值,則電流ICAP經P1-N1結流至A1;如果dV/dt為負值,則電流ICAP經P2-N3結流至A2(如圖1所示)。假如P1或P2層電壓分別高于P1-N2或P2-N3結閾壓(即0.6 V),該電容電流就可能導致雙向可控硅導通。

在雙向可控硅產品數據手冊中,廠商給出相關器件在導通前能夠承受的最小的dV/dt上升速率。如果電壓上升速率高于這個數值,雙向可控硅可能就會導通,如圖1b所示。只要施加的電流小于器件最大輸入電流,dV/dt引起的導通不會損壞雙向可控硅。因為當雙向可控硅導通時,電流會受到負載阻抗限制,所以大多數情況下不會損壞雙向可控硅。

改進雙向可控硅的dV/dt特性

為避免當雙向可控硅輸入端上電壓變化速率過快而引起的導通問題,傳統解決方案是給雙向可控硅并聯一個阻容緩沖電路,抑制市電的dV/dt變化速率。但是,這些電路需要一個大型電容,以耐受高達400V的峰壓(連接220-240V市電)。

第二種解決方案是在柵極和陰極之間增加阻抗,即增加一個電阻器(圖1中的RG )。如圖1所示,這個解決方案只適用于正電壓dV/dt變化的情況,寄生電容電流在P1-N1結分流(見藍色虛線ICAP),防止開關被觸發。對于負電壓dV/dt情況,電容電流(圖1a中的紅色虛線)流向P2-N3結。外部器件無法分流這部分電流,因而無法改進反向dV/dt抑制功能。

用電容替代電阻(圖1中的RG )也可以解決這個問題,雖然這個辦法在SCR(可控硅整流管)中效果很好,但是不建議用于雙向可控硅,因為雙向可控硅導通時dI/dt速率很高,這個電容可能會在雙向可控硅柵極上產生過流,導致器件損毀。

為防范這種風險,可以給該電容串聯一個電阻(圖2a中的RG 和CG),這樣做的好處是使用一個低阻值的RG,同時避免了從控制電路分流過高的電流,因為只要充電,CG 相當于開路。

柵極阻容濾波器有益于提高應用抗干擾能力

家電電器必須達到電磁兼容性標準的最低要求。因為雙向可控硅通過負載直接連接市電,這類電器對IEC61000-4-4標準中的電快速瞬變(EFT)實驗所用瞬變事件特別敏感。

IEC61000-4-4實驗條件包括耦合到市電網絡的5 kHz或100 kHz電壓脈沖串。因為該實驗是在整個被測電器上進行,所以微控制器也可能受到電磁干擾。我們在實驗中只評測雙向可控硅的抗擾度,所以將其柵極直接連至其參考電極,使雙向可控硅不受其它干擾的影響(圖2)。

圖2:IEC61000-4-4測試配置

輸入變阻器用于鉗制電壓,防止擊穿導致雙向可控硅導通。假如沒有輸入變阻器,只要施加1 kV峰壓,任何雙向可控硅都會導通。我們使用一個白熾燈作為負載,以便于觀察雙向可控硅何時導通。例如,我們測試了幾款意法半導體的T系列產品(T610T-8FP, T810T-8FP, T1210T-8FP, T1610T-8FP)。每款產品的柵電流都是10 mA,都對EFT(電快速瞬變)噪聲敏感。通過圖2中的RG-CG-RG2電路,每款產品都能承受3 kV 5 Khz脈沖或2 kV 100 Khz脈沖。如果沒有這個柵極電路,連1 kV的脈沖都承受不住。RG2 對應微控制器輸出引腳的內部RDS(ON)電阻,無需增加外部電阻。

與傳統緩沖電路(圖2中的RS和CS)相比,柵極電路所能承受的電壓略高(3.6 kV 對 3.3 kV 典型值)。柵極電路只用一個16V 的小電容器就取得了400V大電容器的抗擾性能。柵極電路與緩沖電路配合,讓只使用10 mA雙向可控硅的電器取得高于6 kV的EFT抗擾性能。柵極電路能夠讓所有的雙向可控硅受益,不過,意法半導體T系列產品本身的負電壓dV/dt性能非常優異,同時再使用外部柵極電路提高正電壓dV/dt性能。

總之,用柵極濾波器代替高壓緩沖器也可以降低電路板尺寸和成本,此外,還可以濾除從市電網絡進入到控制電路的噪聲。

責任編輯:gt

-

微控制器

+關注

關注

48文章

7542瀏覽量

151316 -

半導體

+關注

關注

334文章

27290瀏覽量

218094 -

可控硅

+關注

關注

43文章

959瀏覽量

71825

發布評論請先 登錄

相關推薦

雙向可控硅控制電機,電壓波動的原因查找。

可控硅是如何工作的?如何減少開關電路中可控硅故障?

簡單的雙向可控硅正電源驅動解決方案

雙向可控硅和單向可控硅的區別

通過利用外部柵極電路提高雙向可控硅的正電壓dV/dt性能

通過利用外部柵極電路提高雙向可控硅的正電壓dV/dt性能

評論