引言

隨著計(jì)算機(jī)技術(shù)、多媒體技術(shù)以及通信技術(shù)的發(fā)展,數(shù)字視頻技術(shù)得到了越來越廣泛的應(yīng)用。在數(shù)字視頻技術(shù)的研究中,視頻數(shù)據(jù)傳輸是一個技術(shù)關(guān)鍵。本文針對視頻數(shù)據(jù)流數(shù)據(jù)量大、實(shí)時性要求高的特點(diǎn),采用流模式傳輸,將視頻采集數(shù)據(jù)通過DMA從存儲資源緊張的片內(nèi)緩存區(qū)搬運(yùn)至片外SDRAM幀緩沖區(qū),實(shí)現(xiàn)圖像的高速傳輸。

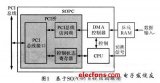

利用SoPC(System on Programmable Chip)片上可編程系統(tǒng)技術(shù),將處理器、多口SDRAM控制器、DMAC、I2C接口等模塊集成到一塊FPGA上,實(shí)現(xiàn)視頻圖像的采集、存儲、傳輸和顯示。采用自定制組件的辦法,將多口sDRAM控制器封裝成符合流模式規(guī)范的一個外設(shè)掛在Avalon總線上,非常方便DMAC進(jìn)行數(shù)據(jù)的搬運(yùn),并大大提高了系統(tǒng)的性能。

1 流模式傳輸規(guī)范

流模式傳輸是Altera Nios II嵌入式系統(tǒng)中的一種高級Avalon總線傳輸方式。這種傳輸模式在流模式主外設(shè)和流模式從外設(shè)之間建立一個開放的信道,以提供連續(xù)的數(shù)據(jù)傳輸。這個信道使得只要存在有效數(shù)據(jù)就能進(jìn)行數(shù)據(jù)的流動,主設(shè)備不需要不斷地對從外設(shè)的狀態(tài)寄存器進(jìn)行訪問。這樣使得主從端口之間的數(shù)據(jù)吞吐量達(dá)到最大,同時也避免了從外設(shè)的數(shù)據(jù)上溢或下溢。流傳輸模式最適合DMA傳輸。一個只包含流控制信號和一個計(jì)數(shù)器的*基金項(xiàng)目:深圳市科技計(jì)劃資助項(xiàng)目(200708)。DMA 控制器就可以用來在一個從外設(shè)和一個存儲器之間連續(xù)地傳輸數(shù)據(jù)。

本設(shè)計(jì)采用流傳輸模式的從端口讀傳輸和從端口寫傳輸?shù)姆椒ā亩丝谧x傳輸中,除了要設(shè)計(jì)接收主端口發(fā)出的clk信號、address信號、 read信號、chipselect信號和readdata信號之外,從外設(shè)還需要設(shè)置dataavailable信號有效來表示它能夠接收讀傳輸。從端口讀傳輸接口信號及其時序如圖1所示,由從外設(shè)發(fā)出的dataavailable有效時啟動流模式讀傳輸,數(shù)據(jù)通過DMA的搬運(yùn),開始連續(xù)不斷地由從外設(shè)流向主端口直至傳輸完成,傳輸?shù)耐V够蛑袛嘁灿蓮耐庠O(shè)來決定。同樣的道理,在寫傳輸中,要設(shè)計(jì)接收主端口發(fā)出的clk信號、address信號、 write信號等基本從端口寫傳輸信號之外,從外設(shè)則需要設(shè)置ready-fordata信號有效來表示它能夠接收寫傳輸,圖2為從端口寫傳輸接口信號及其時序。此外,讀傳輸和寫傳輸中的endofpacket信號取決于用戶設(shè)計(jì)。

2 SoPC系統(tǒng)結(jié)構(gòu)

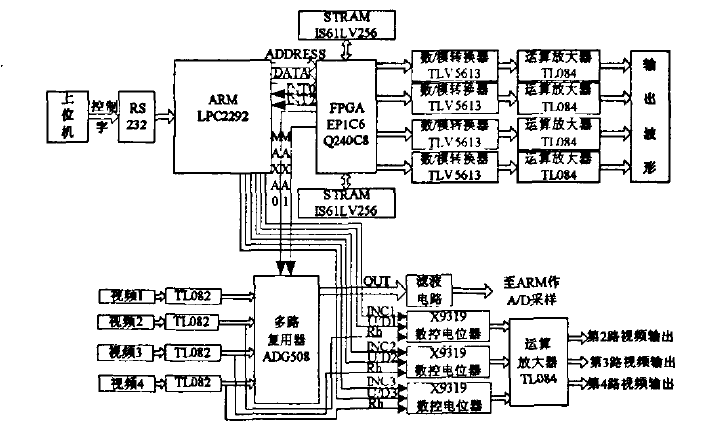

如圖3所示,SoPC系統(tǒng)以32位Nios II處理器為核心,將所有的接口模塊集成到一塊FPGA內(nèi)。其中,多口SDRAM控制器作為一個自定制外設(shè)與其他通用外設(shè)(DMA控制器、SRAM控制器、Flash接口等)一同掛在Avalon總線上,并與圖像采集模塊、VGA顯示控制模塊以及12C通信模塊等一起構(gòu)成SoPC視頻采集系統(tǒng)。本設(shè)計(jì)中,片外SDRAM容量較大,作為視頻數(shù)據(jù)源緩沖區(qū)以及顯示緩沖區(qū);片外SRAM速度快但資源有限,可用于視頻處理緩沖區(qū)。從SDRAM(數(shù)據(jù)源)到 SRAM(處理緩沖區(qū))以及從SRAM(處理緩沖區(qū))到SDRAM(顯示緩沖區(qū))的傳輸,則由DMAC采用流模式的方法來實(shí)現(xiàn)數(shù)據(jù)的搬運(yùn)。

3 流模式接口的設(shè)計(jì)

(1)四口SDRAM控制器

本系統(tǒng)采用片外SDRAM作為幀緩沖區(qū),而對SDRAM使用的關(guān)鍵在于其控制接口的設(shè)計(jì)。在SoPCBuilder集成開發(fā)軟件中,可直接使用系統(tǒng)元件庫提供的單口SDRAM控制器,但是該控制器IP核無法滿足采集、傳輸和顯示同時進(jìn)行的要求。因此,自定制了一個四口SDRAM控制器。如圖4所示,該四口SDRAM控制器中的2個端口用于流模式的讀和寫,另外2個端口一個作為圖像數(shù)據(jù)源輸入,還有一個作為VGA顯示輸出。

由于數(shù)據(jù)采集、VGA監(jiān)控、流模式傳輸數(shù)據(jù)流速度與SDRAM控制器存取不匹配,因此,對于這四口中的任何一個口,都用FIFO來對數(shù)據(jù)進(jìn)行緩沖,以協(xié)調(diào)數(shù)據(jù)的同步而不至于錯位。而每個FIFO都有個水位檢測器,當(dāng)水位到半滿時根據(jù)仲裁電路判斷的優(yōu)先級啟用SDRAM讀寫命令,以100 MHz(系統(tǒng)時鐘頻率50 MHz)的頻率根據(jù)用戶給定的地址信號進(jìn)行批量數(shù)據(jù)的存取,從而滿足了四口并用的要求。該SDRAM控制器的內(nèi)部結(jié)構(gòu)如圖5所示。

(2)數(shù)據(jù)流的傳輸

用DMA來搬運(yùn)數(shù)據(jù)不僅速度非常快,而且整個操作不需要CPU的干預(yù),可把CPU從繁重的數(shù)據(jù)傳送中解放出來。DMA控制器將數(shù)據(jù)從源地址空間傳輸?shù)侥康牡刂房臻g,數(shù)據(jù)源或目的地可以是Avalon從外設(shè)(一個固定地址),也可以是存儲器的一段地址范圍。對DMA控制器的使用,需要Nios II處理器對源地址和目的地址進(jìn)行初始化配置,同時也要預(yù)先給定傳輸長度以及傳輸模式等。本系統(tǒng)使用了Altera公司提供的HAL DMA設(shè)備驅(qū)動程序。該驅(qū)動程序把DMA傳輸抽象成兩種數(shù)據(jù)通道:數(shù)據(jù)發(fā)送通道和數(shù)據(jù)接收通道,如圖6所示。

如此,便可通過Nios II用軟件控制DMA以流模式進(jìn)行數(shù)據(jù)傳輸,具體搬運(yùn)的數(shù)據(jù)路徑如圖7所示。其中緩沖區(qū)1是采集數(shù)據(jù)的源緩沖區(qū)。緩沖區(qū)2是傳輸后顯示緩沖區(qū),緩沖區(qū)3是處理緩沖區(qū)。對視頻的處理不是本文討論的范圍,故這里只將原圖像傳回。

(3)流模式接口的硬件設(shè)計(jì)

對流模式接口的硬件設(shè)計(jì)實(shí)際上就是把上述四口SDRAM控制器封裝成一個Avalon自定制組件,且這個組件的其中兩端口滿足流模式讀寫規(guī)范。根據(jù)Avalon總線流模式傳輸規(guī)范,該自定制外設(shè)需要設(shè)置dataavailable、readyfordata信號有效表示已經(jīng)準(zhǔn)備好流模式傳輸,同時接收主設(shè)備發(fā)出clk、read/write、chipse-lect等信號,并根據(jù)這些信號對上述FIFO進(jìn)行數(shù)據(jù)的存取。以下給出了該接口的部分 Verilog HDL代碼(u9、u10為FIFO的端口信號連接情況):

(4)數(shù)據(jù)路徑的軟件控制

作為自定義的組件,除了硬件接口以外,還需要編寫驅(qū)動層軟件(固件)。SoPC Builder生成的外設(shè)信息都保存在system.h文件里,固件的編寫主要是基于這個文件信息。

對數(shù)據(jù)路徑的控制是通過Nios II軟件配置DMA控制器來實(shí)現(xiàn)的。這種軟硬件協(xié)同設(shè)計(jì)的辦法,既兼顧了傳輸?shù)乃俣扔旨骖櫫藬?shù)據(jù)路徑的靈活性。對數(shù)據(jù)傳輸?shù)脑O(shè)置,首先需要在SoPC Builder中設(shè)定DMA控制器的read_master和write_master,也就是數(shù)據(jù)搬運(yùn)的源和目的地。具體設(shè)置如圖8所示。

除此之外,還要在軟件上具體設(shè)置DMA傳輸?shù)脑吹刂贰⒛康牡刂贰鬏旈L度以及傳輸模式等。這里給出部分調(diào)用HAL DMA驅(qū)動的軟件代碼:

4 系統(tǒng)測試

(1)流模式接口仿真

用Quartus II自帶的Signaltap II邏輯分析儀對自定制的流模式接口信號進(jìn)行觀察,圖9為相關(guān)信號波形。經(jīng)過分析,此波形與流模式的傳輸規(guī)范吻合。

(2)系統(tǒng)測試

整個SOPC系統(tǒng)在Altera DEl的Cyclone II FPGA上實(shí)現(xiàn)。采用友晶科技公司的攝像頭進(jìn)行圖像數(shù)據(jù)源輸入,用VGA顯示終端進(jìn)行輸出觀察,用DEl設(shè)計(jì)平臺和該SoPC視頻采集系統(tǒng)對某一場景進(jìn)行拍攝截圖。結(jié)果表明,該流模式接口工作流暢。

5 總結(jié)

本設(shè)計(jì)采用以Nios II為核心的SoPC系統(tǒng)實(shí)現(xiàn)了視頻采集信號的流模式傳輸,并將其做成一個自定義外設(shè),非常方便重復(fù)利用。另外,利用了DMAC硬件實(shí)現(xiàn)傳輸,且數(shù)據(jù)采集、存儲和顯示全硬件實(shí)現(xiàn),速度非常快;同時,可以將SRAM作為圖像處理緩沖區(qū),將處理后的圖像讀回,這樣就搭建了一個圖像處理的硬件系統(tǒng)。當(dāng)需要實(shí)現(xiàn)某種視頻處理的算法時,只需要修改圖像處理模塊,再放進(jìn)系統(tǒng)中就可以實(shí)現(xiàn)。

責(zé)任編輯:gt

-

控制器

+關(guān)注

關(guān)注

112文章

16332瀏覽量

177803 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7488瀏覽量

87849 -

多媒體

+關(guān)注

關(guān)注

0文章

496瀏覽量

36975

發(fā)布評論請先 登錄

相關(guān)推薦

如何設(shè)計(jì)數(shù)字視頻監(jiān)控系統(tǒng)?

數(shù)字電視信號傳輸采集系統(tǒng)怎么實(shí)現(xiàn)?

如何采用以Nios II為核心的SoPC系統(tǒng)實(shí)現(xiàn)視頻采集信號的流模式傳輸?

無線視頻采集系統(tǒng)的硬件設(shè)計(jì)

基于SOPC的數(shù)字視頻監(jiān)控系統(tǒng)設(shè)計(jì)

基于SoPC的自感知運(yùn)動圖像采集系統(tǒng)設(shè)計(jì)

SOPC基礎(chǔ)上的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

基于IP網(wǎng)絡(luò)的實(shí)時視頻采集系統(tǒng)

基于SOPC心電信號的采集與處理

SOPC實(shí)現(xiàn)的PCI總線高速數(shù)據(jù)傳輸系統(tǒng)

基于SOPC的視頻采集及傳輸系統(tǒng)的設(shè)計(jì)

關(guān)于Rogowski線圈的電流信號采集與光纖傳輸系統(tǒng)的研究

基于Nios軟核的SoPC系統(tǒng)硬件設(shè)計(jì)

如何使用ARM和WINCE進(jìn)行USB視頻采集與傳輸系統(tǒng)的設(shè)計(jì)

如何使用FPGA和ARM設(shè)計(jì)和實(shí)現(xiàn)多路視頻采集系統(tǒng)

基于SoPC系統(tǒng)和DMAC硬件實(shí)現(xiàn)視頻采集信號傳輸系統(tǒng)的設(shè)計(jì)

基于SoPC系統(tǒng)和DMAC硬件實(shí)現(xiàn)視頻采集信號傳輸系統(tǒng)的設(shè)計(jì)

評論