作者:李志剛,王明泉,任少卿,楊靜

1 引言

隨著中國機器人產(chǎn)業(yè)的迅猛發(fā)展,據(jù)預(yù)測到2010年,市場容量將超過93.1億人民幣。智能移動機器人是在室外環(huán)境中,將視頻圖像采集回來之后,按照預(yù)先給定的目標(biāo)任務(wù),結(jié)合已知的地理信息做出路徑規(guī)劃,在行駛的過程中能夠不斷感知和判斷周圍的環(huán)境信息,自主地做出各種決策,隨時調(diào)整自身的行駛狀態(tài)并執(zhí)行相應(yīng)的動作和操作。在這個過程中,視頻采集質(zhì)量的好壞將直接影響整個系統(tǒng)的運行,是進行后續(xù)數(shù)字圖像處理的前提條件。因此,必須有高性能的硬件設(shè)備和高質(zhì)量的算法作為基礎(chǔ),實時視頻采集才成為可能。本文設(shè)計并實現(xiàn)了基于FPGA的嵌入式實時視頻采集系統(tǒng)。該系統(tǒng)體積小,功耗低,速度快,適應(yīng)性好,能夠滿足智能移動機器人視頻信號處理系統(tǒng)的需求。

2 系統(tǒng)基本原理

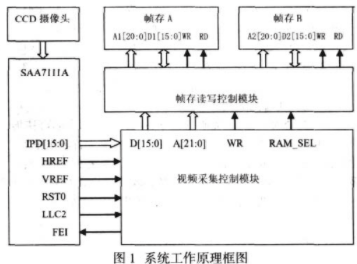

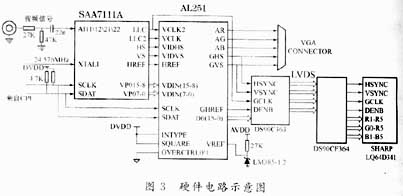

圖1為系統(tǒng)工作原理框圖,整個系統(tǒng)所需各種芯片的電路連接如下圖所示,由CCD攝像頭輸出模擬視頻信號,經(jīng)過視頻解碼芯片SAA7111A進行視頻預(yù)處理(鉗位、放大、A/D轉(zhuǎn)換、同步分離等)后輸出圖像數(shù)字信號IPD、行同步信號HREF、場同步信號VREF、奇偶場標(biāo)志信號RST0和13.5MH像素時鐘信號LLC2去驅(qū)動FPGA,從而產(chǎn)生正確的圖像采集時序和存儲地址,并將采集的圖像存儲到雙口RAM中。整個系統(tǒng)由視頻采集控制和幀存讀寫控制兩個核心模塊組成,它們的功能都由FPGA來實現(xiàn)。雙口RAM分為幀存A和幀存B兩個存儲區(qū)域,實現(xiàn)乒乓式的讀寫操作,能夠完成圖像的實時采集。SAA7111A的配置程序和FPGA采集控制程序存儲在FLASH中,系統(tǒng)上電工作時加載。

圖1 系統(tǒng)工作原理框圖

3 圖像采集系統(tǒng)的構(gòu)成

3.1 視頻信號

視頻信號中除了包含圖像信號之外,還包括了行同步信號、行消隱信號、場同步信號(幀同步信號)、場消隱信號以及槽脈沖信號、前均衡脈沖、后均衡脈沖等。因而,對視頻信號進行A/D轉(zhuǎn)換的電路也非常復(fù)雜。Philips公司將這些非常復(fù)雜的視頻A/D轉(zhuǎn)換電路集成到了一塊芯片內(nèi)。從而生產(chǎn)出功能強大的視頻輸入處理芯片SAA7111A,為視頻信號的數(shù)字化應(yīng)用提供了極大的方便。

3.2 SAA7111A 性能及工作協(xié)議

SAA7111A是PHILIPS公司的一種增強型視頻輸入處理器芯片,它集A/D與解碼功能于一身,片內(nèi)還附有鎖相、自動鉗位控制、時鐘自動增益產(chǎn)生、多制式解碼等電路,另外還可對亮度、對比度和飽和度進行控制[2]。既支持PAL電視制式,又支持NTSC電視制式。SAA7111A內(nèi)部含有I2C接口,可簡潔的通過I2C總線對SAA7111A的工作方式進行設(shè)定。SAA7111A的場同步信號VREF、行同步信號HREF、奇偶場信號RST0、像素時鐘信號LLC2都由引腳直接引出,從而省去了以往時鐘同步電路的設(shè)計,其可靠性和方便性有了很大的提高。

圖2所示為SAA7111A的功能方框圖。從SAA7111A的四個模擬輸入端AI11,AI12, AI21, AI22輸入的視頻圖像信號,經(jīng)模擬處理后,一路經(jīng)A/D轉(zhuǎn)換器后產(chǎn)生數(shù)字色度信號和亮度信號,分別進行亮度信號處理和色度信號處理。亮度信號處理的結(jié)果一路送到色度信號處理器,進行綜合處理,產(chǎn)生Y和UV信號,經(jīng)格式化后從VPO(16位)輸出;另一路進入同步分離器,經(jīng)數(shù)字PLL產(chǎn)生相應(yīng)的行和場同步信號HS和VS,同時PLL驅(qū)動時鐘發(fā)生器,產(chǎn)生與HS鎖定的時鐘信號LLC和像素時鐘信號LLC2。所有這些功能均是在I2C總線控制下完成的,其中SCL為串行時鐘信號,SDA為串行數(shù)據(jù)信號。

基金項目:中國博士后科學(xué)基金資助項目(2005038095);山西省自然科學(xué)基金資助項目(20051043);中北大學(xué)科學(xué)基金資助項目。

圖2 SAA7111A功能方框圖

SAA7111A的主要特點:

可編程選擇四路視頻輸入的一路或兩路,組成不同的工作模式,在其內(nèi)部有兩路模擬視頻信號處理通道,可進行靜態(tài)增益控制或自動增益控制,還有兩路模數(shù)轉(zhuǎn)換器;

可對芯片編程進行自電平控制、抗混疊濾波、梳狀濾波;

場頻50Hz或60Hz自動檢測,并在PAL和NTSC制之間自動切換;

能對不同輸入制式的亮度信號和色度信號進行處理,并實現(xiàn)亮度、色度和飽和度的片內(nèi)控制;

提供兩種數(shù)據(jù)方式供選擇,這兩種數(shù)據(jù)方式分別是RGB和YUV,可靈活輸出不同的數(shù)字圖像數(shù)據(jù)格式,主要有:4:1:1的YUV格式(12bit ), 4:2:2的YUV格式(16bit), 4:2:2的YUV格式[CCIR-656](8bit), 5:6:5的RGB格式(16bit)和8:8:8的RGB格式(24bit);

SAA7111A的工作模式由其內(nèi)部的控制寄存器決定,需根據(jù)不同的視頻標(biāo)準(zhǔn)來配置相應(yīng)的內(nèi)部寄存器,即初始化。用戶根據(jù)I2C 總線協(xié)議,將需要的控制字寫入控制地址即可對SAA7111A進行相應(yīng)的控制。這些控制包括:圖像數(shù)據(jù)輸出格式、色彩、明暗、飽和度及各種參考信號的輸出。I2C總線傳送數(shù)據(jù)的基本時序如圖3所示。

圖3 I2C總線的基本時序

總線上的數(shù)據(jù)傳輸可以是讀或?qū)憙煞N方式,其寫格式為:

![]()

其中:S為總線起始信號;Slave Address W為被控器SAA7111的尋址字節(jié);A為被控器應(yīng)答信號;SubAddres為SAA7111控制寄存器的地址;Data(NB)即控制寄存器的配置參數(shù)為總線終止信號。

3.3 FPGA的采集控制原理

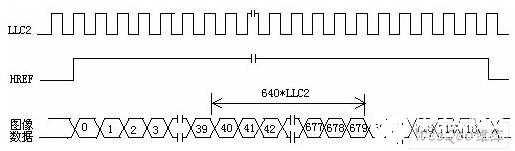

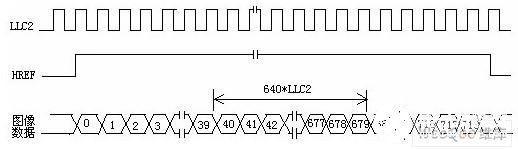

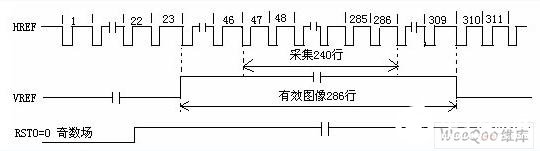

SAA7111A的輸出時鐘信號包括LLC(27MHz)和LLC2(13.5MHz),其中LLC2為像素時鐘頻率,每一時鐘對應(yīng)一個16位像素輸出。行參考同步信號HREF,高電平表示一行的有效像素,為720個LLC2周期。場參考同步信號VREF高電平時表示輸出是有效行圖像,單場是286行;低電平期間為場消隱信號,是26個行周期。RTSO=1時表示輸出為奇數(shù)場,RTSO=0時為偶數(shù)場。輸入信號FEI為輸出使能信號,為0時允許數(shù)據(jù)輸出,為1時數(shù)據(jù)輸出處于高阻狀態(tài)。圖4,5分別為采集一行和奇數(shù)場圖像的信號時序圖。

圖4 SAA7111A采集一行圖像的時序圖

啟動采集前必須對SAA7111A內(nèi)部的32個寄存器寫入相應(yīng)的值。在采集的過程中,僅采集奇場圖像信號而不采集偶場圖像信號。因為只采集奇場信號也能得到穩(wěn)定的圖像,而可以利用偶場圖像時間等待處理圖像。對有效像素、無效像素、有效行和無效行進行計數(shù),產(chǎn)生RAM的地址、讀寫、選通等控制信號,均由FPGA完成。由于只采奇場圖像,行數(shù)也減少為原來的一半,為286行,前后各去掉23行,取中間240行。當(dāng)RTSO為高電平且VREF上升沿到來時,標(biāo)志奇數(shù)場開始,啟動無效行計數(shù)器對HREF信號進行計數(shù),計滿前23行后,啟動有效行計數(shù)器,置COUT信號為高電平,且在水平同步信號VREF=1、垂直同步信號HREF=1、奇偶場信號RTSO=1時,啟動無效像素計數(shù)器,對LLC2二分頻后的像素時鐘信號進行計數(shù)。LLC2二分頻后頻率降為6.75MHz,每行像素點由原來的720點,減少為360點,將其截頭去尾,前后各去掉20個像素,取一行中間的320個像素點,即得到分辨率為320 X 240的一幀圖像。當(dāng)無效像素計數(shù)器計滿前20后,啟動有效像素計數(shù)器開始計數(shù),并將數(shù)據(jù)緩沖器打開,每計一次數(shù),地址發(fā)生器加1,產(chǎn)生地址信號,讀寫信號WR,選通信號RAM_SEL,當(dāng)一幀圖像寫完后,置FLAG信號為低,觸發(fā)中斷信號,以便處理器處理圖像。值得注意的是,利用FPGA可以很靈活地控制存入RAM存儲器中的圖像數(shù)據(jù)量。這里將圖像分辨率設(shè)計為320 X 240,實際應(yīng)用中,可以根據(jù)需要靈活設(shè)置。

圖5 SAA7111A奇數(shù)場采集的時序圖

4 結(jié)束語

本文作者創(chuàng)新點:該系統(tǒng)能夠完成對視頻信號的采集,適應(yīng)性極強的FPGA主要用于控制圖像信號的采集,F(xiàn)PGA除了完成對SAA7111A配置以外,還完成圖像提取處理、圖像存儲地址產(chǎn)生器等功能。由于FPGA的在線可編程特性使該系統(tǒng)變得更加靈活。此外,成熟的編譯環(huán)境和FPGA與SAA7111A簡單的外圍電路大大縮短了開發(fā)和調(diào)試的周期。在未來的FPGA中還可以加入圖像預(yù)處理流程,縮短后續(xù)處理時間,因此具有較高的推廣價值。實驗表明,系統(tǒng)速度快、可靠性高、實時性好,在視頻采集和圖像處理方面有著很好的應(yīng)用前景。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423155 -

機器人

+關(guān)注

關(guān)注

211文章

28380瀏覽量

206918

發(fā)布評論請先 登錄

相關(guān)推薦

用SAA7111A設(shè)計模擬視頻轉(zhuǎn)換接口

用SAA7111A設(shè)計模擬視頻轉(zhuǎn)換接口

如何去實現(xiàn)一種實時圖像采集系統(tǒng)的設(shè)計?

怎么實現(xiàn)PDP中的模擬視頻數(shù)字化電路的設(shè)計?

saa7111中文資料

可編程視頻信號輸入處理器SAA7111

視頻解碼技術(shù)中I2C總線控制核的實現(xiàn)

基于SAA7111A的模擬視頻轉(zhuǎn)換接口設(shè)計

基于DM642的SAA7113H 視頻采集模塊的設(shè)計

用SAA7111A設(shè)計模擬視頻轉(zhuǎn)換接口

基于SAA7115的視頻信號傳輸系統(tǒng)設(shè)計

基于視頻解碼芯片SAA7111A和FPGA實現(xiàn)實時視頻采集系統(tǒng)的設(shè)計

基于視頻解碼芯片SAA7111A和FPGA實現(xiàn)實時視頻采集系統(tǒng)的設(shè)計

評論