1. 引言

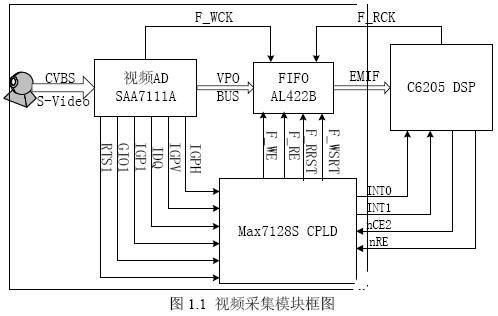

對(duì)于用于視頻圖像處理的DSP來說,由于前端的A/D 采集速度較低,一般為了減少DSP 的開銷,在視頻采集A/D 和DSP之間接入先進(jìn)先出存儲(chǔ)器(FIFO) 作為緩沖。

基于先進(jìn)先出存儲(chǔ)器(FIFO) 的多樣性,一般在視頻采集與微處理器模塊之間很少提供無縫接口。傳統(tǒng)的方法是用簡(jiǎn)單的邏輯電路實(shí)現(xiàn)很少一部分接口控制,大多數(shù)是通過軟件來實(shí)現(xiàn),雖然軟件設(shè)計(jì)靈活性比較大,但是對(duì)軟件設(shè)計(jì)者提出很高的要求; 一般來說使用的都是線存的FIFO,這種FIFO 的存儲(chǔ)量比較少,會(huì)花費(fèi)CPU 很大的開銷。

本文實(shí)現(xiàn)了一種在采集A/D 模塊、專用視頻FIFO 以及DSP 微處理使用CPLD 作為純硬件控制的方案。使用這種方案的創(chuàng)新點(diǎn)是首先因?yàn)槭褂玫氖菐鎯?chǔ)器FIFO,存儲(chǔ)一幀或者一場(chǎng)視頻數(shù)據(jù),這樣可以大大減輕DSP的開銷,提高DSP 的效率,從而更好的提高視頻處理的實(shí)時(shí)性;其次因?yàn)榻涌谶壿嫳容^復(fù)雜,一般用軟件實(shí)現(xiàn)起來比較困難,使用可編程CPLD實(shí)現(xiàn)全部的硬件接口邏輯,減少軟件設(shè)計(jì)的難度,減少DSP 的開銷。同時(shí)可以發(fā)揮CPLD 現(xiàn)場(chǎng)可編程的特點(diǎn),可以像軟件一樣更改; 最后可以作為一個(gè)集成的通用硬件采集模塊。

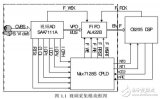

本文實(shí)現(xiàn)的是基于TI TMS320C6x 的DSP的視頻采集壓縮卡的A/D采集模塊以及接口控制模塊。在采集模塊主要功能是將從CCD 攝像頭輸入的模擬視頻信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),普通CCD攝像頭的輸出是NTSC 制式的復(fù)合全電視信號(hào)CVBS 信號(hào),通過SAA7114H TV解碼芯片將模擬TV 信號(hào)解碼,轉(zhuǎn)換為符合ITU-R BT.601 標(biāo)準(zhǔn)的數(shù)字視頻信號(hào),并且由CPLD 控制模塊將數(shù)據(jù)存儲(chǔ)到專用的視頻FIFO芯片,中斷DSP 讀取數(shù)據(jù)處理。

具體的信號(hào)控制見圖1.1。

2. 模塊介紹

2.1. 視頻采集模塊

采集模塊采用PHILIPS 公司的視頻A/D 芯片SAA7114H,該專用視頻A/D 具有6 路模擬視頻輸入,兩個(gè)模擬預(yù)處理通道,并且抗混濾波、梳狀濾波都被集成到芯片內(nèi)部,這樣對(duì)于硬件設(shè)計(jì)帶來了極大的方便。同時(shí)場(chǎng)同步信號(hào)IGPV,行同步信號(hào)IGPH,有效圖像數(shù)據(jù)輸出信號(hào)IDQ,時(shí)鐘輸出信號(hào)ICLK都有管腳直接引出,這樣省去了以往的時(shí)鐘同步電路的設(shè)計(jì),可靠性也有所提高。系統(tǒng)內(nèi)部鎖相環(huán)技術(shù)的集成使得可靠性和設(shè)計(jì)復(fù)雜度都有極大的降低。SAA7114H 的配置支持I2C,可以通過DSP的通用I/O 口軟件模擬I2C總線。

從圖2可以看出整個(gè)過程是在ICLK在上升沿觸發(fā),在 IDQ 有效的情況下傳輸?shù)臄?shù)據(jù)有效,數(shù)據(jù)輸出的格式為(下為奇數(shù)場(chǎng)的一行數(shù)據(jù)掃描)

FF00 0080 U0Y0,V0Y1,U1Y2,V1Y3,…………,U319Y638,V320Y639

其中FF00 和0080 是奇數(shù)場(chǎng)標(biāo)志位。

當(dāng)輸出IGPH 有效表明為一行數(shù)據(jù)的掃描,當(dāng)IGPH無效的情況下,表明數(shù)據(jù)在回掃。從圖3可以看出當(dāng)IGPV 有效說明是一場(chǎng)數(shù)據(jù)的掃描,當(dāng)為無效時(shí),說明為一場(chǎng)數(shù)據(jù)結(jié)束。通過這幾個(gè)狀態(tài)信號(hào)的輸出,以及其它標(biāo)志信號(hào)可以對(duì)行數(shù)據(jù)和場(chǎng)數(shù)據(jù)同步進(jìn)行控制。具體見圖2.1(信號(hào)一行掃描輸出狀態(tài)) 和圖2.2(信號(hào)一場(chǎng)掃描輸出狀態(tài))。

圖2.1 信號(hào)輸出狀態(tài)( 一行掃描)

圖2.2 信號(hào)輸出狀態(tài)( 一場(chǎng)掃描)

2.2. 視頻緩沖模塊FIFO

AL422B 是Averlogic 公司的專用視頻的FIFO,最大存儲(chǔ)為384K 8bits,同時(shí)支持VGA,CCIR,NTSC,PAL 等視頻制式,兩端獨(dú)立的讀寫操作,支持不同速率的讀寫。根據(jù)CCIR.601協(xié)議,一場(chǎng)圖像數(shù)字化后最大的數(shù)據(jù)量是220K 16bit,因此,采用的AL422B 足夠可以容納完整的一場(chǎng)視頻圖像的數(shù)據(jù)量。采用這種大的FIFO 的設(shè)計(jì)可以降低DSP 對(duì)視頻FIFO 讀寫控制時(shí)序的復(fù)雜度,使整個(gè)視頻圖像處理流程簡(jiǎn)捷,同時(shí)減少控制信號(hào)。

2.3. CPLD控制模塊

該模塊的組成主要是一片Altera 公司的CPLD 芯片EPM7128STC100,其主要功能是提供DSP 的EMIF 接口與視頻FIFO 相連時(shí)所需的一些額外的輔助邏輯(glue logic)。另外一個(gè)重要的功能是通過檢測(cè)SAA7114H 輸出的同步信號(hào)來生成DSP 中斷,通知DSP 讀取視頻FIFO 中已滿的一場(chǎng)圖像數(shù)據(jù)。(視頻FIFO AL422B 的容量為384K 8bits,系統(tǒng)中使用兩片并聯(lián)成16bits的接口寬度,整個(gè)視頻FIFO可以一次存放一幀的視頻數(shù)據(jù)。)

CPLD通過SAA7114H的輸出狀態(tài)信號(hào)以及TMS320C6x DSP的相應(yīng)輸出控制信號(hào)生成FIFOAL422B 的控制信號(hào)。具體為:

根據(jù)SAA7114H輸出的VPO 總線同步信號(hào),控制將輸出的數(shù)字視頻信號(hào)寫入到FIFO 中。

檢查到SAA7114H輸出的場(chǎng)同步信號(hào)后(表明FIFO 中已經(jīng)存滿一場(chǎng)圖像數(shù)據(jù)),向DSP 發(fā)出INT 信號(hào),通知其開始讀取FIFO 中的圖像數(shù)據(jù)。同時(shí)將FIFO 的寫入指針復(fù)位到地址0x0000處。

根據(jù)SAA7114H 的兩個(gè)輸出信號(hào)IGP1 和RTS1,判定當(dāng)前視頻AD輸出的視頻數(shù)據(jù)是奇數(shù)場(chǎng)還是偶數(shù)場(chǎng),同時(shí)發(fā)出不同的INT中斷來通知DSP。

控制DSP 讀取FIFO 中圖像數(shù)據(jù)的讀寫時(shí)序,當(dāng)讀完一場(chǎng)數(shù)據(jù)后,將FIFO 的讀出指針復(fù)位到地址0x0000 處。

控制FIFO 的寫時(shí)鐘與讀時(shí)鐘,并且使得寫時(shí)鐘與SAA7114H的輸出時(shí)鐘保持同步,使得讀時(shí)鐘與DSP 的外部分頻后的時(shí)鐘保持同步。

圖2.4 FIFO 寫時(shí)序控制

圖2.5 FIFO 讀時(shí)序控制

圖2.6 CPLD 控制寫時(shí)序的狀態(tài)機(jī)

從FIFO的寫時(shí)序圖和讀時(shí)序可以看到,當(dāng)/WE和/RE(兩者都是低電平有效)為高電平的第一個(gè)周期,芯片仍然進(jìn)行寫入和讀出操作,而下一個(gè)周期才進(jìn)入掛起狀態(tài)。同樣,當(dāng)/WE和/RE由高電平變?yōu)榈碗娖綍r(shí),也是要延后一個(gè)時(shí)鐘周期才能發(fā)生改變。這種特性造成在設(shè)計(jì)SAA7114H向FIFO寫入時(shí)序的時(shí)候,需要提前一個(gè)周期確定下一個(gè)數(shù)據(jù)是否為有效數(shù)據(jù)。CPLD程序中通過檢測(cè)IGP0(配置為SAA7114H I-port端口的Buffer almost empty flag) 來實(shí)現(xiàn)這點(diǎn)。利用邏輯分析儀測(cè)出整個(gè)寫入時(shí)序?yàn)閳D2.8。

在讀控制中主要是產(chǎn)生用于DSP 中斷的外部使能,中斷DSP 讀取FIFO的數(shù)據(jù),同時(shí)還要通知DSP 讀取的是奇數(shù)場(chǎng)的數(shù)據(jù)還是偶數(shù)場(chǎng)的數(shù)據(jù)。FIFO 的讀時(shí)序圖上可以看出如果F_OE 為低電平,這F_RE 變高后(F_OE 和F_RE 都是低電平有效),F(xiàn)IFO 的輸出仍然保存原來的值,而不是進(jìn)入高阻狀態(tài)。CPLD 控制程序中正是利用這點(diǎn)來實(shí)現(xiàn)DSP對(duì)FIFO 的讀寫時(shí)序的匹配以及保證DMA 傳輸在被DSP 中斷后不會(huì)出錯(cuò)。DSP 的FIFO 的讀取采用32 位的異步接口,8個(gè)DSP的時(shí)鐘周期(注意: 采用的是DSP 的主頻,不是總線頻率ClockOut2) 實(shí)現(xiàn)一次對(duì)FIFO 的讀寫。具體設(shè)置參考EMIF 總線初始化部分。CPLD通過將F_RE 置高,延長(zhǎng)FIFO數(shù)據(jù)的輸出時(shí)間來匹配整個(gè)DSP 的讀取時(shí)序。利用邏輯分析儀測(cè)得FIFO 的讀取時(shí)序?yàn)閳D9。

根據(jù)整個(gè)控制過程的邏輯和相應(yīng)器件的讀寫時(shí)序,可以將整個(gè)FIFO 的控制過程分為寫入控制和讀出控制兩個(gè)部分,在寫入控制中用了4個(gè)有限狀態(tài)機(jī)來實(shí)現(xiàn),它們分別是IDLE,WEN0,WEN1,WEN2。根據(jù)狀態(tài)機(jī)的圖,采用硬件描述語言VHDL 實(shí)現(xiàn)了對(duì)CPLD 的邏輯的設(shè)計(jì)、綜合和仿真。邏輯綜合采用Synplicit7.2 公司專門針對(duì)CPLD/CPLD 的邏輯綜合工具。該軟件帶有Altera公司的綜合模塊庫(kù),可以針對(duì)Altera公司的CPLD 器件對(duì)邏輯綜合后的結(jié)果進(jìn)行優(yōu)化和改進(jìn),其中寫狀態(tài)機(jī)綜合后的電路原理圖為圖2.7。

對(duì)于邏輯設(shè)計(jì)的仿真時(shí)序驗(yàn)證工作重要采用ALDEC 公司的仿真工具Active-HDL4.2,然后加入綜合工具生成的標(biāo)準(zhǔn)時(shí)延文件(SDF文件),通過仿真結(jié)果的驗(yàn)證,說明CPLD 的邏輯設(shè)計(jì)是符合FIFO 讀寫控制模塊的功能要求的。最后綜合的邏輯結(jié)果通過Altera 公司的MAXplus10軟件,采用ByteBlaster 電纜下載到CPLD 芯片中。

3. 實(shí)驗(yàn)結(jié)果:

圖3.1 是采用QCIF(176 144) 格式的視頻圖像,壓縮編碼算法采用M-JPEG2000標(biāo)準(zhǔn)。其中前一幅是無損壓縮恢復(fù)的結(jié)果圖,后一幅為有損壓縮。相應(yīng)的壓縮編碼指標(biāo)如表3.1 所示。

表 3.1

從上面表3.1 的結(jié)果可以看出,整個(gè)壓縮系統(tǒng)可以實(shí)現(xiàn)對(duì)視頻圖像的壓縮編碼。壓縮后的視頻流比較流暢。

從通過邏輯分析儀測(cè)得的時(shí)序圖(圖2.8、圖2.9)可以看出,CPLD 實(shí)現(xiàn)的FIFO 控制信號(hào)滿足視頻AL422B的時(shí)序要求,整個(gè)視頻數(shù)據(jù)傳輸?shù)耐饭ぷ髡#旧线_(dá)到了系統(tǒng)設(shè)計(jì)的指標(biāo)和要求。同時(shí)這種方案可以作為一個(gè)整體的視頻采集模塊,在一般的使用DSP 的EMIF 總線的情況下的都可以無需改動(dòng)就可以作為一個(gè)采集模塊直接使用,大大簡(jiǎn)化硬件電路開發(fā)的難度。此方案已經(jīng)在基于DSP 的視頻PCI 采集壓縮卡中得到了驗(yàn)證,達(dá)到了很好的效果。本文的基于CPLD的視頻采集通用模塊已經(jīng)在M-JPEG2000的視頻采集壓縮卡得到了應(yīng)用。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348759 -

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423157 -

cpld

+關(guān)注

關(guān)注

32文章

1248瀏覽量

169334

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

采用CPLD技術(shù)實(shí)現(xiàn)有多種觸發(fā)方式的120MHz高速A/D采集卡設(shè)計(jì)

請(qǐng)教CPLD下載

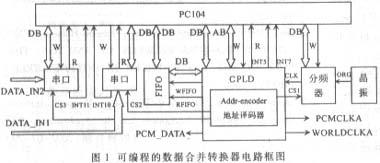

如何利用EPM7128設(shè)計(jì)數(shù)據(jù)合并轉(zhuǎn)換器?

如何采用CPLD技術(shù)來實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)?

基于DSP和CPLD的液晶模塊的設(shè)計(jì)

EPM7128S在雷達(dá)電子干擾模擬訓(xùn)練器中的應(yīng)用

基于EPM7128SLC84實(shí)現(xiàn)的AD574A采樣控制器

基于 CPLD EPM570T100C5的通用直流調(diào)速模塊設(shè)

EPM7128在光柵位移測(cè)量?jī)x中的應(yīng)用

TMS320LF2407型DSP和EPM7128型CPLD在移動(dòng)

基于CPLD控制的通用視頻采集模塊詳述

數(shù)據(jù)合并轉(zhuǎn)換器電路的工作原理分析及如何采用EPM7128芯片實(shí)現(xiàn)

基于CPLD芯片EPM7128STC100實(shí)現(xiàn)視頻采集通用模塊的設(shè)計(jì)

基于CPLD芯片EPM7128STC100實(shí)現(xiàn)視頻采集通用模塊的設(shè)計(jì)

評(píng)論